SNLS508 September 2015 LMH0318

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Description continued

- 6 Pin Configuration and Functions

- 7 Specifications

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3

Feature Description

- 8.3.1 Loss of Signal Detector

- 8.3.2 Continuous Time Linear Equalizer (CTLE)

- 8.3.3 2:1 Multiplexer

- 8.3.4 Clock and Data Recovery

- 8.3.5 Eye Opening Monitor (EOM)

- 8.3.6 Fast EOM

- 8.3.7 LMH0318 Device Configuration

- 8.3.8 Power-On Reset

- 8.4 Device Functional Modes

- 8.5 Programming

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

- RTW|24

サーマルパッド・メカニカル・データ

- RTW|24

発注情報

8 Detailed Description

8.1 Overview

The LMH0318 is a 2.97Gbps/1.485Gbps/0.27Gbps multi-rate serial digital video data reclocker with integrated cable driver intended for equalizing, reclocking, and driving data compatible to the SMPTE standards. It is a 2-input, 2-output single-core chip, enabling 1:2 fan-out or 2:1 MUX operations. Each input has a 100 Ω continuous time linear equalizer (CTLE) at the front-end, intended to compensate for loss over STP coax or FR-4 PCB trace. The LMH0318 OUT0 is a 75 Ω cable driver compatible to the SMPTE requirements.

The referenceless Clock-and-Data Recovery (CDR) circuit selects between the two inputs based on user choice. The reclocked output can be driven to one or two outputs. One of the outputs supports 100-Ω differential cable connection, while the other output can drive a 75 Ω SMPTE specified cable while meeting transmitter requirements as specified in SMPTE standard. The LMH0318 locks to all required SDI data rates, including 270Mbps, 1.485 Gbps, 1.4835 Gbps, 2.97 Gbps, and 2.967 Gbps. The LMH0318 is assembled in a 4 mm × 4 mm 24-pin QFN package. The chip can be programmed using SPI or SMBus interface.

8.2 Functional Block Diagram

8.3 Feature Description

The LMH0318 data path consists of several key blocks as shown in the Functional Block Diagram. These key circuits are:

- Loss of Signal Detector

- Continuous Time Linear Equalizer (CTLE) for FR4 Compensation

- 2:1 Multiplexer/1:2 Fanout

- CDR

- Eye Monitor

- Differential Output Selection

- 75 Ω and 100 Ω Output Drivers

- SMBus/SPI Configuration

8.3.1 Loss of Signal Detector

The LMH0318 supports two high speed differential input ports, with internal 100 Ω terminations. The inputs must be AC coupled. The external AC coupling capacitor value should take into account the pathological low frequency content. For most applications, the RC time constant of 4.7 µF AC coupling capacitor plus the 50 Ω termination resistor is capable of handing the pathological video pattern's low frequency content.

The signal detect circuit is designed to assert when data traffic with a certain minimum amplitude is present at the input of the device. It is also designed to de-assert, or remain de-asserted, when there is noise below certain amplitude at the input to the device.

The LMH0318 has two signal detect circuits, one for each input. Each signal detect threshold can be set independently. By default, both signal detects are powered on. The user selects IN1 or IN0 through SMBus/SPI interface.

8.3.2 Continuous Time Linear Equalizer (CTLE)

The LMH0318 has receive-side equalization, and a key part is the Continuous Time Linear Equalizer (CTLE). This circuit operates on the received differential signal and compensates for frequency-dependent loss due to the transmission media. The CTLE applies gain to the input signal. This gain varies over frequency: higher frequencies are boosted more than lower frequencies. The CTLE works to restore the input signal to full amplitude across a wide range of frequencies.

The CTLE consists of 4 stages with each stage having two boost control bits. This allows 256 different boost settings. CTLE boost levels are determined by summing the boost levels of the 4 stages. The CTLE is configured manually. See LMH0318 Programming Guide (SNLU183) on how to quickly select the most appropriate CTLE boost setting.

There are two CTLEs, one for each input, IN0 and IN1. Only one CTLE is enabled at a time, according to the user input channel selection. If IN0 is selected, the CTLE for IN0 is powered on and the IN1 CTLE is powered off. The CTLE is able to handle low loss channels without over-equalizing by bypassing the CTLE.

8.3.3 2:1 Multiplexer

A 2:1 input multiplexor connects IN0 and IN1 to the CDR. By default, IN0 is selected. To select IN1, the 2:1 multiplexer must be set. See LMH0318 Programming Guide (SNLU183) for detailed settings.

8.3.4 Clock and Data Recovery

By default, the equalized data is fed into the CDR for clock and data recovery. The CDR consists of a reference-less Phase Frequency Detector (PFD), Charge Pump (CP), Voltage Controlled Oscillator (VCO), and Output Data Multiplexer (Mux).

The inputs to the Phase and Frequency Detector (PFD) are the data after the CTLE as well as I and Q clocks from the VCO. The LMH0318 will attempt to lock to the incoming data by tuning the VCO to phase-lock to the incoming data rate.

The supported data rates are listed in the following table. See LMH0318 Programming Guide (SNLU183) for further information on configuring the LMH0318 for different data rates.

Table 1. Supported Data Rates

| DATA RATE RANGE | CDR MODE | COMMENT |

|---|---|---|

| 2.97 Gbps, 2.967 Gbps | Enabled | |

| 1.485 Gbps, 1.4835 Gbps | Enabled | |

| 270 Mbps | Enabled | |

| 125 Mbps | Disabled | At 125 Mbps device is in CDR bypass |

8.3.5 Eye Opening Monitor (EOM)

The LMH0318 has an on-chip eye opening monitor (EOM) which can be used to analyze, monitor, and diagnose the performance of the link. The EOM operates on the post-equalized waveform, just prior to the data sampler. Therefore, it captures the effects of all the equalization circuits within the receiver before the data is reclocked. The EOM is operational for 1.485 Gbps and higher data rates.

The EOM monitors the post-equalized waveform in a time window that spans one unit interval and a configurable voltage range that spans up to ±400 mV differential. The time window and voltage range are divided into 64 steps, so the result of the eye capture is a 64 × 64 matrix of “hits,” where each point represents a specific voltage and phase offset relative to the main data sampler. The number of “hits” registered at each point needs to be taken in context with the total number of bits observed at that voltage and phase offset in order to determine the corresponding probability for that point. The number of bits observed at each point is configurable.

A common measurement performed by the EOM is the horizontal and vertical eye opening. The horizontal eye opening (HEO) represents the width of the post-equalized eye at 0 V differential amplitude, measured in unit intervals or picoseconds. The vertical eye opening (VEO) represents the height of the post-equalized eye, measured midway between the mean zero crossing of the eye. This position in time approximates the CDR sampling phase.

The resulting 64 × 64 matrix produced by the EOM can be processed by software and visualized in a number of ways. Two common ways to visualize this data are shown in Figure 20 and Figure 21. These diagrams depict examples of an eye monitor plot implemented by software. The first plot is an example of using the EOM data to plot a basic eye using ASCII characters, which can be useful for simple diagnostics software. The second plot shows the first derivative of the EOM data, revealing the density of hits and the actual waveforms and crossing that comprise the eye.

8.3.6 Fast EOM

Fast EOM is a mechanism that provides an option to read out EOM through SPI/SMBus interfaces by reading the hits observed for each point of 64 × 64 points matrix. Since SPI interface operates at faster clock rate than SMBus interface, the SPI master will have to wait until the EOM start bit, reg 0x24[0], goes low. This indicates EOM samples are available and the SPI master can proceed to read register 0x25 and 0x26. See SPI Fast EOM Operation and LMH0318 Programming Guide (SNLU183) for further details of Fast EOM operation.

8.3.6.1 SMBus Fast EOM Operation

In SMBus mode, the read on register 0x26 acts as an automatic trigger to read the next EOM count value:

- Enable EOM (power it on), and set VRANGE=0. Write reg 0x24[7] to 1 to turn on fast EOM

- Read register 0x25 as burst of 2 bytes (EOM hit count) and discard

- Read register 0x25 as burst of 2 bytes (EOM hit count) and discard

- Read register 0x25 as burst of 2 bytes (EOM hit count) and save

- Perform Step 4 4095 times (64 × 64 cells)

8.3.6.2 SPI Fast EOM Operation

To perform EOM calculation over SPI:

- Enable EOM (power it on), and set VRANGE=0. Write reg 0x24[7] to 1 to turn on fast EOM

- Read reg 0x26 to initialize. Discard read data

- Read Reg 0x24[0] which is EOM start bit. Wait for this bit to go low

- Read register 0x26 EOM hit count and discard. Read on register 0x26 will automatically trigger the next Fast Eye calculation

- Read Reg 0x24[0]. Wait for this bit to go low

- Do burst read on register 0x25 and 0x26 to get the EOM hit count value.

- Repeat Steps 5 and 6 4095 times (64 × 64 cells)

8.3.7 LMH0318 Device Configuration

The control pins can be used to configure different operations depending on the functional modes as described in Table 2.

Table 2. Control Pins

| FUNCTIONAL MODES | |||

|---|---|---|---|

| PIN # | PIN NAME | SPI | SMBus_Slave |

| 1 | MODE_SEL | 1 kΩ to VDD | 1 kΩ to GND |

| 2 | IN_OUT_SEL_SPI_SS_N_ADDR0 | SPI_SS_N | ADDR0 |

| 3 | EQ_SCL_SCK | SPI_SCK | SMBUS_SCL |

| 4 | OUT_CTRL_MOSI_SDA | SPI_MOSI | SMBUS SDA |

| 6 | ENABLE | ENABLE | ENABLE |

| 13 | LOS_INT_N | LOS_INT_N | LOS_INT_N |

| 15 | VOD_MISO_ADDR1 | SPI_MISO | ADDR1 |

| 16 | LOCK | LOCK | LOCK |

8.3.7.1 MODE_SEL

This pin can be configured in 4 possible ways:

- 1 kΩ to VDD: This puts the part in SPI mode

- Float (Default): Reserved

- 20 kΩ to GND: Reserved

- 1 kΩ to GND: This puts the part in SMBus mode

8.3.7.2 ENABLE

Normal operation when ENABLE is pulled high, and powers down the device when pulled low.

Table 3. ENABLE Selection

| ENABLE | POWER CONDITION |

|---|---|

| 1 kΩ to GND | Power down device (signal detectors powered down, registers at reset state) |

| 20 kΩ to GND | Reserved |

| Float | Reserved |

| 1 kΩ to VDD | Normal Operation |

8.3.7.3 LOS_INT_N

LOS_INT_N pin is an open drain output. When the channel that has been selected cannot detect a signal at the high-speed input pins (as defined by the assert levels), the pin pulls low. Pin 13 can be configured through share register 0xFF[5] for interrupt functionality.

In SMBus/SPI mode, this pin can be configured as an interrupt. This pin is asserted low when there is an interrupt and goes back high when the interrupt status register is read. There are 7 separate masks for different interrupt sources. These interrupt sources are:

- If there is a LOS transition on IN0, irrespective of the input channel selected (2 separate masks).

- If there is a LOS transition on IN1, irrespective of the input channel selected (2 separate masks).

- HEO or VEO goes below a certain threshold as specified in the registers (1 mask).

- Lock transition, whether it is asserted or de-asserted – disabled by default (2 mask).

8.3.7.4 LOCK

Indicates the lock status of the CDR. When CDR is locked this pin is asserted high.

8.3.7.5 SMBus MODE

The SMBus interface can also be used to control the device. If pin 1 (MODE_SEL) is pulled low through 1 kΩ to GND, then Pins 3, 4 are configured as the SMBUS_SCL and SMBUS_SDA respectively. Pins 2, 15 are address straps, ADDR0/ADDR1 respectively, during power up.

The maximum operating speed supported on the SMBus pins is 400 kHz.

Table 4. SMBus MODE

| ADDR0 | ADDR1 | ADDR0 [BINARY] | ADDR1 [BINARY] | 7-Bit SLAVE ADDRESS [HEX] |

8-Bit WRITE COMMAND [HEX] |

|---|---|---|---|---|---|

| 1 kΩ to GND | 1 kΩ to GND | 00 | 00 | 0D | 1A |

| 1 kΩ to GND | 20 kΩ to GND | 00 | 01 | 0E | 1C |

| 1 kΩ to GND | Float | 00 | 10 | 0F | 1E |

| 1 kΩ to GND | 1 kΩ to VDD | 00 | 11 | 10 | 20 |

| 20 kΩ to GND | 1 kΩ to GND | 01 | 00 | 11 | 22 |

| 20 kΩ to GND | 20 kΩ to GND | 01 | 01 | 12 | 24 |

| 20 kΩ to GND | Float | 01 | 10 | 13 | 26 |

| 20 kΩ to GND | 1 kΩ to VDD | 01 | 11 | 14 | 28 |

| Float | 1 kΩ to GND | 10 | 00 | 15 | 2A |

| Float | 20 kΩ to GND | 10 | 01 | 16 | 2C |

| Float | Float | 10 | 10 | 17 | 2E |

| Float | 1 kΩ to VDD | 10 | 11 | 18 | 30 |

| 1 kΩ to VDD | 1 kΩ to GND | 11 | 00 | 19 | 32 |

| 1 kΩ to VDD | 20 kΩ to GND | 11 | 01 | 1A | 34 |

| 1 kΩ to VDD | Float | 11 | 10 | 1B | 36 |

| 1 kΩ to VDD | 1 kΩ to VDD | 11 | 11 | 1C | 38 |

Note: These are 7 bit addresses. Therefore, the LSB must be added to indicate read/write. LSB equal to zero indicates write and 1 indicates SMBus read operation. For example, for 7 bit hex address 0x0D, the I2C hex address byte is 0x1A to write and 0X1B to read.

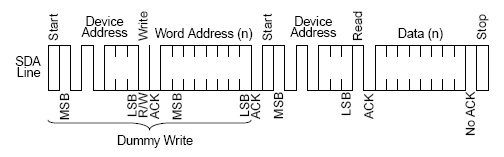

8.3.7.6 SMBus READ/WRITE Transaction

The System Management Bus (SMBus) is a two-wire serial interface through which various system component chips can communicate with the master. Slave devices are identified by having a unique device address. The two-wire serial interface consists of SCL and SDA signals. SCL is a clock output from the Master to all of the Slave devices on the bus. SDA is a bidirectional data signal between the Master and Slave devices. The LMH0318 SMBUS SCL and SDA signals are open drain and require external pull up resistors.

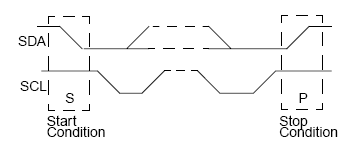

Start and Stop:

The Master generates Start and Stop conditions at the beginning and end of each transaction.

- Start: High to low transition (falling edge) of SDA while SCL is high

- Stop: Low to high transition (rising edge) of SDA while SCL is high

Figure 3. Start and Stop Conditions

Figure 3. Start and Stop Conditions

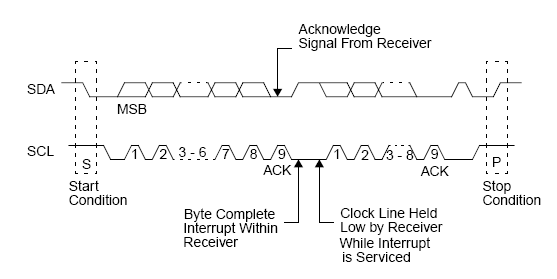

The Master generates 9 clock pulses for each byte transfer. The 9th clock pulse constitutes the ACK cycle. The transmitter releases SDA to allow the receiver to send the ACK signal. An ACK is when the device pulls SDA low, while a NACK is recorded if the line remains high.

Figure 4. Acknowledge (ACK)

Figure 4. Acknowledge (ACK)

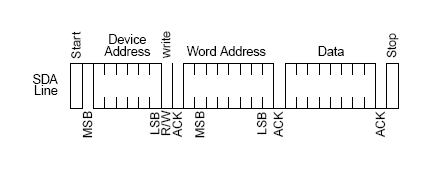

Writing data from a master to a slave comprises of 3 parts as noted in figure Figure 5

- The master begins with start condition followed by the slave device address with the R/W bit cleared

- The 8-bit register address that will be written

- The data byte to write

SMBus read operation consists of four parts

- The master initiates the read cycle with start condition followed by slave device address with the R/W bit cleared

- The 8-bit register address that is to be read

- After acknowledgment from the slave, the master initiates a re-start condition

- The slave device address is resent followed with R/W bit set

- After acknowledgment from the slave, the data is read back from the slave to the master. The last ACK is high if there are no more bytes to read

Figure 6. SMBus Read Operation

Figure 6. SMBus Read Operation

Figure 7. SMBus Timing Parameters

Figure 7. SMBus Timing Parameters

8.3.7.7 SPI Mode

The SPI (Serial Peripheral Interface) bus standard can be used to control the device. The SPI Mode is enabled when MODE_SEL Pin 1 is pulled high through the 1-kΩ resistor. The SPI bus comprises of 4 pins: Pin 2, Pin 3, Pin 4, and Pin 15:

- MOSI Pin 4: Master Output Slave Input. Configured as toggling input.

- MISO Pin 15: Master Input, Slave Output: Configured as a toggling output

- SS_N Pin 2: Slave Select (active low). Configured as toggling input.

- SCK Pin 3: Serial clock (output from master). Configured as toggling input.

The maximum operating speed supported on the SPI bus is 20 MHz.

8.3.7.7.1 SPI READ/WRITE Transaction

Each SPI transaction to a single device is 17 bits long and is framed by SS_N asserted low. The MOSI input is ignored and the MISO output is floated whenever SS_N is de-asserted (High).

The bits are shifted in left-to-right. The first bit is R/W, so it is 1 for reads and 0 for writes. Bits A7-A0 are the 8-bit register address, and bits D7-D0 are the 8-bit read or write data. The prior SPI command, address, and data are shifted out on MISO as the current command, address, and data are shifted in on MOSI. In all SPI transactions, the MISO output signal is enabled asynchronously when SS_N becomes asserted.

| R/W | A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

8.3.7.7.2 SPI Write Transaction Format

For SPI writes, the R/W bit is 0. SPI write transactions are 17 bits per device, and the command is executed on the rising edge of SS_N, as shown in Figure 9. The SPI transaction always starts on the rising edge of the clock.

| 0 | A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

The signal timing for a SPI Write transaction is shown in Figure 10. The “prime” values on MISO (for example, A7‟) reflect the contents of the shift register from the previous SPI transaction, and are a "don’t-care" for the current transaction.

Figure 10. Signal Timing for a SPI Write Transaction

Figure 10. Signal Timing for a SPI Write Transaction

8.3.7.7.3 SPI Read Transaction Format

An SPI read transaction is 34 bits per device consisting of two 17-bit frames. The first 17-bit read transaction, first frame, shifts in the address to be read, followed by a dummy transaction, second frame, to shift out the 17-bit read data. The R/W bit is 1 for the read transaction, as shown in Figure 11.

The first 17 bits from the read transaction specifies 1-bit of RW and 8-bits of address A7-A0. The eight 1’s following the address are ignored. The second dummy transaction acts like a read operation on address 0xFF and needs to be ignored. However, the transaction is necessary in order to shift out the read data D7-D0 in the last 8 bits of the MISO output.

The signal timing for a SPI read transaction is shown in Figure 11. As with the SPI write, the “prime” values on MISO during the first 16 clocks are a don’t-care for this portion of the transaction. Note, that the values shifted out on MISO during the last 17 clocks reflect the read address and 8-bit read data for the current transaction.

Figure 11. Signal Timing for a SPI Read Transaction

Figure 11. Signal Timing for a SPI Read Transaction

8.3.7.8 SPI Daisy Chain

The LMH0318 includes an enhanced SPI controller that supports daisy-chaining the serial configuration data among multiple LMH0318 devices. The LMH0318 device supports SPI Daisy Chain between devices with an 8-bit SPI addressing scheme. Each LMH0318 device is directly connected to the SCK and SS_N pins of the Host. However, only the first LMH0318 device in the chain is connected to the Host’s MOSI pin, and only the last device in the chain is connected to the Host’s MISO pin. The MOSI pin of each intermediate LMH0318 device in the chain is connected to the MISO pin of the previous LMH0318 device, thereby creating a serial shift register. This architecture is shown in Figure 12.

Figure 12. Daisy-Chain Configuration

Figure 12. Daisy-Chain Configuration

In a daisy-chain configuration of N LMH0318 devices, the Host conceptually sees a long shift register of length 17xN. Therefore the length of a Basic SPI Transaction, as described above, is 17xN; in other words, SS_N is asserted for 17xN clock cycles.

8.3.7.8.1 SPI Daisy Chain Write Example

The following example make some assumptions:

The daisy-chain is 3 LMH0318 devices long, comprising Devices 1, 2, and 3 as shown in Figure 12. Therefore, each Basic SPI Transaction is 17x3 = 51 clocks long.

In Figure 13, the following occurs at the end of the transaction:

- Write 0x5A to register 0x12 in Device 3

- Write 0x3C to register 0x34 in Device 2

- Write 0x00 to register 0x56 in Device 1

Note that the bits are shifted out of MOSI left to right. The MISO pin is not shown as it reflects shift register contents from a prior transaction.

Figure 13. MOSI Write Example

Figure 13. MOSI Write Example

8.3.7.8.2 SPI Daisy Chain Write Read Example

In Figure 14 and Figure 15, the following occurs at the end of the first transaction:

- Write 0x22 to register 0x01 in Device 3

- Latch the data from register 0x34 in Device 2

- Write 0x44 to register 0x76 in Device 1

Figure 14. SPI Daisy Chain Write Read First Frame Illustration

Figure 14. SPI Daisy Chain Write Read First Frame Illustration

Figure 15. SPI Daisy Chain Write Read second Frame Illustration

Figure 15. SPI Daisy Chain Write Read second Frame Illustration

8.3.7.8.2.1 SPI Daisy Chain Length of Daisy Chain Illustration

A useful operation for the Host may be to detect the length of the daisy-chain. This is a simple matter of shifting in a series of known data values (0x7F, 0xAA) in the example in Figure 16. After N+1 writes, the known data value will begin to appear on the Host's MISO pin.

Figure 16. MOSI (Host)

Figure 16. MOSI (Host)

8.3.8 Power-On Reset

The LMH0318 has an internal power-on reset (PoR) circuitry which initiates a self-clearing reset after the power is applied to the VDD pins.

8.4 Device Functional Modes

The LMH0318 features can be programmed via SPI, or SMBus interface. LMH0318 Device Configuration describes detailed operation using SPI, or SMBus interface.

8.5 Programming

For more information on device programming, See LMH0318 Programming Guide (SNLU183). Register initialization is required at power-up or after reset. See Initialization Set Up

8.5.1 Register Maps

The LMH0318 register set definition is organized into four groups:

- Global Registers: Chip ID, Interrupt status, LOS registers

- Receiver Registers: Equalizer boost settings and signal detect setting

- CDR Registers: PLL control

- Transmitter Registers: OUT0 and OUT1 parameter setting

The typical device initialization sequence for the LMH0318 includes the followings. For detailed register settings See LMH0318 Programming Guide (SNLU183).

- Shared Register Configuration

- Reading device ID

- Selecting interrupt on to LOS pin

- Settings up the register to access the channel registers

- Channel Register Configuration

- CDR Reset

- Interrupt register configuration

- Optional Input/Output selection

- Optional VOD selection

- CDR Reset and Release

8.5.2 Global Registers

Table 5. Global Registers

| REGISTER NAME | BITS | FIELD REGISTER ADDRESS | DEFAULT | R/RW | DESCRIPTION |

|---|---|---|---|---|---|

| SMBus Observation | Reg_0x00 Share | 0x00 | SMBus Address Observation | ||

| 7 | SMBUS_addr3 | 0 | R | SMBus strap observation | |

| 6 | SMBUS_addr2 | 0 | R | ||

| 5 | SMBUS_addr1 | 0 | R | ||

| 4 | SMBUS_addr0 | 0 | R | ||

| 3 | Reserved | 0 | RW | ||

| 2 | Reserved | 0 | RW | ||

| 1 | Reserved | 0 | RW | ||

| 0 | Reserved | 0 | RW | ||

| Reset Shared Regs | Reg 0x04 Share | 0x01 | Shared Register Reset | ||

| 7 | Reserved | 0 | RW | ||

| 6 | rst_i2c_regs | 0 | RW | 1: Reset Shared Registers 0: Normal operation |

|

| 5 | Reserved | 0 | RW | ||

| 4 | Reserved | 0 | RW | ||

| 3 | Reserved | 0 | RW | ||

| 2 | Reserved | 0 | RW | ||

| 1 | Reserved | 0 | RW | ||

| 0 | Reserved | 1 | RW | ||

| Enable SMBus Strap | Reg 0x06 Share | 0x00 | Allow SMBus strap observation | ||

| 7 | Reserved | 0 | RW | ||

| 6 | Reserved | 0 | RW | ||

| 5 | Reserved | 0 | RW | ||

| 4 | Reserved | 0 | RW | ||

| 3 | Test control[3] | 0 | RW | Set to >9 to allow strap observation on share reg 0x00 | |

| 2 | Test control[2] | 0 | RW | ||

| 1 | Test control[1] | 0 | RW | ||

| 0 | Test control[0] | 0 | RW | ||

| Device Version | Reg 0xF0 Share | 0x01 | Device Version | ||

| 7 | VERSION[7] | 0 | RW | Device revision | |

| 6 | VERSION[6] | 0 | RW | ||

| 5 | VERSION[5] | 0 | RW | ||

| 4 | VERSION[4] | 0 | RW | ||

| 3 | VERSION[3] | 0 | RW | ||

| 2 | VERSION[2] | 0 | RW | ||

| 1 | VERSION[1] | 0 | RW | ||

| 0 | VERSION[0] | 1 | RW | ||

| Channel Control | Reg 0xFF Control | 0x00 | Enable Channel Control | ||

| 7 | Reserved | 0 | RW | ||

| 6 | Reserved | 0 | RW | ||

| 5 | los_int_bus_sel | 0 | RW | 1: Selects interrupt onto LOS pin 0: Selects signal detect onto LOS pin |

|

| 4 | Reserved | 0 | RW | ||

| 3 | Reserved | 0 | RW | ||

| 2 | en_ch_Access | 0 | RW | 1: Enables access to channel registers 0: Enables access to share registers |

|

| 1 | Reserved | 0 | RW | ||

| 0 | Reserved | 0 | RW | ||

| Reset_Channel_Regs | Reg_0x00 Channel | 0x00 | Reset all Channel Registers to Default Values | ||

| 7 | Reserved | 0 | |||

| 6 | Reserved | 0 | |||

| 5 | Reserved | 0 | |||

| 4 | Reserved | 0 | |||

| 3 | Reserved | 0 | |||

| 2 | Rst_regs | 0 | 1: Reset Channel Registers ( self clearing ) 0: Normal operation |

||

| 1 | Reserved | 0 | |||

| 0 | Reserved | 0 | |||

| LOS_status | Reg_0x01 Channel | 0x00 | Signal Detect Status | ||

| 7 | Reserved | 0 | RW | ||

| 6 | Reserved | 0 | RW | ||

| 5 | Reserved | 0 | RW | ||

| 4 | Reserved | 0 | RW | ||

| 3 | Reserved | 0 | RW | ||

| 2 | Reserved | 0 | RW | ||

| 1 | LOS1 | 0 | R | 1: Loss of signal on IN1 0: Signal present on IN1 |

|

| 0 | LOS0 | 0 | R | 1: Loss of signal on IN0 0: Signal present on IN0 |

|

| CDR_Status_1 | Reg_0x02 Channel | 0x00 | CDR Status | ||

| 7 | Reserved | 0 | R | ||

| 6 | Reserved | 0 | R | ||

| 5 | Reserved | 0 | R | ||

| 4 | cdr_status[4] | 0 | R | 11: CDR locked 00: CDR not locked |

|

| 3 | cdr_status[3] | 0 | R | ||

| 2 | Reserved | 0 | R | ||

| 1 | Reserved | 0 | R | ||

| 0 | Reserved | 0 | R | ||

| Interrupt Status Register | Reg 0x54 Channel | 0x00 | Interrupt Status ( clears upon read ) | ||

| 7 | Sigdet | 0 | R | 1: Signal Detect from the selected input asserted 0: Signal Detect from the selected input de-asserted |

|

| 6 | cdr_lock_int | 0 | R | 1: CDR Lock interrupt 0: No interrupt from CDR Lock |

|

| 5 | signal_det1_int | 0 | R | 1: IN1 Signal Detect interrupt 0: No interrupt from IN1 Signal Detect |

|

| 4 | signal_det0_int | 0 | R | 1: IN0 Signal Detect interrupt 0: No interrupt from IN0 Signal Detect |

|

| 3 | heo_veo_int | 0 | R | 1: HEO_VEO Threshold reached interrupt 0: No interrupt from HEO_VEO |

|

| 2 | cdr_lock_loss_int | 0 | R | 1: CDR loss of lock interrupt 0: No interrupt from CDR lock |

|

| 1 | signal_det1_loss_int | 0 | R | 1: IN1 Signal Detect loss interrupt 0: No interrupt from IN1 Signal Detect |

|

| 0 | signal_det0_loss_int | 0 | R | 1: IN0 Signal Detect loss interrupt 0: No interrupt from IN0 Signal Detect |

|

| Interrupt Control | Reg 0x56 Channel | 0x00 | Interrupt Mask | ||

| 7 | Reserved | 0 | RW | ||

| 6 | cdr_lock_int_en | 0 | RW | 1: Enable Interrupt if CDR lock is achieved 0: Disable interrupt if CDR lock is achieved |

|

| 5 | signal_det1_int_en | 0 | RW | 1: Enable interrupt if IN1 Signal Detect is asserted 0: Disable interrupt if IN1 Signal Detect is asserted |

|

| 4 | signal_det0_int_en | 0 | RW | 1: Enable interrupt if IN0 Signal Detect is asserted 0: Disable interrupt if IN0 Signal Detect is asserted |

|

| 3 | heo_veo_int_en | 0 | RW | 1: Enable interrupt if HEO-VEO threshold is reached 0: Disable interrupt due to HEO-VEO threshold |

|

| 2 | cdr_lock_loss_int_en | 0 | RW | 1: Enable interrupt if CDR loses lock 0: Disable interrupt if CDR loses lock |

|

| 1 | signal_det1_loss_int_en | 0 | RW | 1: Enable interrupt if there is loss of signal on IN1 0: Disable interrupt if there is loss of signal on IN1 |

|

| 0 | signal_det0_loss_int_en | 0 | RW | 1: Enable interrupt if there is loss of signal on IN0 0: Disable interrupt if there is loss of signal on IN0 |

8.5.3 Receiver Registers

Table 6. Receiver Registers

| REGISTER NAME | BITS | FIELD REGISTER ADDRESS | DEFAULT | R/RW | DESCRIPTION |

|---|---|---|---|---|---|

| EQ_Boost | Reg 0x03 Channel | 0x80 | 4 Stage EQ Boost Levels. Read-back value going to CTLE in reg_0x52. Used for setting EQ value when reg_0x2D[3] is high | ||

| 7 | eq_BST0[1] | 1 | RW | 2 Bits control for stage 0 of the CTLE. Adapts during CTLE adaptation | |

| 6 | eq_BST0[0] | 0 | RW | ||

| 5 | eq_BST1[1] | 0 | RW | 2 Bits control for stage 1 of the CTLE. Adapts during CTLE adaptation | |

| 4 | eq_BST1[0] | 0 | RW | ||

| 3 | eq_BST2[1] | 0 | RW | 2 Bits control for stage 2 of the CTLE. Adapts during CTLE adaptation | |

| 2 | eq_BST2[0] | 0 | RW | ||

| 1 | eq_BST3[1] | 0 | RW | 2 Bits control for stage 3 of the CTLE. Adapts during CTLE adaptation | |

| 0 | eq_BST3[0] | 0 | RW | ||

| SD_EQ | Reg_0x0D Channel | 0x00 | 270 Mbps EQ Boost Setting | ||

| 7 | Reserved | 0 | RW | ||

| 6 | Reserved | 0 | RW | ||

| 5 | Reserved | 0 | RW | ||

| 4 | Reserved | 0 | RW | ||

| 3 | Reserved | 0 | RW | ||

| 2 | Reserved | 0 | RW | ||

| 1 | Reserved | 0 | RW | ||

| 0 | Mr_auto_eq_en_bypass | 0 | RW | 1: EQ Bypass for 270 Mbps 0: Use EQ Settings in reg0x03[7:0] for 270 Mbps Note: If 0x13[1] mr_eq_en_bypass is set, bypass would be set and auto-bypass has no significance. |

|

| EQ_SD_CONFIG | Reg 0x13 Channel | 0x90 | Channel EQ Bypass and Power Down | ||

| 7 | Reserved | 1 | RW | ||

| 6 | sd_0_PD | 0 | RW | 1: Power Down IN0 Signal Detect 0: IN0 Signal Detect normal operation |

|

| 5 | sd_1_PD | 0 | RW | 1: Power Down IN1 Signal Detect 0: IN1 Signal Detect normal operation |

|

| 4 | Reserved | 1 | RW | ||

| 3 | eq_PD_EQ | 0 | RW | Controls the power-state of the selected channel. The un-selected channel is always powered-down 1: Powers down selected channel EQ stage 0: Powers up EQ of the selected channel |

|

| 2 | Reserved | 0 | RW | ||

| 1 | eq_en_bypass | 0 | RW | 1: Bypass stage 3 and 4 of CTLE 0: Enable Stage 3 and 4 of CTLE |

|

| 0 | Reserved | 0 | RW | ||

| SD0_CONFIG | Reg 0x14 Channel | 0x00 | IN0 Signal Detect Threshold Setting | ||

| 7 | Reserved | 0 | RW | ||

| 6 | Reserved | 0 | RW | ||

| 5 | sd_0_refa_sel[1] | 0 | RW | Controls signal detect SDH- Assert [5:4], SDL- De-Assert [3:2], thresholds for IN0 0000: Default levels (nominal) 0101: Nominal -2 mV 1010: Nominal +5 mV 1111: Nominal +3 mV |

|

| 4 | sd_0_refa_sel[0] | 0 | RW | ||

| 3 | sd_0_refd_sel[1] | 0 | RW | ||

| 2 | sd_0_refd_sel[0] | 0 | RW | ||

| 1 | Reserved | 0 | RW | ||

| 0 | Reserved | 0 | RW | ||

| SD1_CONFIG | Reg_0x15 Channel | 0x00 | IN1 Signal Detect Threshold Setting | ||

| 7 | Reserved | 0 | RW | ||

| 6 | Reserved | 0 | RW | ||

| 5 | sd_1_refa_sel[1] | 0 | RW | Controls signal detect SDH- Assert [5:4], SDL- De-Assert [3:2], thresholds for IN1 0000: Default levels (nominal) 0101: Nominal -2 mV 1010: Nominal +5 mV 1111: Nominal +3 mV |

|

| 4 | sd_1_refa_sel[0] | 0 | RW | ||

| 3 | sd_1_refd_sel[1] | 0 | RW | ||

| 2 | sd_1_refd_sel[0] | 0 | RW | ||

| 1 | Reserved | 0 | RW | ||

| 0 | Reserved | 0 | RW | ||

| EQ_BOOST_OV | Reg_0x2D Channel | 0x88 | EQ Boost Override | ||

| 7 | Reserved | 1 | RW | ||

| 6 | Reserved | 0 | RW | ||

| 5 | Reserved | 0 | RW | ||

| 4 | Reserved | 0 | RW | ||

| 3 | reg_eq_bst_ov | 1 | RW | 1: Enable EQ boost over ride See LMH0318 Programming Guide (SNLU183) 0: Disable EQ boost over ride |

|

| 2 | Reserved | 0 | RW | ||

| 1 | Reserved | 0 | RW | ||

| 0 | Reserved | 0 | RW | ||

| CTLE Setting | Reg_0x31 Channel | 0x00 | CTLE Mode of Operation and Input/Output Mux Selection | ||

| 7 | Reserved | 0 | RW | ||

| 6 | adapt_mode[1] | 00 | RW | 00: Normal Operation - Manual CTLE Setting 01: Test Mode - See the LMH0318 Programming Guide (SNLU183) for details Other Settings - Invalid |

|

| 5 | adapt_mode[0] | ||||

| 4 | Reserved | 0 | RW | ||

| 3 | Reserved | 0 | RW | ||

| 2 | Reserved | 0 | RW | ||

| 1 | input_mux_ch_sel[1] | 0 | RW | IN0/1 and OUT0/1 selection 00: selects IN0 and OUT0/1 01: selects IN0 and OUT0 10: selects IN1 and OUT1 11: selects IN1 and OUT0/1 |

|

| 0 | input_mux_ch_sel[0] | 0 | RW | ||

| LOW_RATE_ EQ_BST |

Reg 0x3A Channel | 0x00 | HD and SD EQ Level | ||

| 7 | fixed_eq_BST0[1] | 0 | RW | When CTLE is operating in test mode, Reg 0x3A[7:0] forces fixed EQ setting. In normal operating manual mode Reg_0x03 forces EQ boost. See LMH0318 Programming Guide (SNLU183) for details | |

| 6 | fixed_eq_BST0[0] | 0 | RW | ||

| 5 | fixed_eq_BST1[1] | 0 | RW | ||

| 4 | fixed_eq_BST1[0] | 0 | RW | ||

| 3 | fixed_eq_BST2[1] | 0 | RW | ||

| 2 | fixed_eq_BST2[0] | 0 | RW | ||

| 1 | fixed_eq_BST3[1] | 0 | RW | ||

| 0 | fixed_eq_BST3[0] | 0 | RW | ||

| BST_Indx0 | Reg_0x40 Channel | 0x00 | Index0 4 Stage EQ Boost. See LMH0318 Programming Guide (SNLU183) | ||

| 7 | I0_BST0[1] | 0 | RW | Index 0 Boost Stage 0 bit 1 | |

| 6 | I0_BST0[0] | 0 | RW | Index 0 Boost Stage 0 bit 0 | |

| 5 | I0_BST1[1] | 0 | RW | Index 0 Boost Stage 1 bit 1 | |

| 4 | I0_BST1[0] | 0 | RW | Index 0 Boost Stage 1 bit 0 | |

| 3 | I0_BST2[1] | 0 | RW | Index 0 Boost Stage 2 bit 1 | |

| 2 | I0_BST2[0] | 0 | RW | Index 0 Boost Stage 2 bit 0 | |

| 1 | I0_BST3[1] | 0 | RW | Index 0 Boost Stage 3 bit 1 | |

| 0 | I0_BST3[0] | 0 | RW | Index 0 Boost Stage 3 bit 0 | |

| BST_Indx1 | Reg 0x41 Channel | 0x40 | Index1 4 Stage EQ Boost. | ||

| 7 | I1_BST0[1] | 0 | RW | Index 1 Boost Stage 0 bit 1 | |

| 6 | I1_BST0[0] | 1 | RW | Index 1 Boost Stage 0 bit 0 | |

| 5 | I1_BST1[1] | 0 | RW | Index 1 Boost Stage 1 bit 1 | |

| 4 | I1_BST1[0] | 0 | RW | Index 1 Boost Stage 1 bit 0 | |

| 3 | I1_BST2[1] | 0 | RW | Index 1 Boost Stage 2 bit 1 | |

| 2 | I1_BST2[0] | 0 | RW | Index 1 Boost Stage 2 bit 0 | |

| 1 | I1_BST3[1] | 0 | RW | Index 1 Boost Stage 3 bit 1 | |

| 0 | I1_BST3[0] | 0 | RW | Index 1 Boost Stage 3 bit 0 | |

| BST_Indx2 | Reg 0x42 Channel | 0x80 | Index2 4 Stage EQ Boost. | ||

| 7 | I2_BST0[1] | 1 | RW | Index 2 Boost Stage 0 bit 1 | |

| 6 | I2_BST0[0] | 0 | RW | Index 2 Boost Stage 0 bit 0 | |

| 5 | I2_BST1[1] | 0 | RW | Index 2 Boost Stage 1 bit 1 | |

| 4 | I2_BST1[0] | 0 | RW | Index 2 Boost Stage 1 bit 0 | |

| 3 | I2_BST2[1] | 0 | RW | Index 2 Boost Stage 2 bit 1 | |

| 2 | I2_BST2[0] | 0 | RW | Index 2 Boost Stage 2 bit 0 | |

| 1 | I2_BST3[1] | 0 | RW | Index 2 Boost Stage 3 bit 1 | |

| 0 | I2_BST3[0] | 0 | RW | Index 2 Boost Stage 3 bit 0 | |

| BST_Indx3 | Reg 0x43 Channel | 0x50 | Index3 4 Stage EQ Boost. | ||

| 7 | I3_BST0[1] | 0 | RW | Index 3 Boost Stage 0 bit 1 | |

| 6 | I3_BST0[0] | 1 | RW | Index 3 Boost Stage 0 bit 0 | |

| 5 | I3_BST1[1] | 0 | RW | Index 3 Boost Stage 1 bit 1 | |

| 4 | I3_BST1[0] | 1 | RW | Index 3 Boost Stage 1 bit 0 | |

| 3 | I3_BST2[1] | 0 | RW | Index 3 Boost Stage 2 bit 1 | |

| 2 | I3_BST2[0] | 0 | RW | Index 3 Boost Stage 2 bit 0 | |

| 1 | I3_BST3[1] | 0 | RW | Index 3 Boost Stage 3 bit 1 | |

| 0 | I3_BST3[0] | 0 | RW | Index 3 Boost Stage 3 bit 0 | |

| BST_Indx4 | Reg 0x44 Channel | 0xC0 | Index4 4 Stage EQ Boost. | ||

| 7 | I4_BST0[1] | 1 | RW | Index 4 Boost Stage 0 bit 1 | |

| 6 | I4_BST0[0] | 1 | RW | Index 4 Boost Stage 0 bit 0 | |

| 5 | I4_BST1[1] | 0 | RW | Index 4 Boost Stage 1 bit 1 | |

| 4 | I4_BST1[0] | 0 | RW | Index 4 Boost Stage 1 bit 0 | |

| 3 | I4_BST2[1] | 0 | RW | Index 4 Boost Stage 2 bit 1 | |

| 2 | I4_BST2[0] | 0 | RW | Index 4 Boost Stage 2 bit 0 | |

| 1 | I4_BST3[1] | 0 | RW | Index 4 Boost Stage 3 bit 1 | |

| 0 | I4_BST3[0] | 0 | RW | Index 4 Boost Stage 3 bit 0 | |

| BST_Indx5 | Reg 0x45 Channel | 0x90 | Index5 4 Stage EQ Boost. | ||

| 7 | I5_BST0[1] | 1 | RW | Index 5 Boost Stage 0 bit 1 | |

| 6 | I5_BST0[0] | 0 | RW | Index 5 Boost Stage 0 bit 0 | |

| 5 | I5_BST1[1] | 0 | RW | Index 5 Boost Stage 1 bit 1 | |

| 4 | I5_BST1[0] | 1 | RW | Index 5 Boost Stage 1 bit 0 | |

| 3 | I5_BST2[1] | 0 | RW | Index 5 Boost Stage 2 bit 1 | |

| 2 | I5_BST2[0] | 0 | RW | Index 5 Boost Stage 2 bit 0 | |

| 1 | I5_BST3[1] | 0 | RW | Index 5 Boost Stage 3 bit 1 | |

| 0 | I5_BST3[0] | 0 | RW | Index 5 Boost Stage 3 bit 0 | |

| BST_Indx6 | Reg 0x46 Channel | 0x54 | Index6 4 Stage EQ Boost. | ||

| 7 | I6_BST0[1] | 0 | RW | Index 6 Boost Stage 0 bit 1 | |

| 6 | I6_BST0[0] | 1 | RW | Index 6 Boost Stage 0 bit 0 | |

| 5 | I6_BST1[1] | 0 | RW | Index 6 Boost Stage 1 bit 1 | |

| 4 | I6_BST1[0] | 1 | RW | Index 6 Boost Stage 1 bit 0 | |

| 3 | I6_BST2[1] | 0 | RW | Index 6 Boost Stage 2 bit 1 | |

| 2 | I6_BST2[0] | 1 | RW | Index 6 Boost Stage 2 bit 0 | |

| 1 | I6_BST3[1] | 0 | RW | Index 6 Boost Stage 3 bit 1 | |

| 0 | I6_BST3[0] | 0 | RW | Index 6 Boost Stage 3 bit 0 | |

| BST_Indx7 | Reg 0x47 Channel | 0xA0 | Index7 4 Stage EQ Boost. | ||

| 7 | I7_BST0[1] | 1 | RW | Index 7 Boost Stage 0 bit 1 | |

| 6 | I7_BST0[0] | 0 | RW | Index 7 Boost Stage 0 bit 0 | |

| 5 | I7_BST1[1] | 1 | RW | Index 7 Boost Stage 1 bit 1 | |

| 4 | I7_BST1[0] | 0 | RW | Index 7 Boost Stage 1 bit 0 | |

| 3 | I7_BST2[1] | 0 | RW | Index 7 Boost Stage 2 bit 1 | |

| 2 | I7_BST2[0] | 0 | RW | Index 7 Boost Stage 2 bit 0 | |

| 1 | I7_BST3[1] | 0 | RW | Index 7 Boost Stage 3 bit 1 | |

| 0 | I7_BST3[0] | 0 | RW | Index 7 Boost Stage 3 bit 0 | |

| BST_Indx8 | Reg 0x48 Channel | 0xB0 | Index8 4 Stage EQ Boost. | ||

| 7 | I8_BST0[1] | 1 | RW | Index 8 Boost Stage 0 bit 1 | |

| 6 | I8_BST0[0] | 0 | RW | Index 8 Boost Stage 0 bit 0 | |

| 5 | I8_BST1[1] | 1 | RW | Index 8 Boost Stage 1 bit 1 | |

| 4 | I8_BST1[0] | 1 | RW | Index 8 Boost Stage 1 bit 0 | |

| 3 | I8_BST2[1] | 0 | RW | Index 8 Boost Stage 2 bit 1 | |

| 2 | I8_BST2[0] | 0 | RW | Index 8 Boost Stage 2 bit 0 | |

| 1 | I8_BST3[1] | 0 | RW | Index 8 Boost Stage 3 bit 1 | |

| 0 | I8_BST3[0] | 0 | RW | Index 8 Boost Stage 3 bit 0 | |

| BST_Indx9 | Reg 0x49 Channel | 0X95 | 0x95 | Index9 4 Stage EQ Boost. | |

| 7 | I9_BST0[1] | 1 | RW | Index 9 Boost Stage 0 bit 1 | |

| 6 | I9_BST0[0] | 0 | RW | Index 9 Boost Stage 0 bit 0 | |

| 5 | I9_BST1[1] | 0 | RW | Index 9 Boost Stage 1 bit 1 | |

| 4 | I9_BST1[0] | 1 | RW | Index 9 Boost Stage 1 bit 0 | |

| 3 | I9_BST2[1] | 0 | RW | Index 9 Boost Stage 2 bit 1 | |

| 2 | I9_BST2[0] | 1 | RW | Index 9 Boost Stage 2 bit 0 | |

| 1 | I9_BST3[1] | 0 | RW | Index 9 Boost Stage 3 bit 1 | |

| 0 | I9_BST3[0] | 1 | RW | Index 9 Boost Stage 3 bit 0 | |

| BST_Indx10 | Reg 0x4A Channel | 0x69 | Index10 4 Stage EQ Boost. | ||

| 7 | I10_BST0[1] | 0 | RW | Index 10 Boost Stage 0 bit 1 | |

| 6 | I10_BST0[0] | 1 | RW | Index 10 Boost Stage 0 bit 0 | |

| 5 | I10_BST1[1] | 1 | RW | Index 10 Boost Stage 1 bit 1 | |

| 4 | I10_BST1[0] | 0 | RW | Index 10 Boost Stage 1 bit 0 | |

| 3 | I10_BST2[1] | 1 | RW | Index 10 Boost Stage 2 bit 1 | |

| 2 | I10_BST2[0] | 0 | RW | Index 10 Boost Stage 2 bit 0 | |

| 1 | I10_BST3[1] | 0 | RW | Index 10 Boost Stage 3 bit 1 | |

| 0 | I10_BST3[0] | 1 | RW | Index 10 Boost Stage 3 bit 0 | |

| BST_Indx11 | Reg 0x4B Channel | 0xD5 | Index11 4 Stage EQ Boost. | ||

| 7 | I11_BST0[1] | 1 | RW | Index 11 Boost Stage 0 bit 1 | |

| 6 | I11_BST0[0] | 1 | RW | Index 11 Boost Stage 0 bit 0 | |

| 5 | I11_BST1[1] | 0 | RW | Index 11 Boost Stage 1 bit 1 | |

| 4 | I11_BST1[0] | 1 | RW | Index 11 Boost Stage 1 bit 0 | |

| 3 | I11_BST2[1] | 0 | RW | Index 11 Boost Stage 2 bit 1 | |

| 2 | I11_BST2[0] | 1 | RW | Index 11 Boost Stage 2 bit 0 | |

| 1 | I11_BST3[1] | 0 | RW | Index 11 Boost Stage 3 bit 1 | |

| 0 | I11_BST3[0] | 1 | RW | Index 11 Boost Stage 3 bit 0 | |

| BSTIndx12 | Reg 0x4C Channel | 0x99 | Index12 4 Stage EQ Boost. | ||

| 7 | I12_BST0[1] | 1 | RW | Index 12 Boost Stage 0 bit 1 | |

| 6 | I12_BST0[0] | 0 | RW | Index 12 Boost Stage 0 bit 0 | |

| 5 | I12_BST1[1] | 0 | RW | Index 12 Boost Stage 1 bit 1 | |

| 4 | I12_BST1[0] | 1 | RW | Index 12 Boost Stage 1 bit 0 | |

| 3 | I12_BST2[1] | 1 | RW | Index 12 Boost Stage 2 bit 1 | |

| 2 | I12_BST2[0] | 0 | RW | Index 12 Boost Stage 2 bit 0 | |

| 1 | I12_BST3[1] | 0 | RW | Index 12 Boost Stage 3 bit 1 | |

| 0 | I12_BST3[0] | 1 | RW | Index 12 Boost Stage 3 bit 0 | |

| BST_Indx13 | Reg 0x4D Channel | 0xA5 | Index13 4 Stage EQ Boost. | ||

| 7 | I13_BST0[1] | 1 | RW | Index 13 Boost Stage 0 bit 1 | |

| 6 | I13_BST0[0] | 0 | RW | Index 13 Boost Stage 0 bit 0 | |

| 5 | I13_BST1[1] | 1 | RW | Index 13 Boost Stage 1 bit 1 | |

| 4 | I13_BST1[0] | 0 | RW | Index 13 Boost Stage 1 bit 0 | |

| 3 | I13_BST2[1] | 0 | RW | Index 13 Boost Stage 2 bit 1 | |

| 2 | I13_BST2[0] | 1 | RW | Index 13 Boost Stage 2 bit 0 | |

| 1 | I13_BST3[1] | 0 | RW | Index 13 Boost Stage 3 bit 1 | |

| 0 | I13_BST3[0] | 1 | RW | Index 13 Boost Stage 3 bit 0 | |

| BST_Indx14 | Reg 0x4E Channel | 0xE6 | Index14 4 Stage EQ Boost. | ||

| 7 | I14_BST0[1] | 1 | RW | Index 14 Boost Stage 0 bit 1 | |

| 6 | I14_BST0[0] | 1 | RW | Index 14 Boost Stage 0 bit 0 | |

| 5 | I14_BST1[1] | 1 | RW | Index 14 Boost Stage 1 bit 1 | |

| 4 | I14_BST1[0] | 0 | RW | Index 14 Boost Stage 1 bit 0 | |

| 3 | I14_BST2[1] | 0 | RW | Index 14 Boost Stage 2 bit 1 | |

| 2 | I14_BST2[0] | 1 | RW | Index 14 Boost Stage 2 bit 0 | |

| 1 | I14_BST3[1] | 1 | RW | Index 14 Boost Stage 3 bit 1 | |

| 0 | I14_BST3[0] | 0 | RW | Index 14 Boost Stage 3 bit 0 | |

| BST_Indx15 | Reg 0x4F Channel | 0xF9 | Index15 4 Stage EQ Boost. | ||

| 7 | I15_BST0[1] | 1 | RW | Index 15 Boost Stage 0 bit 1 | |

| 6 | I15_BST0[0] | 1 | RW | Index 15 Boost Stage 0 bit 0 | |

| 5 | I15_BST1[1] | 1 | RW | Index 15 Boost Stage 1 bit 1 | |

| 4 | I15_BST1[0] | 1 | RW | Index 15 Boost Stage 1 bit 0 | |

| 3 | I15_BST2[1] | 1 | RW | Index 15 Boost Stage 2 bit 1 | |

| 2 | I15_BST2[0] | 0 | RW | Index 15 Boost Stage 2 bit 0 | |

| 1 | I15_BST3[1] | 0 | RW | Index 15 Boost Stage 3 bit 1 | |

| 0 | I15_BST3[0] | 1 | RW | Index 15 Boost Stage 3 bit 0 | |

| Active_EQ | Reg 0x52 Channel | 0x00 | Active CTLE Boost Setting Read Back | ||

| 7 | eq_bst_to_ana[7] | 0 | R | Read-back returns CTLE boost settings | |

| 6 | eq_bst_to_ana[6] | 0 | R | ||

| 5 | eq_bst_to_ana[5] | 0 | R | ||

| 4 | eq_bst_to_ana[4] | 0 | R | ||

| 3 | eq_bst_to_ana[3] | 0 | R | ||

| 2 | eq_bst_to_ana[2] | 0 | R | ||

| 1 | eq_bst_to_ana[1] | 0 | R | ||

| 0 | eq_bst_to_ana[0] | 0 | R | ||

| EQ_Control | Reg 0x55 Channel | 0x00 | EQ Adaptation Control | ||

| 7 | Reserved | 0 | R | ||

| 6 | Reserved | 0 | RW | ||

| 5 | Reserved | 0 | RW | ||

| 4 | Reserved | 0 | RW | ||

| 3 | Reserved | 0 | RW | ||

| 2 | Reserved | 0 | RW | ||

| 1 | INIT_CDR_SM_4 | 0 | RW | At power-up, this bit needs to be set to 1'b. See initialization set up | |

| 0 | Reserved | 0 | RW |

8.5.4 CDR Registers

Table 7. CDR Registers

| REGISTER NAME |

BITS | FIELD REGISTER ADDRESS |

DEFAULT | R/RW | DESCRIPTION |

|---|---|---|---|---|---|

| Output_Mux_OV | Reg 0x09 Channel | 0x00 | Output Data Mux Override | ||

| 7 | Reserved | 0 | RW | ||

| 6 | Reserved | 0 | RW | ||

| 5 | Reg_bypass_pfd_ovd | 0 | RW | 1: Enable values from 0x1E[7:5] & 0x1C[7:5] to control output mux 0: Register 0x1C[3:2] determines the output selection |

|

| 4 | Reserved | 0 | RW | ||

| 3 | Reserved | 0 | RW | ||

| 2 | Reserved | 0 | RW | ||

| 1 | Reserved | 0 | RW | ||

| 0 | Reserved | 0 | RW | ||

| CDR_Reset | Reg 0x0A Channel | 0x50 | CDR State Machine Reset | ||

| 7 | Reserved | 0 | RW | ||

| 6 | Reserved | 1 | RW | ||

| 5 | Reserved | 0 | RW | ||

| 4 | Reserved | 1 | RW | ||

| 3 | reg_cdr_reset_ov | 0 | RW | 1: Enable 0x0A[2] to control CDR Reset 0: Disable CDR Reset |

|

| 2 | reg_cdr_reset_sm | 0 | RW | 1: Enable CDR Reset if 0x0A[3] = 1'b 0: Disable CDR Reset if 0x0A[3] = 1'b |

|

| 1 | Reserved | 0 | RW | ||

| 0 | Reserved | 0 | RW | ||

| CDR_Status | Reg 0x0C Channel | 0x08 | CDR Status Control | ||

| 7 | reg_sh_status_control[3] | 0 | RW | Determines what is shown in Reg 0x02. See LMH0318 Programming Guide (SNLU183) | |

| 6 | reg_sh_status_control[2] | 0 | RW | ||

| 5 | reg_sh_status_control[1] | 0 | RW | ||

| 4 | reg_sh_status_control[0] | 0 | RW | ||

| 3 | Reserved | 1 | RW | ||

| 2 | Reserved | 0 | RW | ||

| 1 | Reserved | 0 | RW | ||

| 0 | Reserved | 0 | RW | ||

| EOM_Vrange | Reg 0x11 Channel | 0xE0 | EOM Vrange Setting and EOM Power Down Control | ||

| 7 | eom_sel_vrange[1] | 11 | RW | Sets eye monitor ADC granularity if 0x2C[6] =0'b 00: 3.125 mV 01: 6.25 mV 10: 9.375 mV 11: 12.5 mV |

|

| 6 | eom_sel_vrange[0] | ||||

| 5 | eom_PD | 1 | RW | 0: EOM Operational 1: Power down EOM |

|

| 4 | Reserved | 0 | RW | ||

| 3 | Reserved | 0 | RW | ||

| 2 | Reserved | 0 | RW | ||

| 1 | Reserved | 0 | RW | ||

| 0 | Reserved | 0 | RW | ||

| Full Temperature Range | Reg 0x16 Channel | 0x7A | Temperature Range Setting | ||

| 7 | INIT_CDR_SM_27 | 0 | RW | At power-up, this register needs to be set to 0x25. See initialization set up | |

| 6 | INIT_CDR_SM_26 | 1 | RW | ||

| 5 | INIT_CDR_SM_25 | 1 | RW | ||

| 4 | INIT_CDR_SM_24 | 1 | RW | ||

| 3 | INIT_CDR_SM_23 | 1 | RW | ||

| 2 | INIT_CDR_SM_22 | 0 | RW | ||

| 1 | INIT_CDR_SM_21 | 1 | RW | ||

| 0 | INIT_CDR_SM_20 | 0 | RW | ||

| HEO_VEO_OV | Reg 0x23 Channel | 0x40 | |||

| 7 | eom_get_heo_veo_ov | 0 | RW | 1: Enable reg 0x24[1] to acquire HEO/VEO 0: Disable reg 0x24[1] to acquire HEO/VEO |

|

| 6 | Reserved | 1 | RW | ||

| 5 | Reserved | 0 | RW | ||

| 4 | Reserved | 0 | RW | ||

| 3 | Reserved | 0 | RW | ||

| 2 | Reserved | 0 | RW | ||

| 1 | Reserved | 0 | RW | ||

| 0 | Reserved | 0 | RW | ||

| EOM_CNTL | Reg 0x24 Channel | 0x00 | 0x00 | Eye Opening Monitor Control Register | |

| 7 | fast_eom | 0 | R | 1: Enable Fast EOM mode 0: Disable fast EOM mode |

|

| 6 | Reserved | 0 | R | ||

| 5 | get_heo_veo_error_no_hits | 0 | R | 1: No zero crossing in the eye diagram observed 0: Zero crossing in the eye diagram detected |

|

| 4 | get_heo_veo_error_no_opening | 0 | R | 1: Eye diagram is completely closed 0: Open eye diagram detected |

|

| 3 | Reserved | 0 | R | ||

| 2 | Reserved | 0 | R | ||

| 1 | eom_get_heo_veo | 0 | RW | 1: Acquire HEO & VEO(self-clearing) 0: Normal operation |

|

| 0 | eom_start | 0 | R | 1: Starts EOM counter(self-clearing) 0: Normal operation |

|

| EOM_MSB | Reg 0x25 Channel | 0x00 | Eye opening monitor hits(MSB) | ||

| 7 | eom_count[15] | 0 | RW | MSBs of EOM counter | |

| 6 | eom_count[14] | 0 | RW | ||

| 5 | eom_count[13] | 0 | RW | ||

| 4 | eom_count[12] | 0 | RW | ||

| 3 | eom_count[11] | 0 | RW | ||

| 2 | eom_count[10] | 0 | RW | ||

| 1 | eom_count[9] | 0 | RW | ||

| 0 | eom_count[8] | 0 | RW | ||

| EOM_LSB | Reg 0x26 Channel | 0x00 | Eye opening monitor hits(LSB) | ||

| 7 | eom_count[7] | 0 | RW | LSBs of EOM counter | |

| 6 | eom_count[6] | 0 | RW | ||

| 5 | eom_count[5] | 0 | RW | ||

| 4 | eom_count[4] | 0 | RW | ||

| 3 | eom_count[3] | 0 | RW | ||

| 2 | eom_count[2] | 0 | RW | ||

| 1 | eom_count[1] | 0 | RW | ||

| 0 | eom_count[0] | 0 | RW | ||

| HEO | Reg 0x27 Channel | 0x00 | Horizontal Eye Opening | ||

| 7 | heo[7] | 0 | R | HEO value. This is measured in 0-63 phase settings. To get HEO in UI, read HEO, convert hex to dec, then divide by 64. | |

| 6 | heo[6] | 0 | R | ||

| 5 | heo[5] | 0 | R | ||

| 4 | heo[4] | 0 | R | ||

| 3 | heo[3] | 0 | R | ||

| 2 | heo[2] | 0 | R | ||

| 1 | heo[1] | 0 | R | ||

| 0 | heo[0] | 0 | R | ||

| VEO | Reg 0x28 Channel | 0x00 | Vertical Eye Opening | ||

| 7 | veo[7] | 0 | R | This is measured in 0-63 vertical steps. To get VEO in mV, read VEO, convert hex to dec, then multiply by 3.125mV | |

| 6 | veo[6] | 0 | R | ||

| 5 | veo[5] | 0 | R | ||

| 4 | veo[4] | 0 | R | ||

| 3 | veo[3] | 0 | R | ||

| 2 | veo[2] | 0 | R | ||

| 1 | veo[1] | 0 | R | ||

| 0 | veo[0] | 0 | R | ||

| Auto_EOM _Vrange | Reg 0x29 Channel | 0x00 | EOM Vrange Readback | ||

| 7 | Reserved | 0 | RW | ||

| 6 | eom_vrange_setting[1] | 00 | R | Auto Vrange readback of eye monitor granularity 00: 3.125mV 01: 6.25mV 10: 9.375mV 11: 12.5mV |

|

| 5 | eom_vrange_setting[0] | ||||

| 4 | Reserved | 0 | RW | ||

| 3 | Reserved | 0 | RW | ||

| 2 | Reserved | 0 | RW | ||

| 1 | Reserved | 0 | RW | ||

| 0 | Reserved | 0 | RW | ||

| EOM_Timer_Thr | Reg 0x2A Channel | 0x30 | EOM Hit Timer | ||

| 7 | eom_timer_thr[7] | 0 | RW | EOM timer for how long to check each phase/voltage setting | |

| 6 | eom_timer_thr[6] | 0 | RW | ||

| 5 | eom_timer_thr[5] | 1 | RW | ||

| 4 | eom_timer_thr[4] | 1 | RW | ||

| 3 | eom_timer_thr[3] | 0 | RW | ||

| 2 | eom_timer_thr[2] | 0 | RW | ||

| 1 | eom_timer_thr[1] | 0 | RW | ||

| 0 | eom_timer_thr[0] | 0 | RW | ||

| VEO_Scale | Reg 0x2C Channel | 0x32 | VEO_Scale | ||

| 7 | Reserved | 0 | RW | ||

| 6 | veo_scale | 0 | RW | 1: Enable Auto VEO scaling 0: VEO scaling based on Vrange Setting (0x11[7:6]) |

|

| 5 | Reserved | 1 | RW | ||

| 4 | Reserved | 1 | RW | ||

| 3 | Reserved | 0 | RW | ||

| 2 | Reserved | 0 | RW | ||

| 1 | Reserved | 1 | RW | ||

| 0 | Reserved | 0 | RW | ||

| HEO VEO Threshold | Reg 0x32 Channel | 0x11 | HEO/VEO Interrupt Threshold | ||

| 7 | heo_int_thresh[3] | 0 | RW | Compares HEO value, 0x27[7:0], vs threshold 0x32[7:4] * 4 | |

| 6 | heo_int_thresh[2] | 0 | RW | ||

| 5 | heo_int_thresh[1] | 0 | RW | ||

| 4 | heo_int_thresh[0] | 1 | RW | ||

| 3 | veo_int_thresh[3] | 0 | RW | Compares VEO value, 0x28[7:0], vs threshold 0x32[3:0 * 4 | |

| 2 | veo_int_thresh[2] | 0 | RW | ||

| 1 | veo_int_thresh[1] | 0 | RW | ||

| 0 | veo_int_thresh[0] | 1 | RW | ||

| CDR State Machine Control | Reg 0x3E Channel | 0x80 | CDR State Machine Setting | ||

| 7 | INIT_CDR_SM_3 | 1 | RW | At power-up, this bit needs to be set to 0'b. See initialization set up | |

| 6 | Reserved | 0 | RW | ||

| 5 | Reserved | 0 | RW | ||

| 4 | Reserved | 0 | RW | ||

| 3 | Reserved | 0 | RW | ||

| 2 | Reserved | 0 | RW | ||

| 1 | Reserved | 0 | RW | ||

| 0 | Reserved | 0 | RW | ||

| HEO_VEO_Lock | Reg 0x69 Channel | 0x0A | HEO/VEO Interval Monitoring | ||

| 7 | Reserved | 0 | RW | ||

| 6 | Reserved | 0 | RW | ||

| 5 | Reserved | 0 | RW | ||

| 4 | Reserved | 0 | RW | ||

| 3 | hv_lckmon_cnt_ms[3] | 1 | RW | While monitoring lock, this sets the interval time. Each interval is 6.5 ms. At default condition, HEO_VEO Lock Monitor occurs once every 65 ms. | |

| 2 | hv_lckmon_cnt_ms[2] | 0 | RW | ||

| 1 | hv_lckmon_cnt_ms[1] | 1 | RW | ||

| 0 | hv_lckmon_cnt_ms[0] | 0 | RW | ||

| CDR State Machine Control | Reg 0x6A Channel | 0x44 | CDR State Machine Control | ||

| 7 | INIT_CDR_SM_57 | 0 | RW | At power-up, this register should be set to 0x00. See initialization set up | |

| 6 | INIT_CDR_SM_56 | 1 | RW | ||

| 5 | INIT_CDR_SM_55 | 0 | RW | ||

| 4 | INIT_CDR_SM_54 | 0 | RW | ||

| 3 | INIT_CDR_SM_53 | 0 | RW | ||

| 2 | INIT_CDR_SM_52 | 1 | RW | ||

| 1 | INIT_CDR_SM_51 | 0 | RW | ||

| 0 | INIT_CDR_SM_50 | 0 | RW | ||

| SMPTE_Rate_Enable | Reg 0xA0 Channel | 0x1f | SMPTE_Data_Rate_Lock_Restriction | ||

| 7 | Reserved | 0 | RW | ||

| 6 | Reserved | 0 | RW | ||

| 5 | Reserved | 0 | RW | ||

| 4 | dvb_enable | 1 | RW | 1: Enable CDR Lock to 270 Mbps 0: Disable CDR Lock to 270 Mbps |

|

| 3 | hd_enable | 1 | RW | 1: Enable CDR Lock to 1.485/1.4835 Gbps 0: Disable CDR Lock to 1.485/1.4835 Gbps |

|

| 2 | 3G_enable | 1 | RW | 1: Enable CDR Lock to 2.97/2.967 Gbps 0: Disable CDR Lock to 2.97/2.967 Gbps |

|

| 1 | Reserved | 1 | RW | Reserved | |

| 0 | Reserved | 1 | RW | Reserved |

8.5.5 Transmitter Registers

Table 8. Transmitter Registers

| REGISTER NAME | BITS | FIELD REGISTER ADDRESS | DEFAULT | R/RW | DESCRIPTION |

|---|---|---|---|---|---|

| Out0_Mux_Select | Reg 0x1C Channel | 0x18 | OUT0 Mux Selection | ||

| 7 | pfd_sel0_data_mux[2] | 0 | RW | When 0x09[5] = 1'b OUT0 Mux Selection can be controlled as follows: 000: Mute 001: 10 MHz Clock 010: Raw Data 100: Retimed Data Other Settings - Invalid |

|

| 6 | pfd_sel0_data_mux[1] | 0 | RW | ||

| 5 | pfd_sel0_data_mux[0] | 0 | RW | ||

| 4 | vco_clk_sel | 1 | RW | When 0x09[5] = 1'b and 0x1E[[7:5] = 101'b OUT1 clock selection can be controlled as follows: 1: OUT1 puts out line rate clock 0: OUT1 puts out 10MHz clock |

|

| 3 | mr_drv_out_ctrl[1] | 1 | RW | Controls both OUT0 and OUT1: 00: OUT0: Mute OUT1: Mute 01: OUT0: Locked Reclocked Data / Unlocked Raw Data OUT1: Locked Output Clock / Unlocked Mute 10: OUT0: Locked Reclocked Data / Unlocked RAW OUT1: Locked Reclocked Data / Unlocked Raw 11: OUT0: Forced Raw OUT1: Forced Raw |

|

| 2 | mr_drv_out_ctrl[0] | 0 | RW | ||

| 1 | Reserved | 0 | RW | ||

| 0 | Reserved | 0 | RW | ||

| OUT1_Mux_Select | Reg 0x1E Channel | 0xE9 | OUT1 Mux Selection | ||

| 7 | pfd_sel_data_mux[2] | 1 | RW | When 0x09[5] = 1'b OUT0 Mux Selection can be controlled as follows: 111: Mute 101: 10MHz Clock if reg 0x1c[4]=0 and full rate clock if reg 0x1c[4] = 1 010: Full Rate Clock 001: Retimed Data 000: Raw Data Other Settings - Invalid |

|

| 6 | pfd_sel_data_mux[1] | 1 | RW | ||

| 5 | pfd_sel_data_mux[0] | 1 | RW | ||

| 4 | Reserved | 0 | RW | ||

| 3 | Reserved | 1 | RW | ||

| 2 | Reserved | 0 | RW | ||

| 1 | Reserved | 0 | RW | ||

| 0 | Reserved | 1 | RW | ||

| OUT1 Invert | Reg 0x1F Channel | 0x10 | Invert OUT1 Polarity | ||

| 7 | pfd_sel_inv_out1 | 0 | RW | 1: Inverts OUT1 polarity 0: OUT1 Normal polarity |

|

| 6 | Reserved | 0 | RW | ||

| 5 | Reserved | 0 | RW | ||

| 4 | Reserved | 1 | RW | ||

| 3 | Reserved | 0 | RW | ||

| 2 | Reserved | 0 | RW | ||

| 1 | Reserved | 0 | RW | ||

| 0 | Reserved | 0 | RW | ||

| OUT0_VOD | Reg 0x80 Channel | 0x54 | OUT0 VOD_PD | ||

| 7 | drv_0_sel_vod[3] | 0 | RW | Controls OUTDriver 0 VOD Setting 0011: Nominal - 10% 0100: Nominal - 5% 0101: Nominal 800 mV 0110: Nominal + 5% 0111: Nominal + 10% Other Settings - Invalid |

|

| 6 | drv_0_sel_vod[2] | 1 | RW | ||

| 5 | drv_0_sel_vod[1] | 0 | RW | ||

| 4 | drv_0_sel_vod[0] | 1 | RW | ||

| 3 | Reserved | 0 | RW | ||

| 2 | Reserved | 1 | RW | ||

| 1 | mr_drv_0_ov | 0 | RW | 1: Enable 0x80[0] to override pin/sm control 0: Disable 0x80[0] to override pin/sm control |

|

| 0 | sm_drv_0_PD | 0 | RW | 1: Power down OUT0 0: OUT1 in normal operating mode |

|

| OUT1_VOD | Reg 0x84 Channel | 0x04 | OUT1 VOD Control | ||

| 7 | Reserved | 0 | RW | ||

| 6 | drv_1_sel_vod[2] | 0 | RW | OUTDriver1 VOD Setting 000: 570 mVDifferential(Diff) Peak to Peak(PP) 010: 730 mV(Diff PP) 100: 900 mV(Diff PP) 110: 1035 mV(Diff PP) |

|

| 5 | drv_1_sel_vod[1] | 0 | RW | ||

| 4 | drv_1_sel_vod[0] | 0 | RW | ||

| 3 | Reserved | 0 | RW | ||

| 2 | drv_1_sel_scp | 1 | RW | 1: Enables short circuit protection on OUT1 0: Disable short circuit protection on OUT1 |

|

| 1 | mr_drv_1_ov | 0 | RW | 1: Enable 0x80[0] to override pin/sm control 0: Disable 0x80[0] to override pin/sm control |

|

| 0 | sm_drv_1_PD | 0 | RW | 1: Power down OUT1 driver 0: OUT1 in normal operating mode |

|

| OUT1_DE | Reg 0x85 | 0x00 | OUT1 DE Control | ||

| 7 | Reserved | 0 | RW | ||

| 6 | Reserved | 0 | RW | ||

| 5 | Reserved | 0 | RW | ||

| 4 | Reserved | 0 | RW | ||

| 3 | drv_1_dem_range | 0 | RW | Controls de-emphasis of 50 Ω Driver 0000: DE Disabled 0001: 0.2 dB 0010: 1.8 dB ......... 0111: 11 dB |

|

| 2 | drv_1_dem[2] | 0 | RW | ||

| 1 | drv_1_dem[1] | 0 | RW | ||

| 0 | drv_1_dem[0] | 0 | RW |