JAJSMA9A october 2021 – june 2023 LMK1D1208P

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Revision History

- 5 Device Comparison

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Parameter Measurement Information

- 9 Detailed Description

- 10Application and Implementation

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

- RHA|40

サーマルパッド・メカニカル・データ

- RHA|40

発注情報

10.2.3 Application Curves

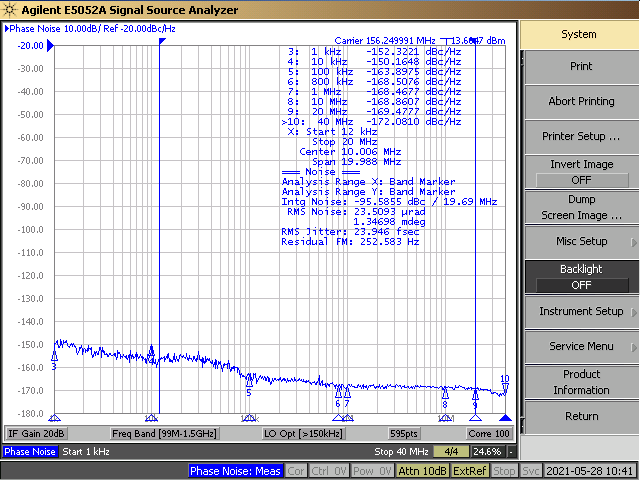

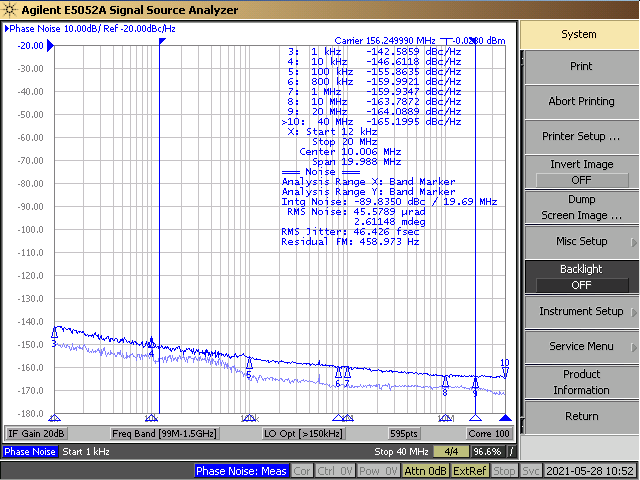

This section shows the low additive noise for the LMK1D1208P. The low noise 156.25-MHz source with 24-fs RMS jitter shown in Figure 10-2 drives the LMK1D1208P, resulting in 46.4-fs RMS when integrated from 12 kHz to 20 MHz (see Figure 10-3). The resultant additive jitter is 39.7-fs RMS for this configuration.

| Note: Reference signal is a low-noise Rhode and Schwarz SMA100B |

Figure 10-3 LMK1D1208P Output Phase Noise, 156.25 MHz, 46.4-fs RMS (12 kHz to 20 MHz)

Figure 10-3 LMK1D1208P Output Phase Noise, 156.25 MHz, 46.4-fs RMS (12 kHz to 20 MHz)