JAJSDE8B July 2017 – March 2018 LMS3655

PRODUCTION DATA.

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 Device Comparison Table

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Detailed Description

-

9 Application and Implementation

- 9.1 Application Information

- 9.2

Typical Applications

- 9.2.1 General Application

- 9.2.2 Adjustable 5-V Output

- 9.2.3 Adjustable 3.3-V Output

- 9.2.4 6-V Adjustable Output

- 9.3 Do's and Don't's

- 10Power Supply Recommendations

- 11Layout

- 12デバイスおよびドキュメントのサポート

- 13メカニカル、パッケージ、および注文情報

8.3.1 RESET Flag Output

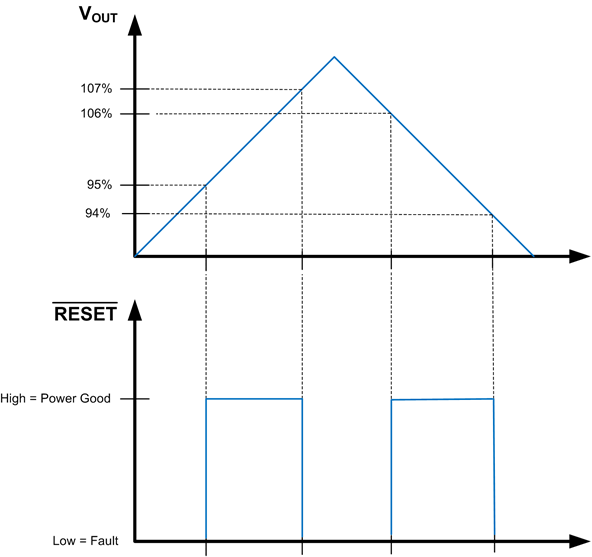

While the LMS3655 reset function resembles a standard Power-Good function, its functionality is designed to replace a discrete reset device, reducing additional component cost. There are three major differences between the reset function and the normal power good function seen in most regulators.

- A delay has been added between the point at which the output voltage is within specified limits and the flag asserts Power Good. A glitch filter prevents false flag operation for short excursions in the output voltage, such as during line and load transients. See Figure 11 and Figure 12 for more detail.

- RESET output signals a fault (pulls its output to ground) while the part is disabled.

- RESET continues to operate with input voltage as low as 1.5 V. Below this input voltage, RESET output may be high impedance.

Because the RESET comparator and the regulation loop share the same reference, the thresholds track with the output voltage. When EN is pulled low, the RESET flag output is forced low. When the device is disabled, RESET remains valid as long as the input voltage is ≥ 1.5 V. RESET operation can best be understood by reference to Figure 10 and Figure 11. Output voltage excursions lasting less than TRESET-filter do not trip RESET. Once the output voltage is within the prescribed limits, a delay of TRESET-act is imposed before RESET goes high. This enables tighter tolerance than is possible with an external supervisor device while also expanding the system allowance for transient response without the need for extremely accurate internal circuitry.

This output consists of an open-drain NMOS; requiring an external pullup resistor to a suitable logic supply. It can also be pulled up to either VCC or VOUT, through an appropriate resistor, as desired. The pin can be left floating or grounded if the RESET function is not used in the application. The maximum current into this pin must be limited to 10 mA, and the maximum voltage must be less than 8 V.

Figure 10. Static RESET Operation

Figure 10. Static RESET Operation

Figure 11. RESET Timing Behavior

Figure 11. RESET Timing Behavior

The threshold voltage for the RESET function takes advantage of the availability of the LMS3655 internal feedback threshold to the RESET circuit. This allows a maximum threshold of 96.5% of selected output voltage to be specified at the same time as 96% of actual set point.