JAJS595I August 1999 – June 2016 LMV821-N , LMV822-N , LMV822-N-Q1 , LMV824-N , LMV824-N-Q1

PRODUCTION DATA.

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 ESD Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Thermal Information, 5 Pins

- 6.5 Thermal Information, 8 Pins

- 6.6 Thermal Information, 14 Pins

- 6.7 DC Electrical Characteristics 2.7V

- 6.8 DC Electrical Characteristics 2.5V

- 6.9 AC Electrical Characteristics 2.7V

- 6.10 DC Electrical Characteristics 5V

- 6.11 AC Electrical Characteristics 5V

- 6.12 Typical Characteristics

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11デバイスおよびドキュメントのサポート

- 12メカニカル、パッケージ、および注文情報

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

サーマルパッド・メカニカル・データ

発注情報

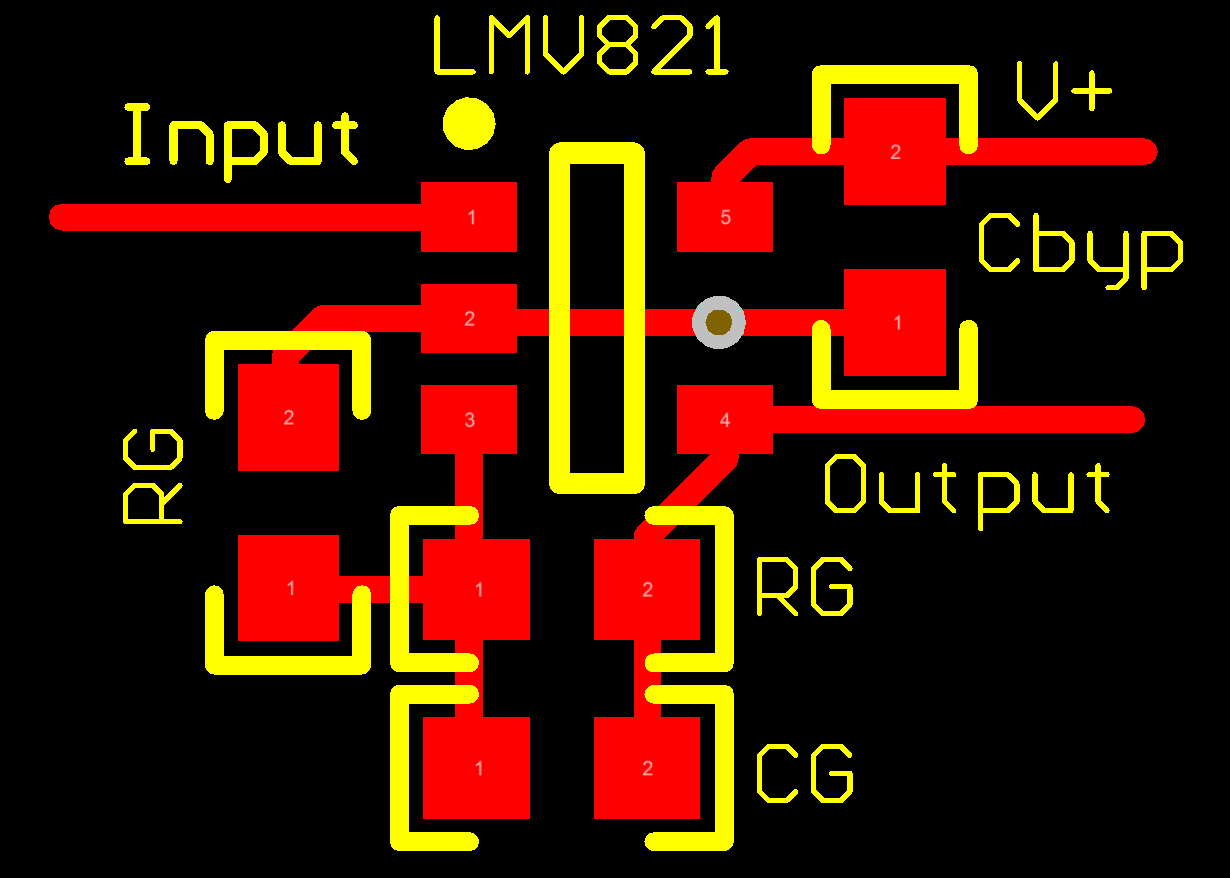

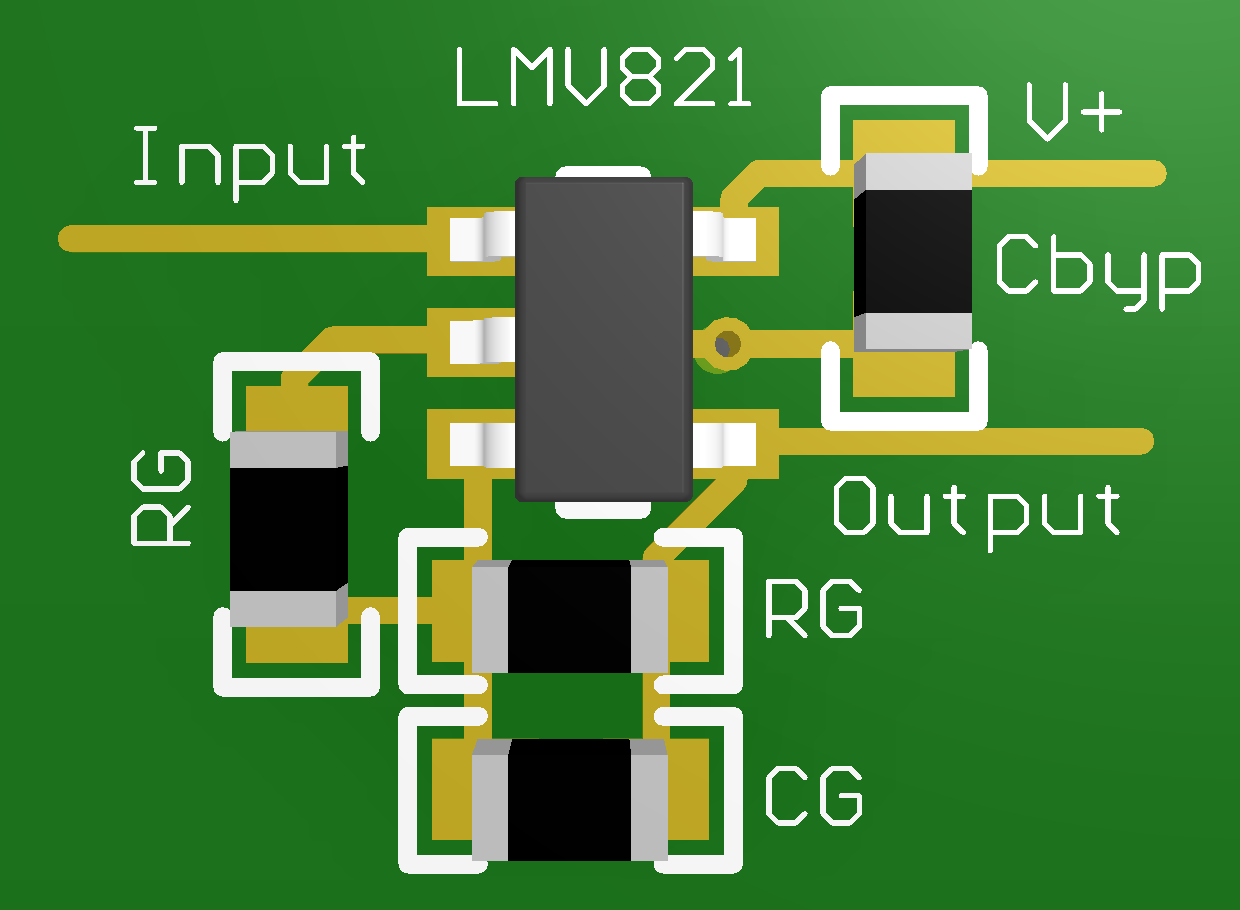

10 Layout

10.1 Layout Guidelines

The V+ pin should be bypassed to ground with a low ESR capacitor.

The optimum placement is closest to the V+ and ground pins.

Care should be taken to minimize the loop area formed by the bypass capacitor connection between V+ and ground.

The ground pin should be connected to the PCB ground plane at the pin of the device.

The feedback components should be placed as close to the device as possible minimizing strays.

10.2 Layout Example

Figure 47. 2-D Layout

Figure 47. 2-D Layout

Figure 48. 3-D Layout

Figure 48. 3-D Layout