JAJSG07E August 2012 – August 2018 LMZ21701

PRODUCTION DATA.

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11デバイスおよびドキュメントのサポート

- 12メカニカル、パッケージ、および注文情報

パッケージ・オプション

デバイスごとのパッケージ図は、PDF版データシートをご参照ください。

メカニカル・データ(パッケージ|ピン)

- SIL|8

サーマルパッド・メカニカル・データ

発注情報

8.2.3.2 VOUT = 1.8 V

Figure 32. Typical Applications Circuit

Figure 32. Typical Applications Circuit  Figure 34. Efficiency VOUT = 1.8 V

Figure 34. Efficiency VOUT = 1.8 V  Figure 36. Load Transient VOUT = 1.8 V

Figure 36. Load Transient VOUT = 1.8 V  Figure 38. 20 MHz Oscilloscope Bandwidth

Figure 38. 20 MHz Oscilloscope Bandwidth

Output Voltage Ripple VOUT = 1.8 V

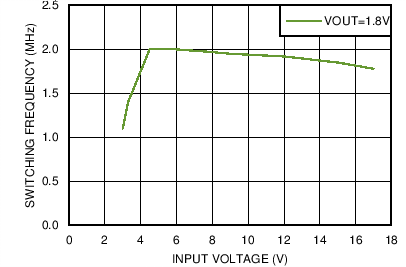

Figure 40. Typical Switching Frequency at 1000 mA Load VOUT = 1.8 V

Figure 40. Typical Switching Frequency at 1000 mA Load VOUT = 1.8 V  Figure 42. Line and Load Regulation VOUT = 1.8 V

Figure 42. Line and Load Regulation VOUT = 1.8 V  Figure 33. External Component Values

Figure 33. External Component Values

(VOUT = 1.8 V)

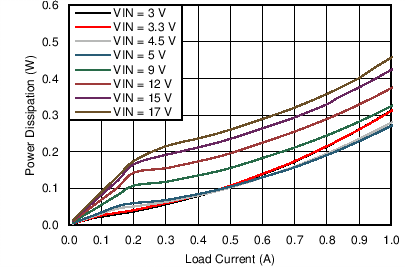

Figure 35. Power Dissipation VOUT = 1.8 V

Figure 35. Power Dissipation VOUT = 1.8 V  Figure 37. Startup VOUT = 1.8 V

Figure 37. Startup VOUT = 1.8 V  Figure 39. 500 MHz Oscilloscope Bandwidth, 3x1000 pF additional output capacitance

Figure 39. 500 MHz Oscilloscope Bandwidth, 3x1000 pF additional output capacitance

Output Voltage Ripple and HF Noise VOUT = 1.8 V

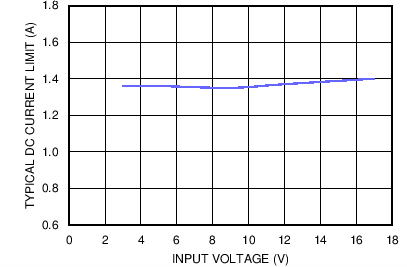

Figure 41. Typical Current Limit VOUT = 1.8 V, TA = 85 °C

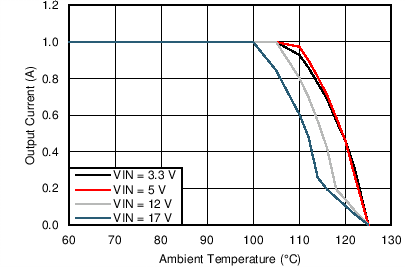

Figure 41. Typical Current Limit VOUT = 1.8 V, TA = 85 °C  Figure 43. Thermal Derating for θJA= 47ºC/W VOUT = 1.8 V

Figure 43. Thermal Derating for θJA= 47ºC/W VOUT = 1.8 V