JAJSQM5C july 2003 – june 2023 SN74AHC02-Q1

PRODMIX

- 1

- 1特長

- 2概要

- 3Revision History

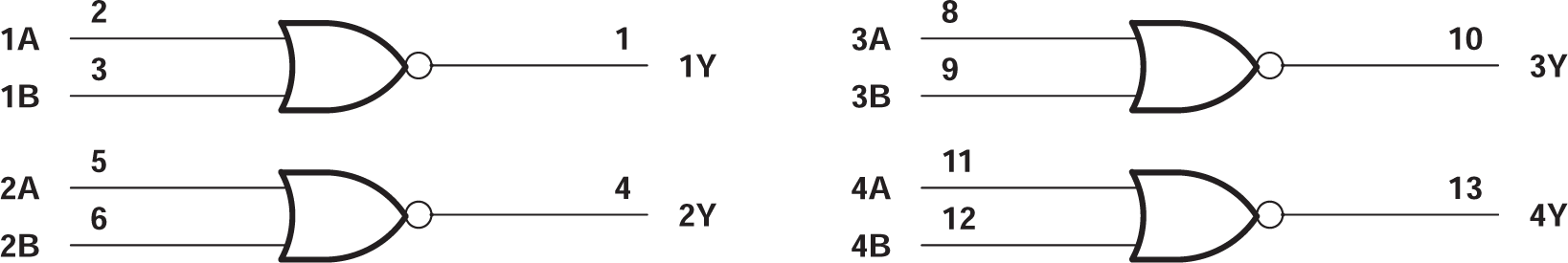

- 4Pin Configuration and Functions

- 5Specifications

- 6Parameter Measurement Information

- 7Detailed Description

- 8Device and Documentation Support

- 9Mechanical, Packaging, and Orderable Information

パッケージ・オプション

デバイスごとのパッケージ図は、PDF版データシートをご参照ください。

メカニカル・データ(パッケージ|ピン)

- PW|14

- BQA|14