JAJSFC9B September 2017 – June 2018 TPS560430

UNLESS OTHERWISE NOTED, this document contains PRODUCTION DATA.

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 Device Comparison Table

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Detailed Description

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12デバイスおよびドキュメントのサポート

- 13メカニカル、パッケージ、および注文情報

パッケージ・オプション

デバイスごとのパッケージ図は、PDF版データシートをご参照ください。

メカニカル・データ(パッケージ|ピン)

- DBV|6

サーマルパッド・メカニカル・データ

発注情報

8.3.4 Minimum ON-Time, Minimum OFF-Time and Frequency Foldback

Minimum ON-time, TON_MIN, is the smallest duration of time that the HS switch can be on. TON_MIN is typically 60 ns in the TPS560430. Minimum OFF-time, TOFF_MIN, is the smallest duration that the HS switch can be off. TOFF_MIN is typically 100 ns. In CCM operation, TON_MIN and TOFF_MIN limit the voltage conversion range without switching frequency foldback.

The minimum duty cycle without frequency foldback allowed is

The maximum duty cycle without frequency foldback allowed is

Given a required output voltage, the maximum VIN without frequency foldback can be found by

The minimum VIN without frequency foldback can be calculated by

In the TPS560430, a frequency foldback scheme is employed once the TON_MIN or TOFF_MIN is triggered, which may extend the maximum duty cycle or lower the minimum duty cycle.

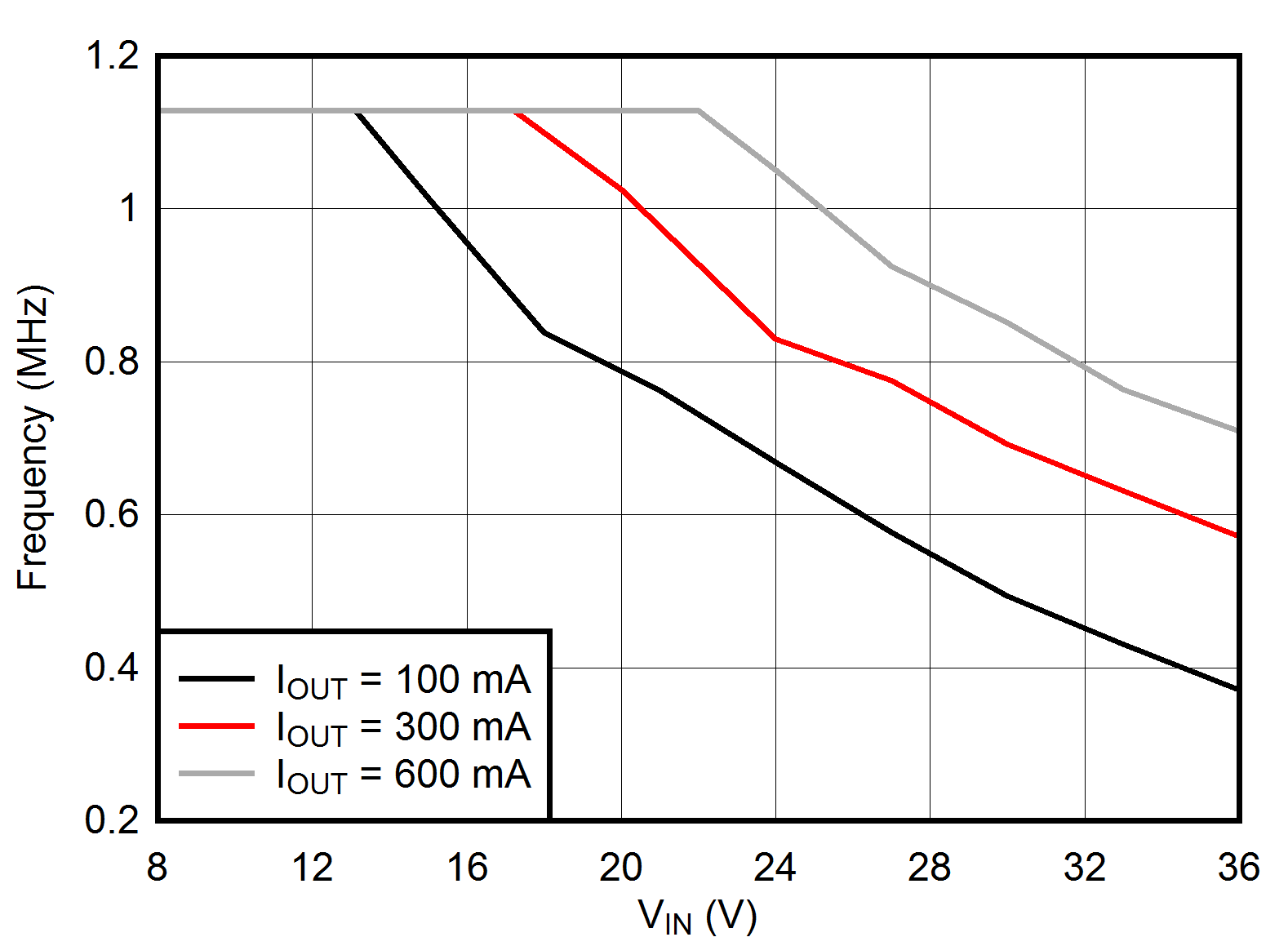

The on-time decreases while VIN voltage increases. Once the on-time decreases to TON_MIN, the switching frequency starts to decrease while VIN continues to go up, which lowers the duty cycle further to keep VOUT in regulation according to Equation 2.

The frequency foldback scheme also works once larger duty cycle is needed under low VIN condition. The frequency decreases once the device hits its TOFF_MIN, which extends the maximum duty cycle according to Equation 3. In such condition, the frequency can be as low as about 133 kHz minimum. Wide range of frequency foldback allows the TPS560430 output voltage stay in regulation with a much lower supply voltage VIN, which leads to a lower effective drop-out.

With frequency foldback, VIN_MAX is raised, and VIN_MIN is lowered by decreased fSW.

| VOUT = 1 V | fSW = 1.1 MHz |

| VOUT = 5 V | fSW = 1.1 MHz |