JAJSQ72B june 2014 – may 2023 TPS65262-1

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Revision History

- 5 Device Comparison Table

- 6 Pin Configuration and Functions

- 7 Specifications

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3

Feature Description

- 8.3.1 Adjusting the Output Voltage

- 8.3.2 Enable and Adjusting UVLO

- 8.3.3 Soft-Start Time

- 8.3.4 Power-Up Sequencing

- 8.3.5 V7V Low Dropout Regulator and Bootstrap

- 8.3.6 Out-of-Phase Operation

- 8.3.7 Output Overvoltage Protection (OVP)

- 8.3.8 PSM

- 8.3.9 Slope Compensation

- 8.3.10 Overcurrent Protection (OCP)

- 8.3.11 Power Good

- 8.3.12 Thermal Shutdown

- 8.4 Device Functional Modes

- 9 Application and Implementation

- 10Device and Documentation Support

- 11Mechanical, Packaging, and Orderable Information

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

- RHB|32

サーマルパッド・メカニカル・データ

- RHB|32

発注情報

3 概要

TPS65262-1 は、出力電流 3A/1A/1A のモノリシック・トリプル同期降圧型 (バック) コンバータです。4.5V~18V の幅広い入力電源電圧範囲をサポートしており、5V、9V、12V、または 15V のようなほとんどの中間バス電圧入力に対応できます。コンバータは定周波数ピーク電流モードを備え、アプリケーションを単純化しながら、目的のアプリケーションに合わせてシステムを最適化できるよう設計されています。このデバイスは、600kHz の固定スイッチング周波数で動作します。外付け部品数を低減するため、Buck2 と Buck3 のループ補償を内蔵しています。Buck1 と Buck2/Buck3 は位相差 180°で動作するため (Buck2 と Buck3 は同相動作)、入力フィルタの要件が最小化されます。軽負荷時には、デバイスは自動的にパルス・スキップ・モード (PSM) で動作し、スイッチング損失を低減することで高い効率を実現します。

TPS65262-1 は、2 つの低ドロップアウト電圧リニア・レギュレータ (LDO) を内蔵しています。これらの LDO は入力電圧範囲が 1.3~5.5V、連続出力電流が 350/150mA であり、独立したイネーブルを備え、出力電圧は可変です。

TPS65262-1 には、MODE ピンを High に駆動し、EN1、EN2、EN3 ピンを設定する自動パワー・シーケンスが搭載されています。

本デバイスには、過電圧、過電流、短絡、過熱保護が搭載されています。いずれかの降圧出力電圧がレギュレーション範囲を外れると、パワー・グッド・ピンがアサートされます。

| 部品番号 | パッケージ | 本体サイズ (公称) |

|---|---|---|

| TPS65262-1 | RHB (VQFN、32) | 5.00mm × 5.00mm |

代表的なアプリケーション

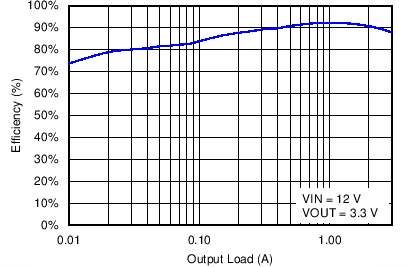

代表的なアプリケーション 効率と出力負荷との関係

効率と出力負荷との関係