JAJSMF2A February 2022 – September 2022 TPS7H5005-SEP , TPS7H5006-SEP , TPS7H5007-SEP , TPS7H5008-SEP

PRODUCTION DATA

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Revision History

- 5 Device Comparison Table

- 6 Pin Configuration and Functions

-

7 Specifications

- 7.1 Absolute Maximum Ratings

- 7.2 ESD Ratings

- 7.3 Recommended Operating Conditions

- 7.4 Thermal Information

- 7.5 Electrical Characteristics: All Devices

- 7.6 Electrical Characteristics: TPS7H5005-SEP

- 7.7 Electrical Characteristics: TPS7H5006-SEP

- 7.8 Electrical Characteristics: TPS7H5007-SEP

- 7.9 Electrical Characteristics: TPS7H5008-SEP

- 7.10 Typical Characteristics

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3

Feature Description

- 8.3.1 VIN and VLDO

- 8.3.2 Start-Up

- 8.3.3 Enable and Undervoltage Lockout (UVLO)

- 8.3.4 Voltage Reference

- 8.3.5 Error Amplifier

- 8.3.6 Output Voltage Programming

- 8.3.7 Soft Start (SS)

- 8.3.8 Switching Frequency and External Synchronization

- 8.3.9 Primary Switching Outputs (OUTA/OUTB)

- 8.3.10 Synchronous Rectifier Outputs (SRA/SRB)

- 8.3.11 Dead Time and Leading Edge Blank Time Programmability (PS, SP, and LEB)

- 8.3.12 Pulse Skipping

- 8.3.13 Duty Cycle Programmability

- 8.3.14 Current Sense and PWM Generation (CS_ILIM)

- 8.3.15 Hiccup Mode Operation (HICC)

- 8.3.16 External Fault Protection (FAULT)

- 8.3.17 Slope Compensation (RSC)

- 8.3.18 Frequency Compensation

- 8.3.19 Thermal Shutdown

- 8.4 Device Functional Modes

-

9 Application and Implementation

- 9.1 Application Information

- 9.2

Typical Application

- 9.2.1 Design Requirements

- 9.2.2

Detailed Design Procedure

- 9.2.2.1 Switching Frequency

- 9.2.2.2 Output Voltage Programming Resistors

- 9.2.2.3 Dead Time

- 9.2.2.4 Leading Edge Blank Time

- 9.2.2.5 Soft-Start Capacitor

- 9.2.2.6 Transformer

- 9.2.2.7 Main Switching FETs

- 9.2.2.8 Synchronous Rectificier FETs

- 9.2.2.9 RCD Clamp

- 9.2.2.10 Output Inductor

- 9.2.2.11 Output Capacitance and Filter

- 9.2.2.12 Sense Resistor

- 9.2.2.13 Hiccup Capacitor

- 9.2.2.14 Frequency Compensation Components

- 9.2.2.15 Slope Compensation Resistor

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

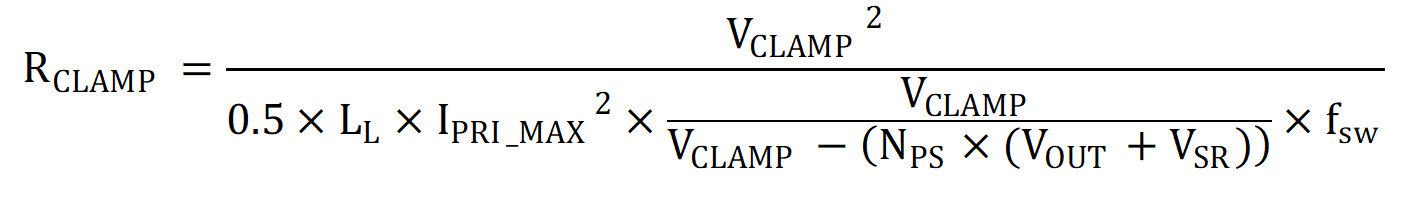

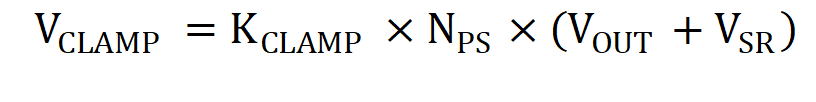

9.2.2.9 RCD Clamp

A resistor-capacitor-diode clamp circuit can be used to limit the voltage at the switch node. The equations below can be used to determine initial values for the resistor and capacitor, but the circuit will need to be optimized through testing. First, calculate the clamp voltage by determining how much overshoot is allowable at the switch node.

The parameter KCLAMP defines the target overshoot value. For example, set KCLAMP to 1.5 for 50% allowable overshoot.

Next, the leakage inductance LL and peak primary current IPRI_MAX of the transformer can be used to approximate the clamp resistor. The clamp capacitor value can be determined thereafter. Note that ΔVCLAMP defines the allowable ripple for the clamp capacitor.