SLLSE32G November 2010 – November 2017 TUSB1310A

PRODUCTION DATA.

- 1Device Overview

- 2Revision History

- 3Pin Configuration and Functions

- 4Specifications

-

5Detailed Description

- 5.1 Overview

- 5.2 Functional Block Diagram

- 5.3 Feature Description

- 5.4 Device Functional Modes

- 5.5

Register Maps

- 5.5.1 Vendor ID and Product ID (00h-03h)

- 5.5.2 Function Control (04h-06h)

- 5.5.3 Interface Control (07h-09h)

- 5.5.4 OTG Control

- 5.5.5 USB Interrupt Enable Rising (0Dh-0Fh)

- 5.5.6 USB Interrupt Enable Falling (10h-12h)

- 5.5.7 USB Interrupt Status (13h)

- 5.5.8 USB Interrupt Latch (14h)

- 5.5.9 Debug (15h)

- 5.5.10 Scratch Register (16-18h)

- 6Application, Implementation, and Layout

- 7Device and Documentation Support

- 8Mechanical, Packaging, and Orderable Information

6 Application, Implementation, and Layout

NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI’s customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

6.1 Application Information

Texas Instruments’ TUSB1310A device is a single port, 5.0-Gbps USB 3.0 physical layer transceiver that is available in a lead-free, 175-ball, 12-mm × 12-mm NFBGA package (ZAY). The link controller interfaces to the TUSB1310A device are through a PIPE (16-bit wide operating at 250 MHz) and a ULPI (8-bit wide operating at 60 MHz) interface. The USB connector interfaces to the TUSB1310A device through a USB 3.0 SuperSpeed USB differential pair (TX and RX) and USB 2.0 differential pair (DP/DM).

6.2 Typical Application

Figure 6-1 represents a typical implementation of the TUSB1310A USB 3.0 physical layer transceiver that operates off of a single crystal or an external reference clock. The reference frequencies are selectable from 20, 25, 30, and 40 MHz. The TUSB1310A device provides a clock to the USB link layer controllers. The single reference clock allows the TUSB1310A device to provide a cost effective USB 3.0 solution with few external components and a minimum implementation cost.

Figure 6-1 Typical Application Schematic

Figure 6-1 Typical Application Schematic

6.2.1 Design Requirements

6.2.1.1 Clock Source Requirements

6.2.1.1.1 Clock Source Selection Guide

Reference clock jitter is an important parameter. Jitter on the reference clock degrades both the transmit eye and receiver jitter tolerance, no matter how clean the rest of the PLL is, thereby impairing system performance. Additionally, a particularly jittery reference clock may interfere with PLL lock detection mechanism, forcing the lock detector to issue an unlock signal. A good quality, low jitter reference clock is required to achieve compliance with supported USB 3.0 standards. For example, USB 3.0 specification requires the random jitter (RJ) component of either RX or TX to be 2.42 ps (random phase jitter calculated after applying jitter transfer function [JTF]). As the PLL typically has a number of additional jitter components, the reference clock jitter must be considerably below the overall jitter budget.

6.2.1.1.2 Oscillator

If an external clock source is used, XI must be tied to the clock source and XO must be left floating.

Table 6-1 Oscillator Specification

| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|---|---|---|---|---|---|

| Frequency tolerance | Operational temperature | ±50 | ppm | ||

| Frequency stability | 1 year aging | ±50 | ppm | ||

| Rise and Fall time | 20% to 80% | 6 | nsec | ||

| Reference clock RJ with JTF (1 sigma)(1)(2) | 0.8 | psec | |||

| Reference clock TJ with JTF (total p-p)(2)(3) | 25 | psec | |||

| Reference clock jitter (absolute p-p)(4) | 50 | psec |

6.2.1.1.3 Crystal

Either a 20-MHz, 25-MHz, 30-MHz, or 40-MHz crystal can be selected. A parallel, 20-pF load crystal must be used if a crystal source is used.

Table 6-2 Crystal Specification

| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|---|---|---|---|---|---|

| Frequency tolerance | Operational temperature | ±50 | ppm | ||

| Frequency stability | 1 year aging | ±50 | ppm | ||

| Load capacitance | 12 | 20 | 24 | pF |

6.2.2 Detailed Design Procedure

6.2.2.1 Chip Connection on PCB

Components must be placed close to the TUSB1310A device to reduce the trace length of the interface between the components and the TUSB1310A. If external capacitors cannot accommodate a close placement, shielding to ground is recommended.

Figure 6-2 Analog Pin Connections

Figure 6-2 Analog Pin Connections

6.2.2.1.1 USB Connector Pins Connection

The following rules apply for differential pair signals (DP/DM, SSTXP/SSTXN, and SSRXP/SSRXN):

- Keep as short as possible

- Must be trace-length matched and parallelism must be maintained

- Minimize vias and corners

- Avoid crossing plane splits and stubs

Figure 6-3 and Figure 6-4 are for visual reference only.

Figure 6-3 USB Standard-A Connector Pin Connection

Figure 6-3 USB Standard-A Connector Pin Connection

Figure 6-4 USB Standard-B Connector Pin Connection

Figure 6-4 USB Standard-B Connector Pin Connection

6.2.2.1.2 Clock Connections

The TUSB1310A device supports an external oscillator source or a crystal unit. If a clock is provided to XI instead of a crystal, XO is left open. Otherwise, if a crystal is used, the connection must adhere to the following guidelines.

Because XI and XO are coupled to other leads and supplies on the PCB, it is important to keep them as short as possible and away from any switching leads. It is also recommended to minimize the capacitance between XI and XO. This can be accomplished by connecting the VSSOSC lead to the two external capacitors CL1 and CL2 and shielding them with the clean ground lines. The VSSOSC must not be connected to PCB ground.

Load capacitance (CLOAD) of the crystal varying with the crystal vendors is the total capacitance value of the entire oscillation circuit system as seen from the crystal. It includes two external capacitors CL1 and CL2 in Figure 6-5. The trace length between the decoupling capacitors and the corresponding power pins on the TUSB1310A device must be minimized. It is also recommended that the trace length from the capacitor pad to the power or ground plane be minimized.

Figure 6-5 Typical Crystal Connections

Figure 6-5 Typical Crystal Connections

6.2.3 Application Curve

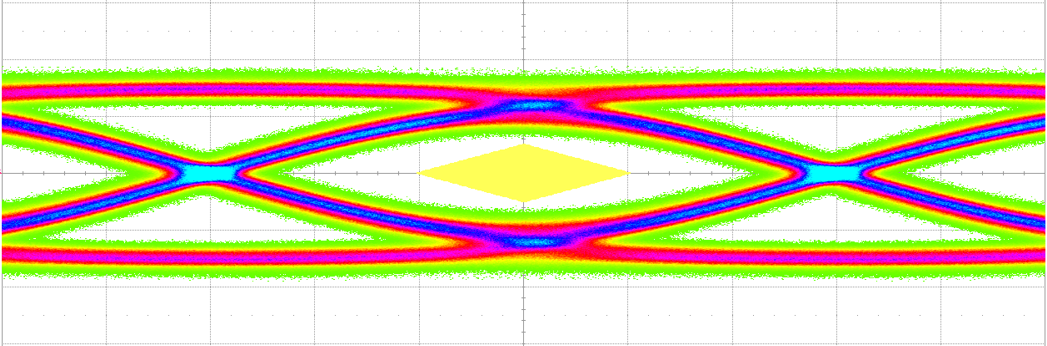

Figure 6-6 Super Speed Eye Diagram

Figure 6-6 Super Speed Eye Diagram

6.2.4 Layout

6.2.4.1 Layout Guidelines

6.2.4.1.1 High-Speed Differential Routing

- The high-speed differential pair (USB_DM and USB_DP) is connected to a type A USB connecter.

- The differential pair traces should be routed with 90 Ω ±15% differential impedance.

- The high-speed signal pair should be trace length matched.

- Max trace length mismatch between high speed USB signal pairs should be no greater than 150 mils.

- Keep total trace length to a minimum, if routing longer than eight inches contact TI to address signal integrity concerns.

- Route differential traces first.

- Route the differential pairs on the top or bottom layers with the minimum amount of vias possible.

- No termination or coupling caps are required.

- If a common mode choke is required then place the choke as close as possible to the USB connector signal pins.

- Likewise ESD clamps should also be placed as close as possible to the USB connector signal pins (closer than the choke).

- For more detailed information, refer to USB 2.0 Board Design and Layout Guidelines (SPRAAR7), which describes general PCB design and layout guidelines for the USB 2.0 differential pair (DP/DM).

6.2.4.1.2 SuperSpeed Differential Routing

- SuperSpeed consists of two differential routing pairs: a transmit pair (USB_SSTXM and USB_SSTXP) and a receive pair (USB_SSRXM and USB_SSRXP).

- Each differential pair trace must be routed with 90 Ω ±15% differential impedance.

- The high-speed signal pair must be trace-length matched. Maximum trace length mismatch between SuperSpeed USB signal pairs must be no greater than 5 mils. The total length for each differential pair can be no longer than eight inches, which is based on the SuperSpeed USB compliance channel specification and must be avoided if at all possible. TI recommends that the SuperSpeed differential pairs be as short as possible.

- The transmit differential pair does not have to be the same length as the receive differential pair. Keep total trace length to a minimum. Route differential traces first. Route the differential pairs on the top or bottom layers with the minimum amount of vias possible.

- The transmitter differential pair requires 0.1-µF coupling capacitors for proper operation. The package or case size of these capacitors must be no larger than 0402. C-packs are not allowed. The capacitors must be placed symmetrically as close as possible to the USB connector signal pins.

- If a common mode choke is required, place the choke as close as possible to the USB connector signal pins (closer than the transmitter capacitors).

- Likewise, ESD clamps must also be placed as close as possible to the USB connector signal pins (closer than the choke and transmitter capacitors).

- It is permissible to swap the plus and minus on either or both of the SuperSpeed differential pairs, which may be necessary to prevent the differential traces from crossing over one another. However, it is not permissible to swap the transmitter differential pair with the receive differential pair.

- It is recommended to use a 2010 pad for the inside pins, provided no pad is used for adjacent pins. Instead, use a pad on one of the inside pins for the next pad route the trace between the outer pins to a via. There is enough space to route a 3.78-mil trace between the outside pads while leaving 5-mil spacing between the trace and pad; it is then possible to increase the trace width to 4 mils after the breakout.

- In Figure 6-7 the red pads are USB_SS_RXP/USB_SS_RXN and the blue pads are USB_SS_TXP/USB_SS_TXN.

6.2.4.2 Layout Example

Figure 6-7 Layout Example

Figure 6-7 Layout Example

6.3 Power Supply Recommendations

6.3.1 1.1-V and 1.8-V Digital Supply

The TUSB1310A requires 1.1-V and 1.8-V digital power sources. Both VDD1P1 and VDD1P8 supplies must have 0.1-μF bypass capacitors to VSS (ground) in order for proper operation. The recommendation is one capacitor for each power terminal. Place the capacitor as close as possible to the terminal on the device and keep trace length to a minimum. Smaller value capacitors like 0.01-μF are also recommended on the digital supply terminals. When placing and connecting all bypass capacitors, high-speed board design rules must be followed.

6.3.2 1.1-V, 1.8-V and 3.3-V Analog Supplies

Because circuit noise on the analog power terminals must be minimized, a Pi-type filter is recommended for each supply. Analog power terminals must have a 0.1-μF bypass capacitor connected to VSSA (ground) for proper operation. Place the capacitor as close as possible to the terminal on the device and keep trace length to a minimum. Smaller value capacitors (0.01-μF) are also recommended on the analog supply terminals.

6.3.3 Capacitor Selection Recommendations

When selecting bypass capacitors for the TUSB1310A device, X7R-type capacitors are recommended. The frequency versus impedance curves, quality, stability, and cost of these capacitors make them a logical choice for most computer systems.

The selection of bulk capacitors with low-ESR specifications is recommended to minimize low frequency power supply noise. Today, the best low-ESR bulk capacitors are radial leaded aluminum electrolytic capacitors. These capacitors typically have ESR specifications that are less than 0.01 Ω at 100 kHz. Also, several manufacturers sell D-size surface mount specialty polymer solid aluminum electrolytic capacitors with ESR specifications slightly higher than 0.01 Ω at 100 kHz. Both of these bulk capacitor options significantly reduce low frequency power supply noise and ripple.