JAJSS81I September 2008 – November 2023 UCC27423-Q1 , UCC27424-Q1 , UCC27425-Q1

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Device Comparison Table

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Revision History

- 13Mechanical, Packaging, and Orderable Information

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

サーマルパッド・メカニカル・データ

- DGN|8

発注情報

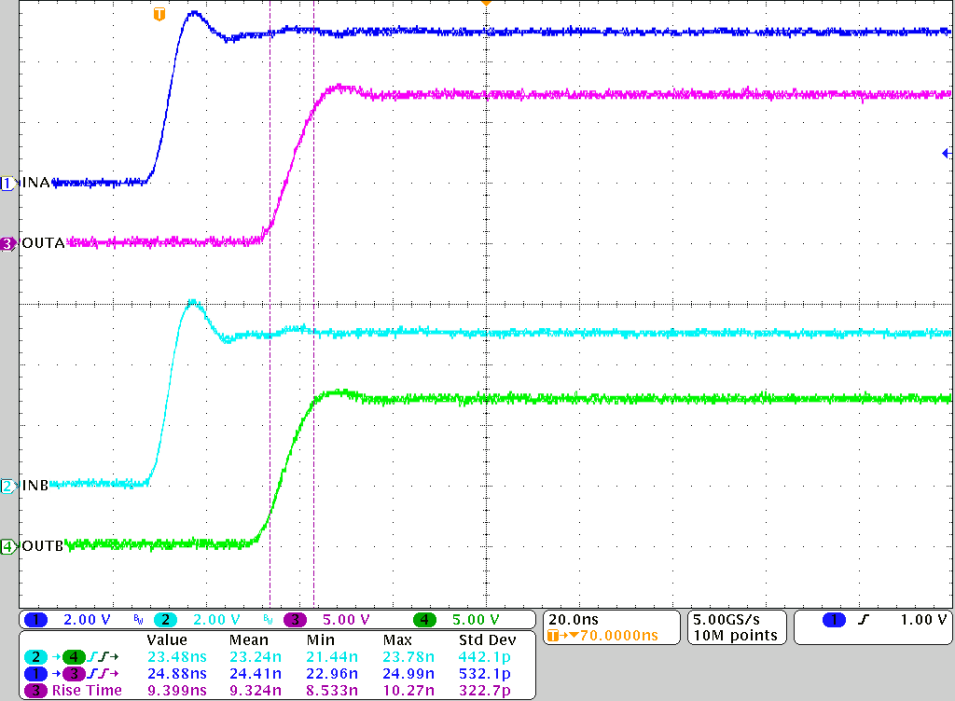

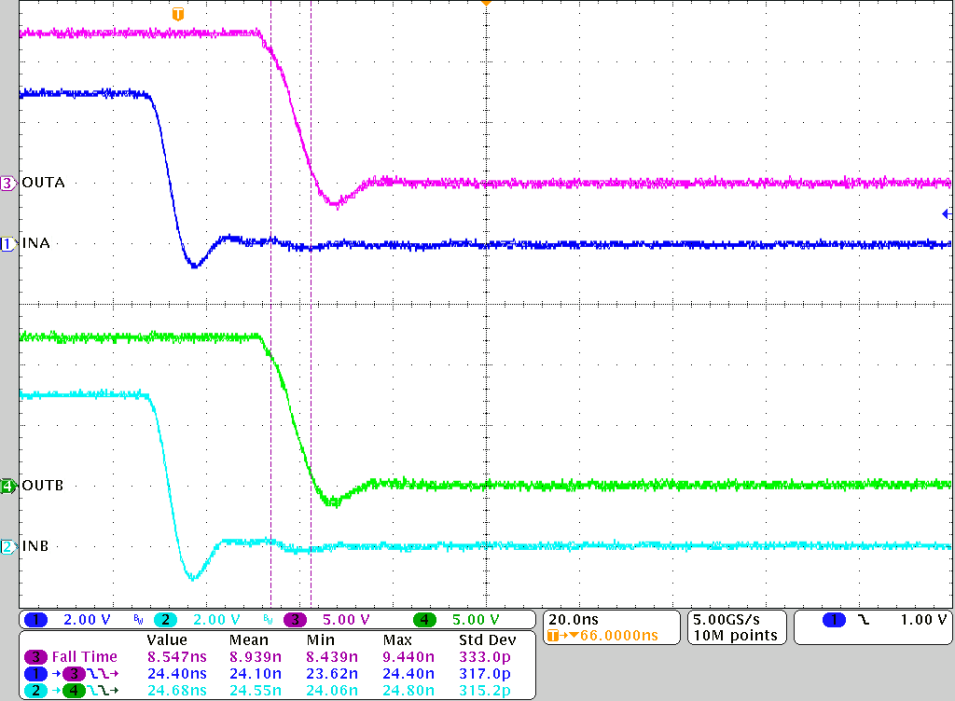

8.2.3 Application Curves

Figure 8-4 and Figure 8-5 show rising and falling time and turnon and turnoff propagation delay testing waveform in room temperature for UCC27424-Q1, and waveform measurement data (see the bottom part of the waveform). Each channel, INA/INB/OUTA/OUTB, is labeled and displayed on the left hand of the waveforms.

The load capacitance testing condition is 1.8 nF, VDD = 12 V, and f = 300 kHz.

HI and LI share one same input from function generator; therefore, besides the propagation delay and rising or falling time, the difference of the propagation delay between HO and LO gives the propagation delay matching data.

Note the linear rise and fall edges of the switching waveforms. This is due to the constant output current characteristic of the driver as opposed to the resistive output impedance of traditional MOSFET-based gate drivers.