JAJSHT1G December 2009 – November 2022 UCC28C40-Q1 , UCC28C41-Q1 , UCC28C42-Q1 , UCC28C43-Q1 , UCC28C44-Q1 , UCC28C45-Q1

PRODUCTION DATA

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Revision History

- 5 Device Comparison Table

- 6 Pin Configuration and Functions

- 7 Specifications

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3 Feature Description

- 8.4 Device Functional Modes

-

9 Application and Implementation

- 9.1 Application Information

- 9.2

Typical Application

- 9.2.1 Design Requirements

- 9.2.2

Detailed Design Procedure

- 9.2.2.1 Custom Design With WEBENCH® Tools

- 9.2.2.2 Input Bulk Capacitor and Minimum Bulk Voltage

- 9.2.2.3 Transformer Turns Ratio and Maximum Duty CycleG

- 9.2.2.4 Transformer Inductance and Peak Currents

- 9.2.2.5 Output Capacitor

- 9.2.2.6 Current Sensing Network

- 9.2.2.7 Gate Drive Resistor

- 9.2.2.8 VREF Capacitor

- 9.2.2.9 RT/CT

- 9.2.2.10 Start-Up Circuit

- 9.2.2.11 Voltage Feedback Compensation

- 9.2.3 Application Curves

- 9.2.4 Power Supply Recommendations

- 9.2.5 Layout

- 10Device and Documentation Support

- 11Mechanical, Packaging, and Orderable Information

9.2.3 Application Curves

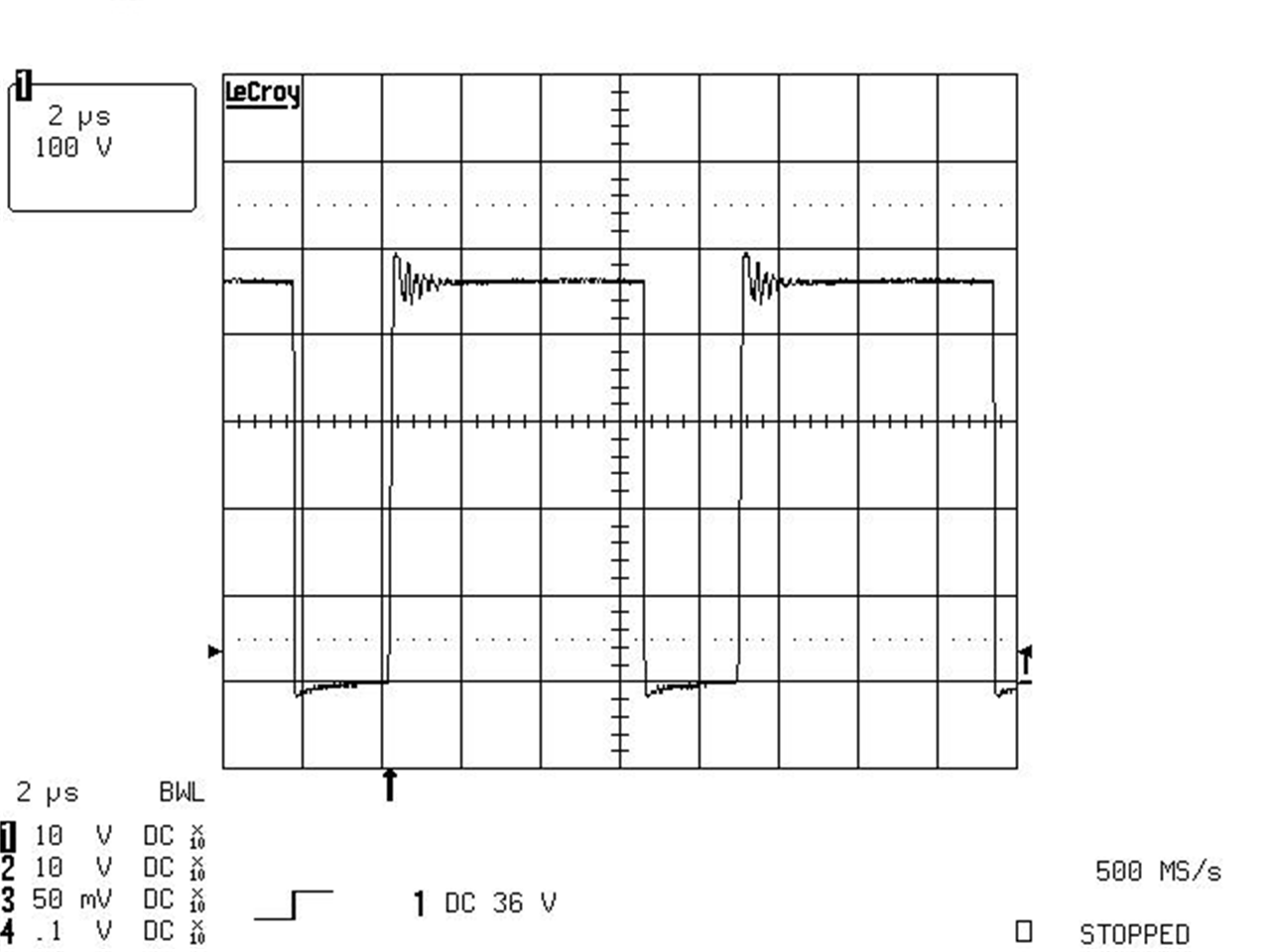

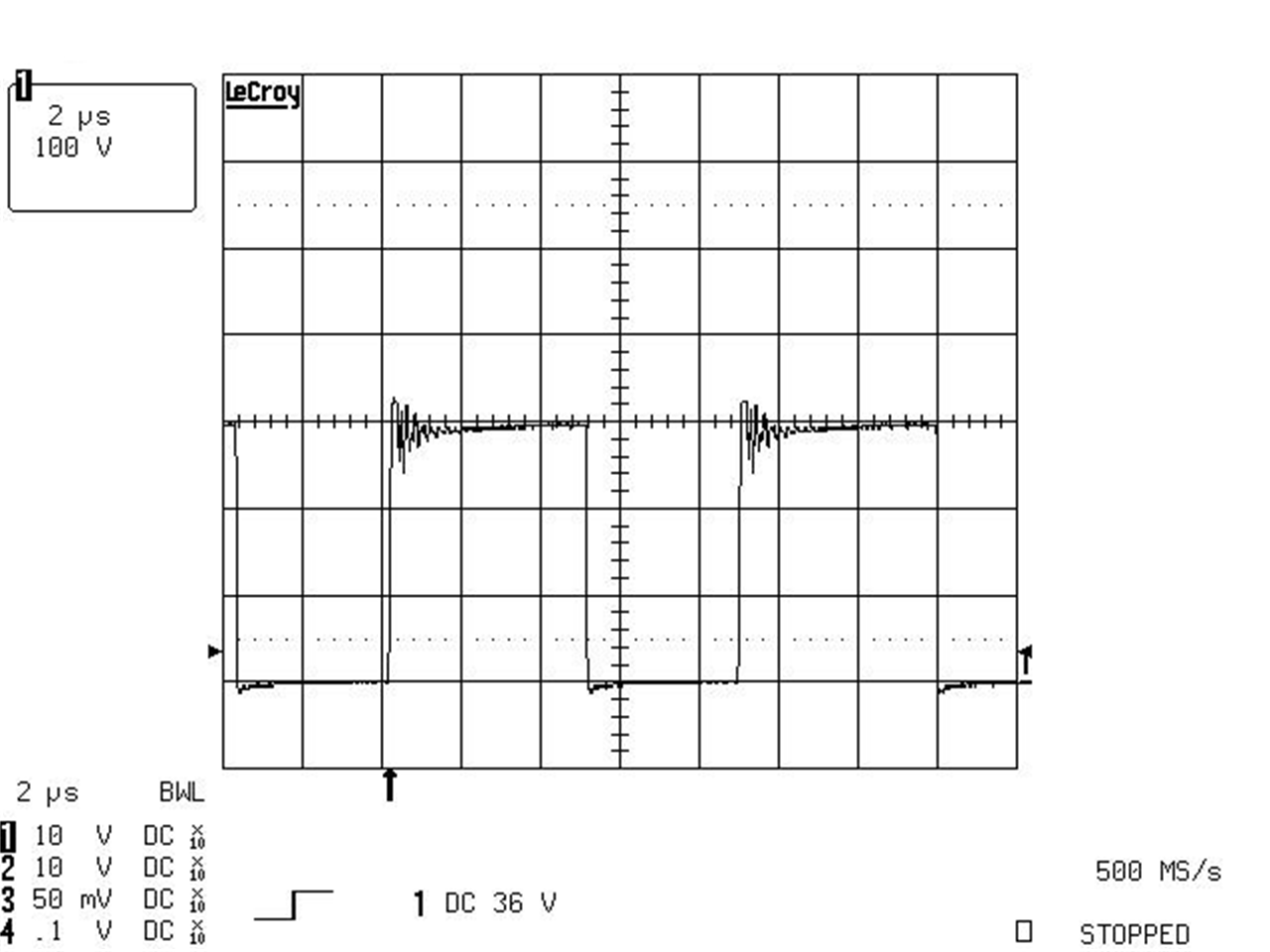

Figure 9-7 Primary Side MOSFET Drain to Source Voltage at 240-V AC Input (100 V/div)

Figure 9-7 Primary Side MOSFET Drain to Source Voltage at 240-V AC Input (100 V/div)

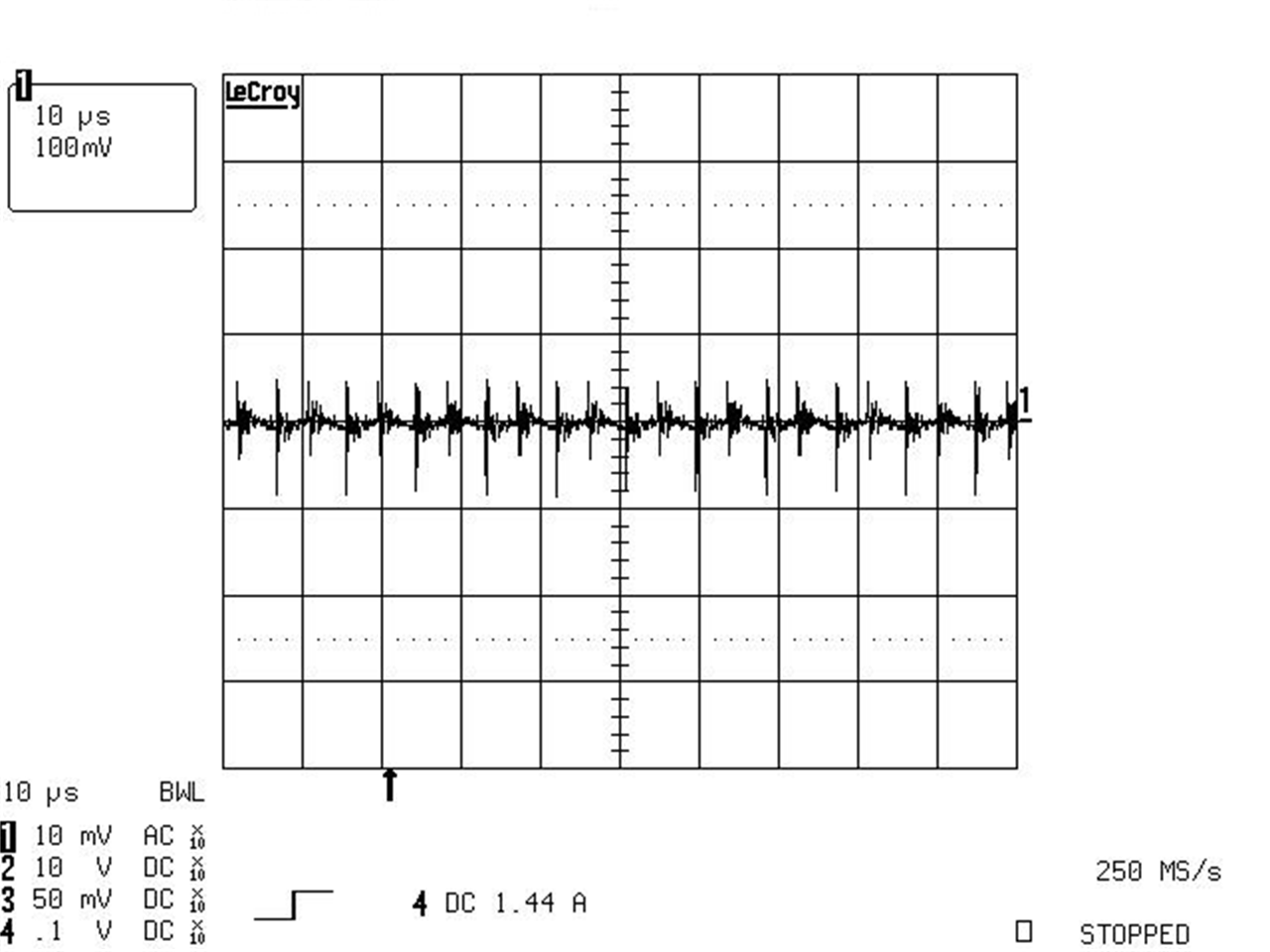

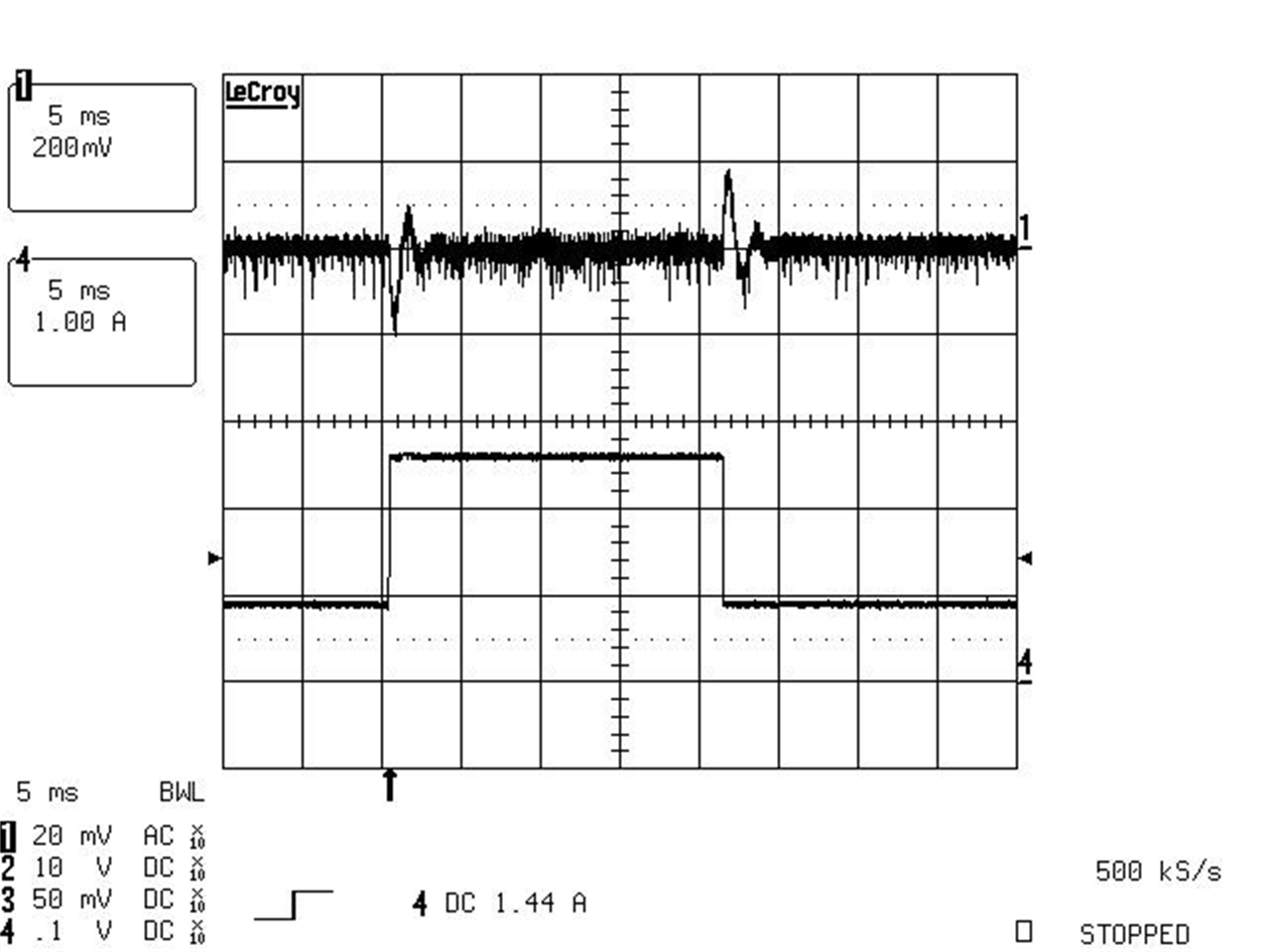

| CH1: Output Voltage AC Coupled, 200 mV/div |

| CH4: Output Current, 1 A/div |

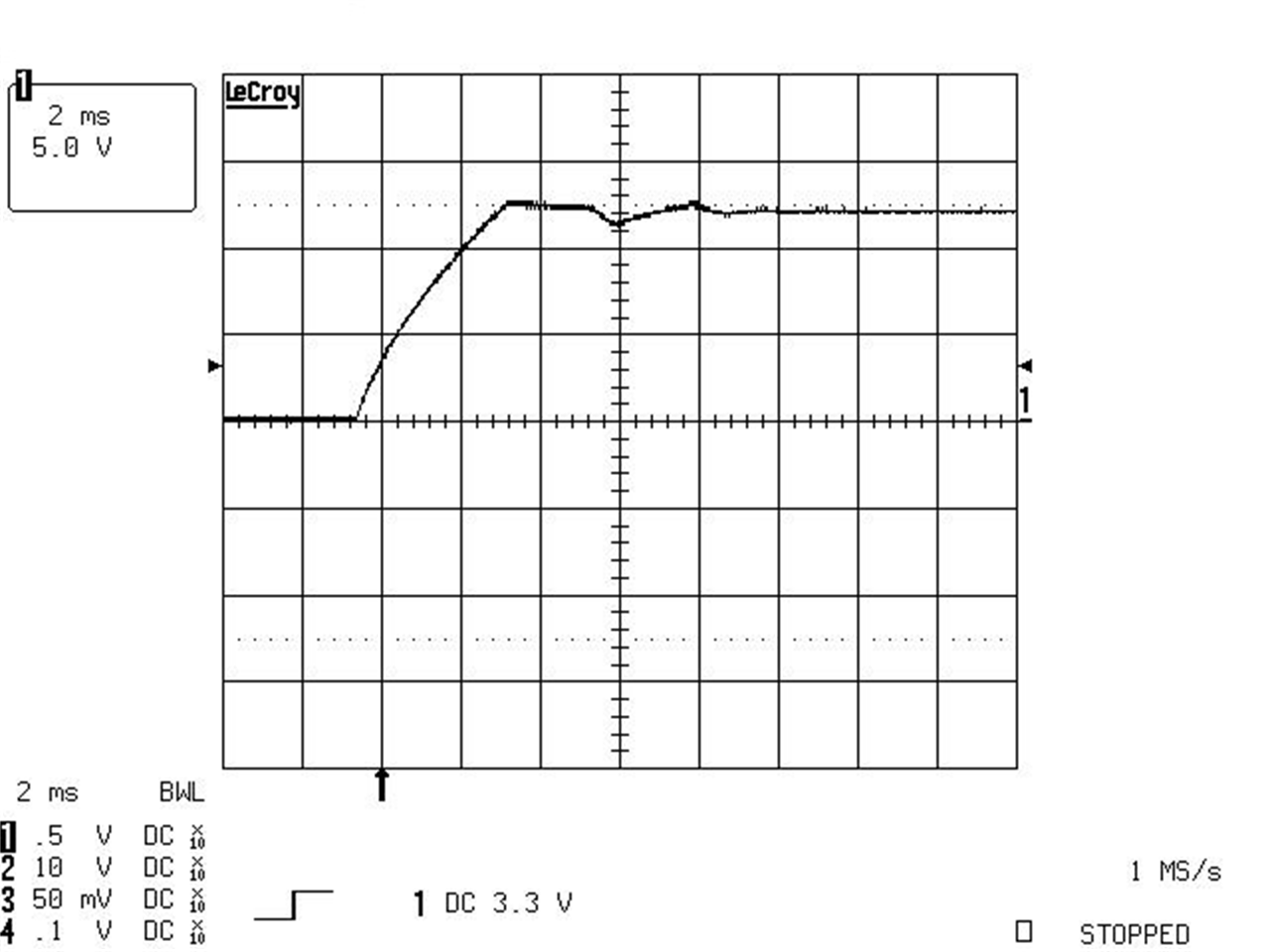

Figure 9-11 Output Voltage Behavior at Full Load Start-up (5 V/div)

Figure 9-11 Output Voltage Behavior at Full Load Start-up (5 V/div) Figure 9-8 Primary Side MOSFET Drain to Source Voltage at 120-V AC Input (100 V/div)

Figure 9-8 Primary Side MOSFET Drain to Source Voltage at 120-V AC Input (100 V/div)