JAJSGX5C july 2018 – april 2023 BQ25150

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Revision History

- 5 概要 (続き)

- 6 Device Key Default Settings

- 7 Pin Configuration and Functions

- 8 Specifications

-

9 Detailed Description

- 9.1 Overview

- 9.2 Functional Block Diagram

- 9.3

Feature Description

- 9.3.1 Linear Charger and Power Path

- 9.3.2 Protection Mechanisms

- 9.3.3 ADC

- 9.3.4 VDD LDO

- 9.3.5 Load Switch / LDO Output and Control

- 9.3.6 PMID Power Control

- 9.3.7 MR Wake and Reset Input

- 9.3.8 14-Second Watchdog for HW Reset

- 9.3.9 Faults Conditions and Interrupts ( INT)

- 9.3.10 Power Good ( PG) Pin

- 9.3.11 External NTC Monitoring (TS)

- 9.3.12 External NTC Monitoring (ADCIN)

- 9.3.13 I2C Interface

- 9.4 Device Functional Modes

- 9.5 Register Map

- 10Application and Implementation

- 11Power Supply Recommendations

- 12Layout

- 13Device and Documentation Support

- 14Mechanical, Packaging, and Orderable Information

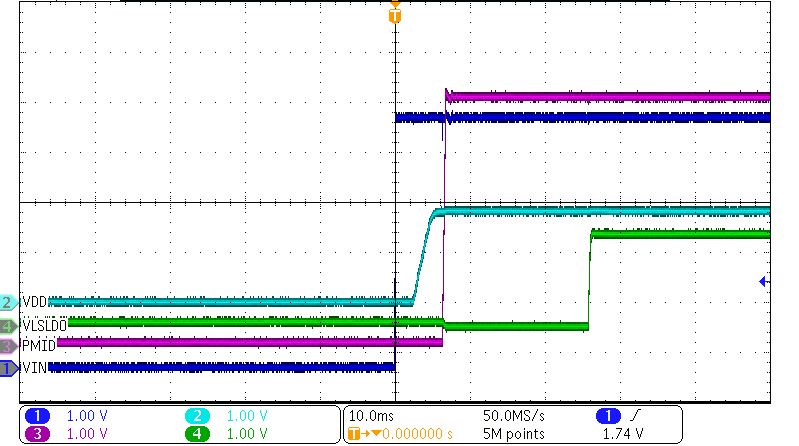

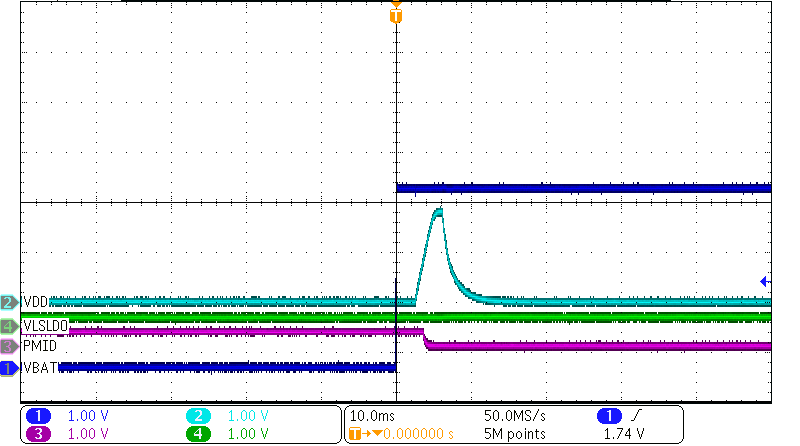

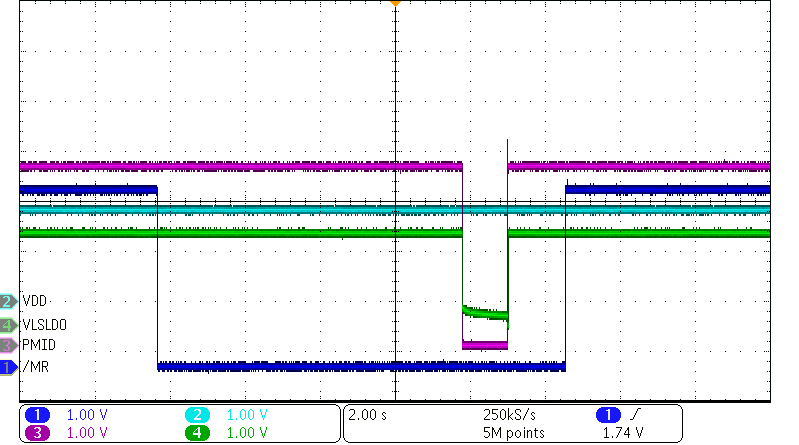

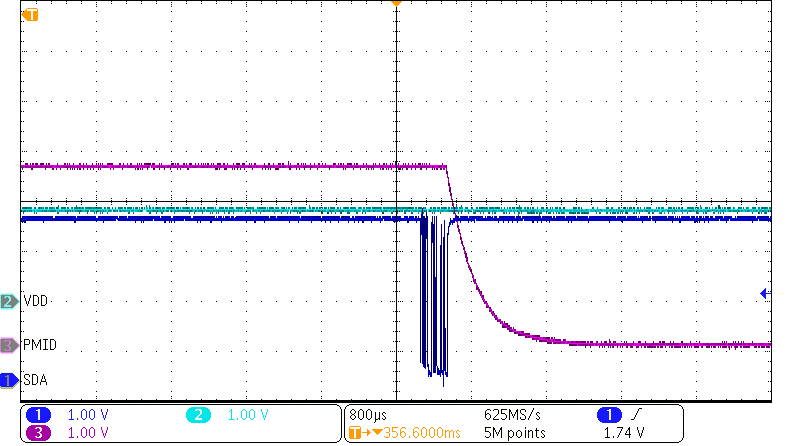

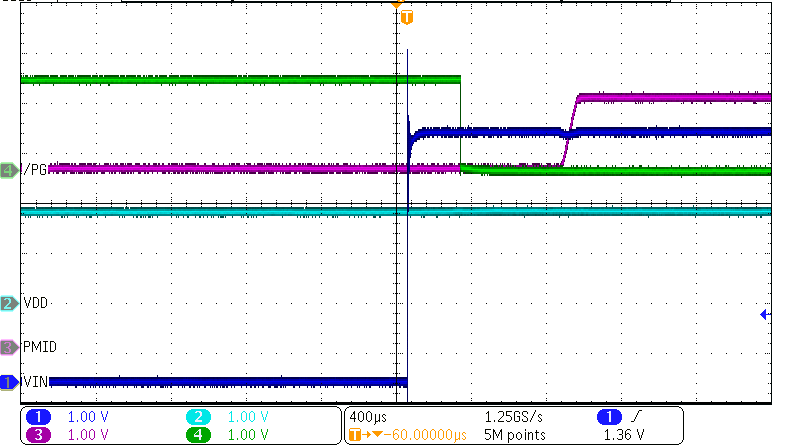

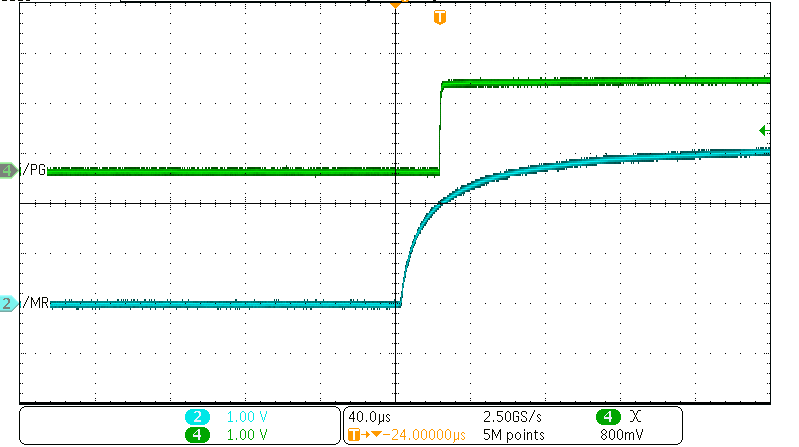

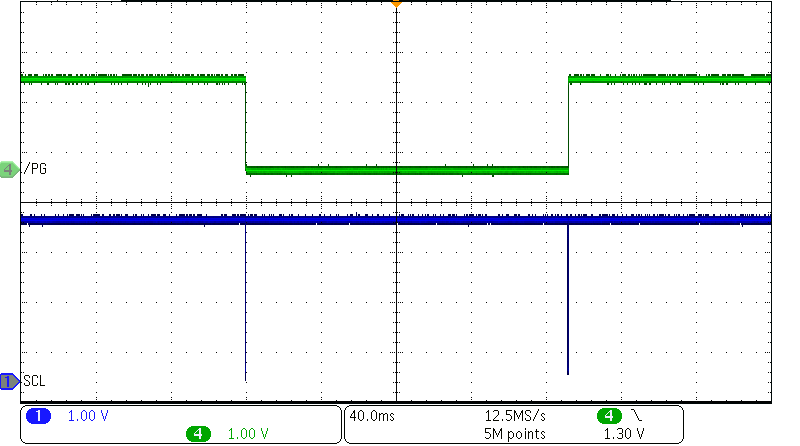

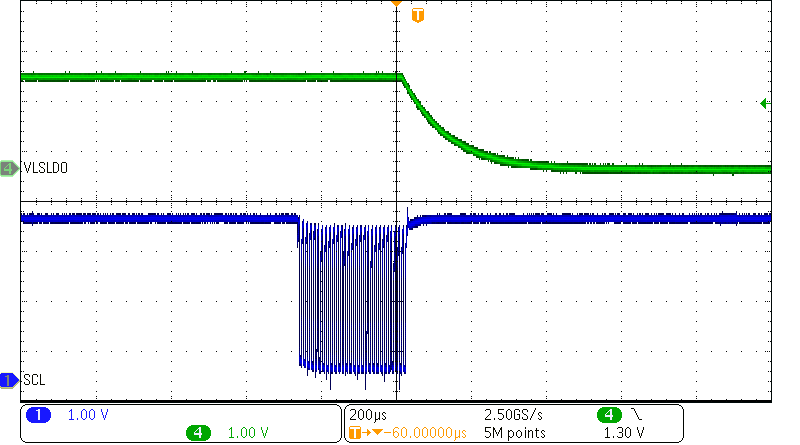

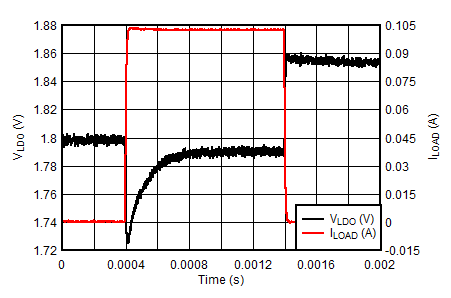

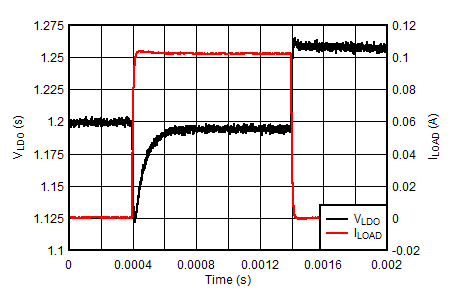

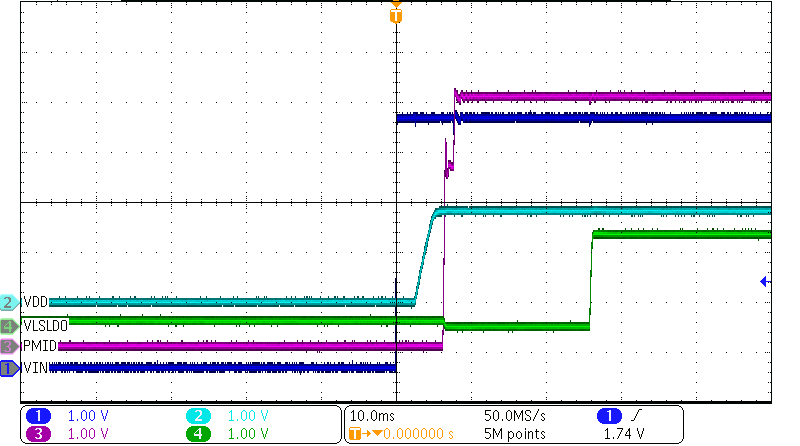

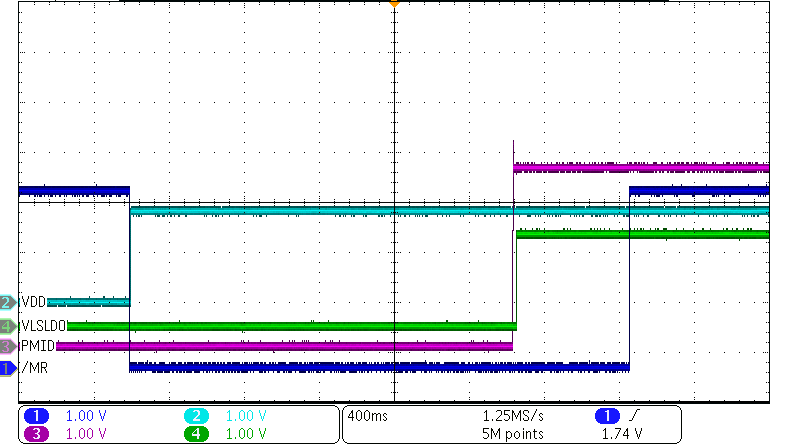

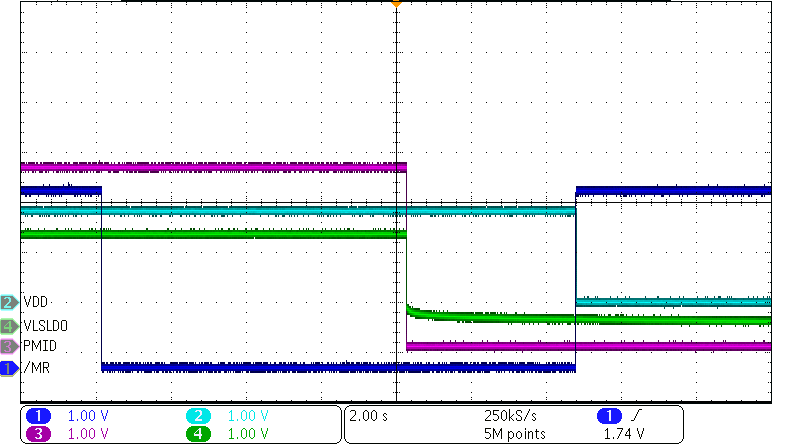

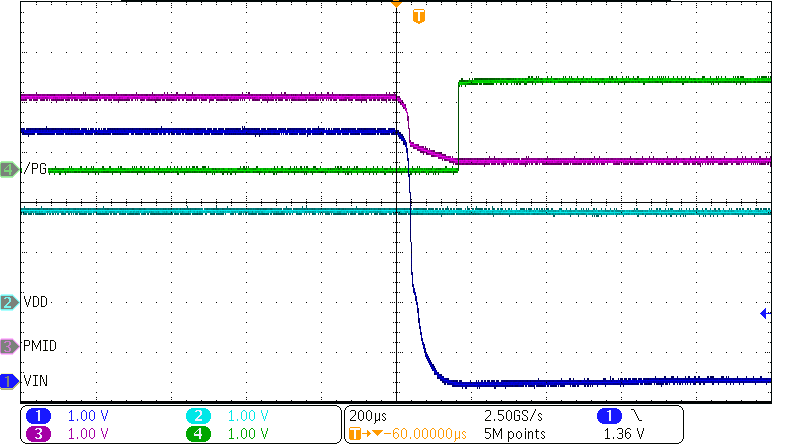

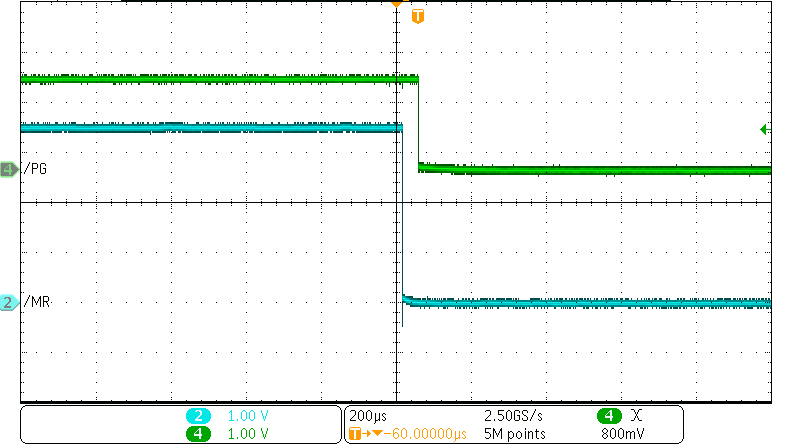

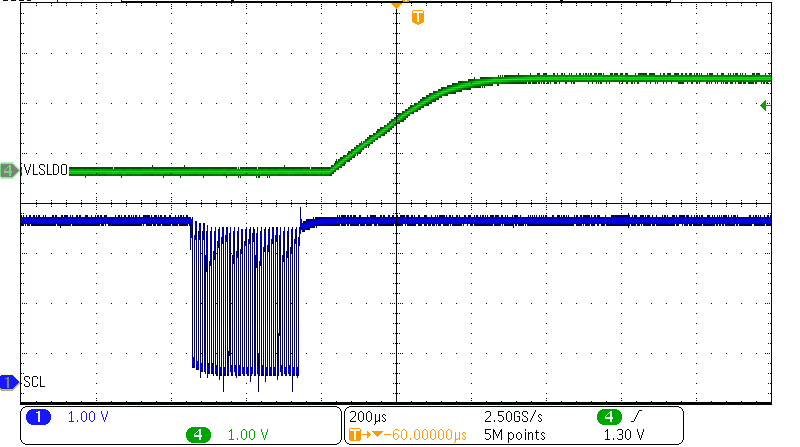

10.2.3 Application Curves

| VIN = 5 V | VBAT = 0 V |

| VIN = 0 V | VBAT = 3.6 V |

| VIN = 0 V | VBAT = 3.6 V |

| VIN = 0 V | VBAT = 3.6 V |

| VIN = 5 V | VBAT = 3.6 V |

| VIN = 5 V | VBAT = 3.6 V |

| VBAT = 3.6 V |

| VBAT = 3.6 V | No load | |

| VIN = 0 V | VBAT = 2.4 V | VINLS = VPMID |

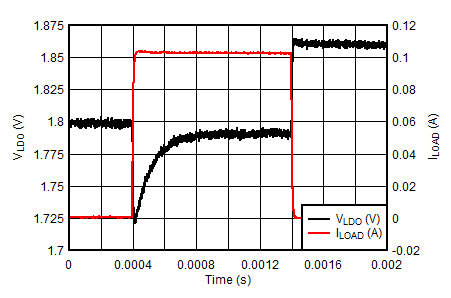

| VIN = 0 V | VBAT = 3.6 V | VINLS = VPMID |

| VIN = 5 V | VBAT = 3.6 V |

| VIN = 0 V | VBAT = 3.6 V |

| VIN = 0 V | VBAT = 3.6 V | LBPRESS_ACTION = 01 |

| VIN = 5 V | VBAT = 3.6 V | SHIPMODE_EN = 1 |

| VIN = 5 V | VBAT = 3.6 V |

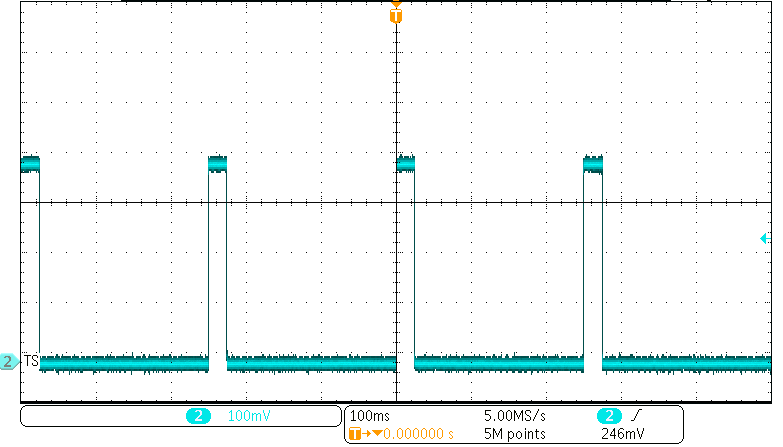

| VBAT = 3.6 V |

| VBAT = 3.6 V | No load |

| VIN = 0 V | VBAT = 3.6 V | VINLS = VPMID |

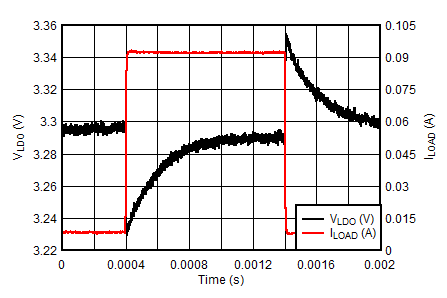

| VIN = 0 V | VBAT = 3.8 V | VINLS = VPMID |

| VIN = 5V |