JAJU881 December 2022

4.2.1 Virtual Antenna Array

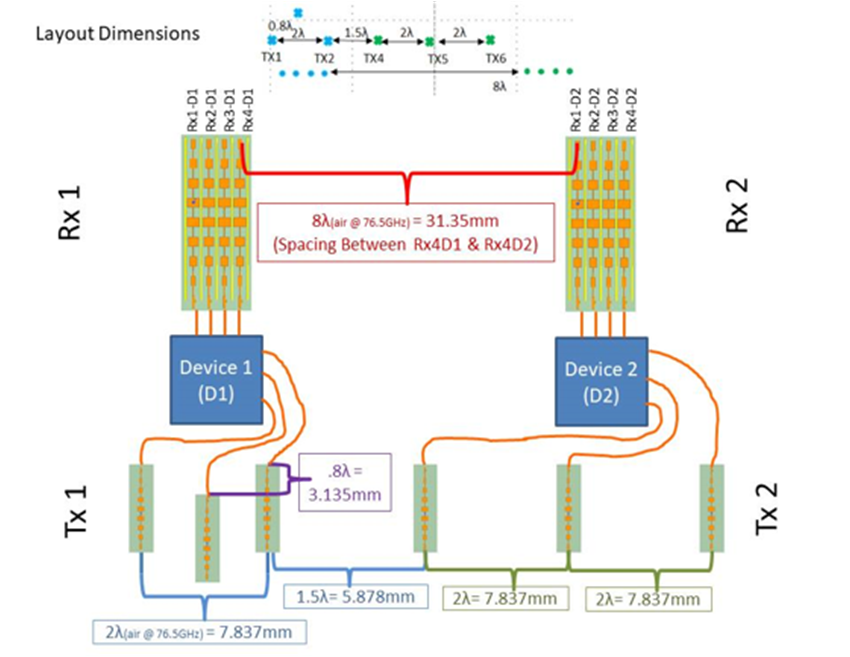

The two-chip cascade EVM consists of 6-TX channels and 8-RX channels as shown in Figure 4-1 giving a total number of 48 virtual channels in the MIMO virtual array. The arrangement of the channels is shown in Figure 4-2 where the MIMO array gives an aperture limited angle resolution of about 3 deg in the azimuth direction.

The antenna element design is shown in Figure 4-1.

Figure 4-1 TX and RX Channel

Spacings

Figure 4-1 TX and RX Channel

Spacings

Figure 4-2 MIMO Virtual Array