SLAU776A May 2018 – December 2023 ADC12DL2500 , ADC12DL3200

- 1

- Abstract

- Trademarks

- 1Introduction

- 2Equipment

-

3Setup Procedure

- 3.1 Install the High Speed Data Converter (HSDC) Pro Software

- 3.2 Install the Configuration GUI Software

- 3.3 Connect the EVM and TSW14DL3200EVM

- 3.4 Connect the Power Supplies to the Boards (Power Off)

- 3.5 Connect the Signal Generators to the EVM (*RF Outputs Disabled Until Directed)

- 3.6 Turn On the TSW14DL3200EVM Power and Connect to the PC

- 3.7 Turn On the ADC12DLXX00EVM 5-V Power Supply and Connect to the PC

- 3.8 Turn On the Signal Generator RF Outputs

- 3.9 Open the ADC12DLXX00EVM GUI and Program the ADC and Clocks

- 3.10 Calibrate the ADC Device on the EVM

- 3.11 Open the HSDC Software and Load the FPGA Image to the TSW14DL3200EVM

- 3.12 Capture Data Using the HSDC Pro Software

- 4Device Configuration

- A Troubleshooting the ADC12DL3200EVM

- B Optional ADC12DL3200EVM Configurations

- C Revision History

B Optional ADC12DL3200EVM Configurations

This appendix provides settings for modifying the EVM for optional clocking support.

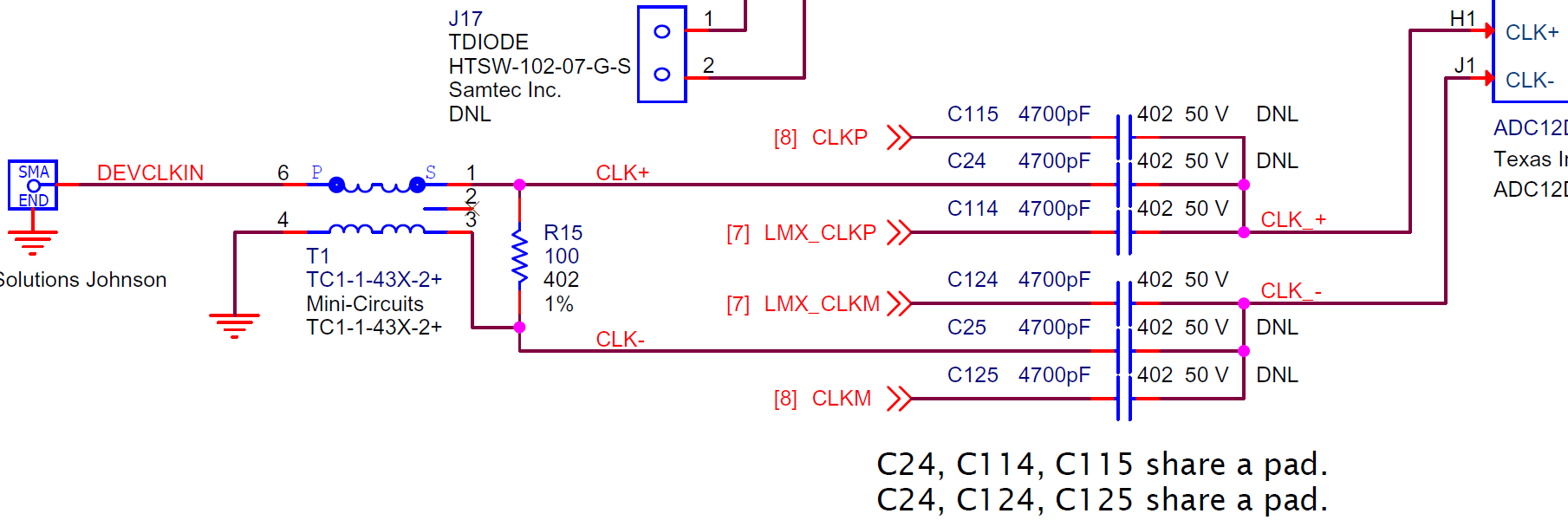

The LMK04828 provides a buffered copy of the onboard 100-MHz VCXO to the LMX2582. When the optional 10-MHz reference clock is connected, the 100-MHz VCXO output is frequency locked to the 10-MHz reference. This process enables coherent sampling of the analog input signal. The EVM can be configured to use an external ADC clock with the following steps (see Figure 6-1):

- Modify the hardware:

- Remove C114 and C124, populate C24 and C25.

- Connect the signal generators:

- Connect the 10-MHz reference from Sig Gen 1 to Sig Gen 2.

- Configure Sig Gen 2 to use the 10-MHz reference input from Sig Gen 1.

- Sig Gen 1 connects to DEVCLK (J12). Set to the generator frequency to the desired FCLK. Set output level to +9 dBm.

- Sig Gen 2 connects to the desired analog input with output level at 0 dBm for the starting point.

- Program the GUI:

- In the EVM tab, set the clock source to External.

- Enter the Sampling Frequency (FCLK) in step 2b.

Figure B-1 External CLK

Configuration

Figure B-1 External CLK

ConfigurationThe ADC12DL3200EVM includes a reference clock input (CLKIN0) that allows the user to sync the LMK04828 to an external 10-MHz reference allowing for coherent sampling

The LMX2582 and LMK04828 may be reconfigured to exercise more features, but this EVM is not intended to be a full evaluation platform for these devices. For a full evaluation platform, see the LMK04828 tool folder and LMX2582 tool folder.