SLVAFI8 February 2023 TLC6C5748-Q1

- Abstract

- Trademarks

- 1Introduction

-

2Design Considerations for Low EMI

- 2.1 Design Considerations Overview

- 2.2

Considerations in Detail

- 2.2.1 Top-Level Architecture

- 2.2.2

High Frequency Signals

- 2.2.2.1 Original Setup

- 2.2.2.2 3.3 V I/O Voltage Instead of 5 V

- 2.2.2.3 Use Independent OSC for GSCLK With Spread Spectrum

- 2.2.2.4 Without Using Buffer on GSCLK

- 2.2.2.5 Using Snubber on GSCLK

- 2.2.2.6 Lower the Signal Frequency

- 2.2.2.7 Placement and PCB layout

- 2.2.2.8 ESD Enhancement

- 2.2.2.9 Demo and Test Results

- 2.2.2.10 Bench Test Results

- 3Summary

- 4References

2.2.2.5 Using Snubber on GSCLK

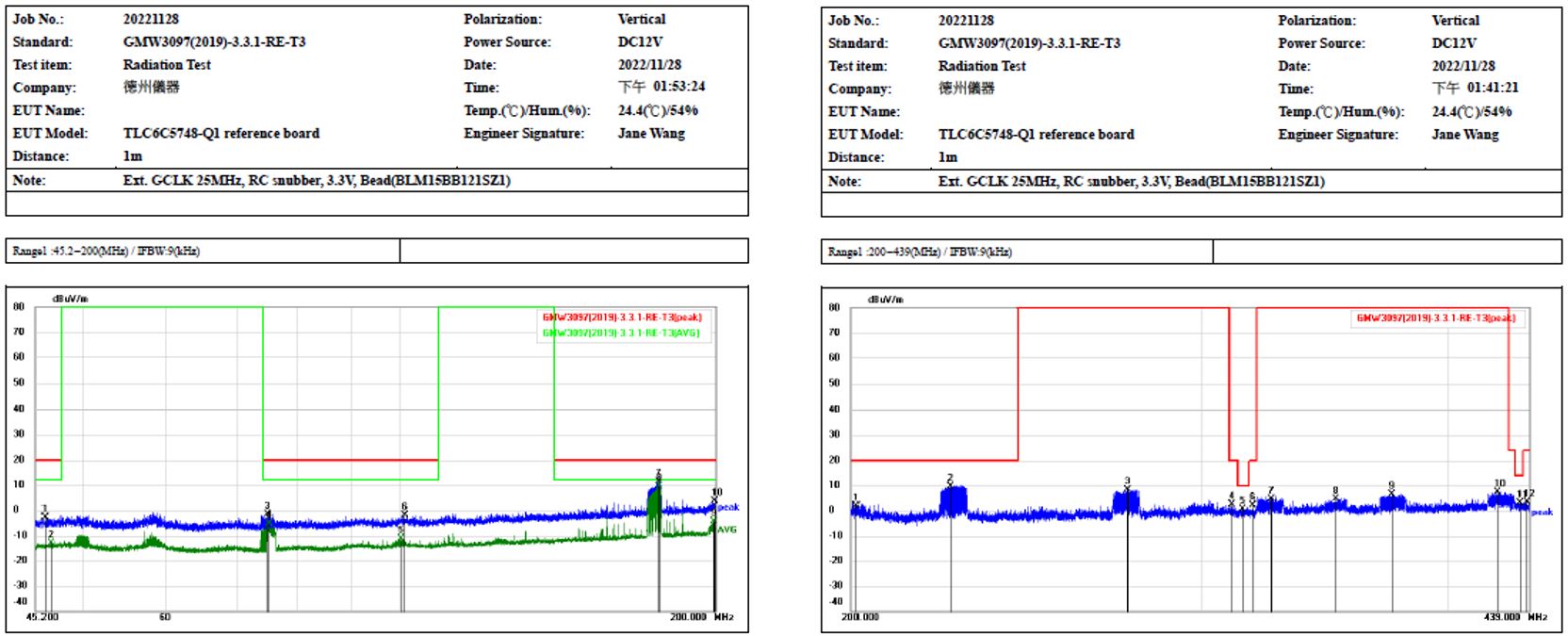

In the basis of previous section, #FIG_XJS_JLL_FWB shows test results adding snubber on GSCLK.

Figure 2-7 Test Results of Using 3.3V IO

Voltage Setup, GSCLK with SSC and Add Snubber on GCLK (Vertical Direction) from

45MHz to 439MHz

Figure 2-7 Test Results of Using 3.3V IO

Voltage Setup, GSCLK with SSC and Add Snubber on GCLK (Vertical Direction) from

45MHz to 439MHz