SLVAFR4 February 2024 TPS25762-Q1 , TPS25763-Q1 , TPS25772-Q1

4.5 SPT.7 PPS Current Limit Test

The PPS Current Foldback Test verifies that when a source port makes a contract using an APDO and current reaches Operating Current level, the output follows the tolerance requirements from USB PD spec 7.1.4.2. Please timely check latest PD spec and PD CTS upon USBIF official website. USBIF updates specs occasionally which are crucial for certification test reference. USBIF relaxes the current limit test range recently. The key parameters is iPpsCLNew (-150mA, 150mA) and slew rate of current step (iPpsCLLoadReleaseRate, iPpsCLLoadStepRate). In practice, output capacitors influence heavily on this test item. TI suggests customer to strictly follow capacitance values IC provider rules. The test procedures refer to ‘Universal Serial Bus Type-C and Power Delivery Source Power Requirements Test Specification’. Look up the test manual, Total-phase data log and QuadView data log as debug failures.

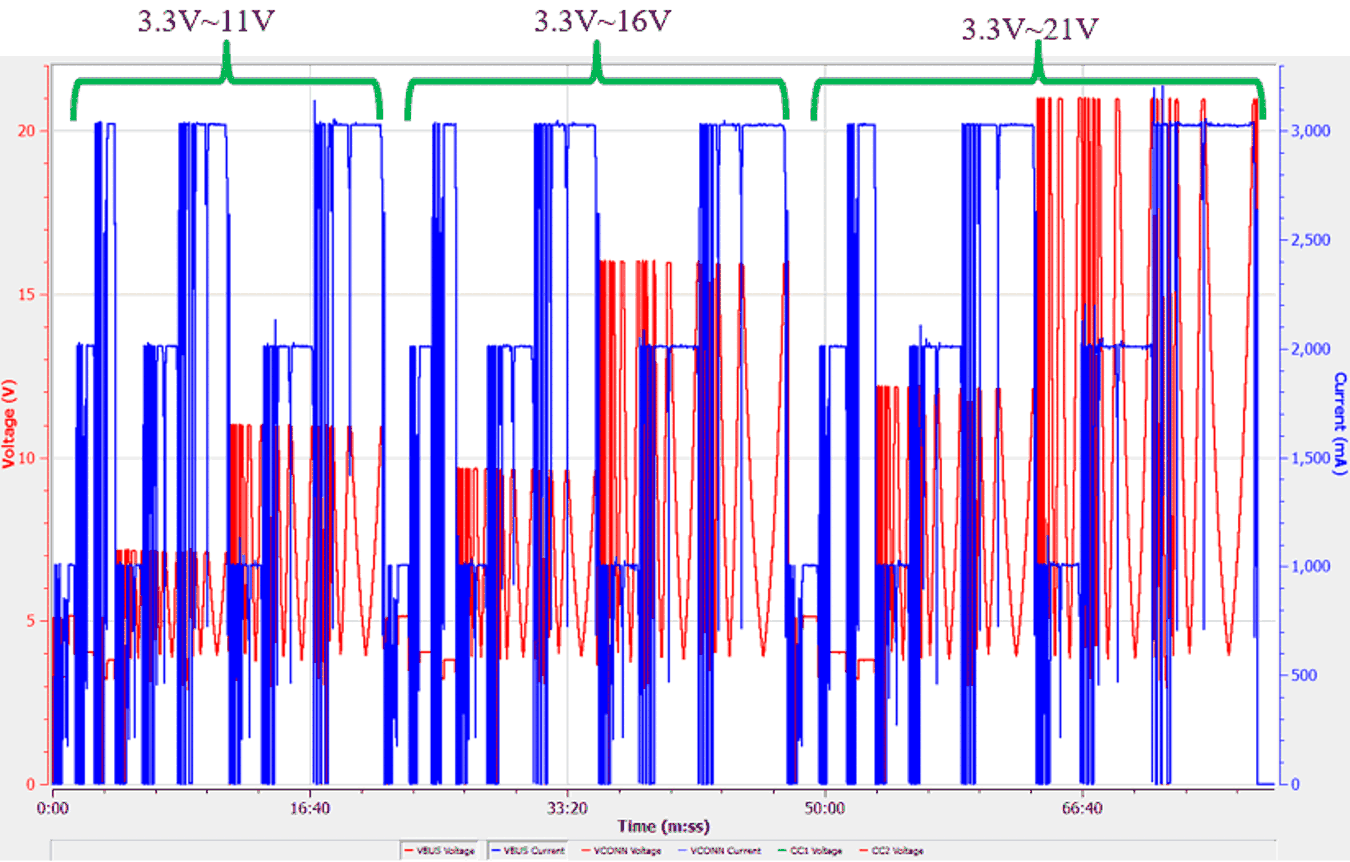

Figure 4-8 is SPT.7 test log extracted by total-phase analyzer. The tester runs 3 APDOs, 3.3V~11V, 3.3V~16V, 3.3V~21V. Customer’s requirements determine how many APDOs need to be tested. Test procedures C, D, E rules RDO currents, voltages and steps resolution to test.

Figure 4-8 SPT.7 Total-Phase Analyzer Data Log

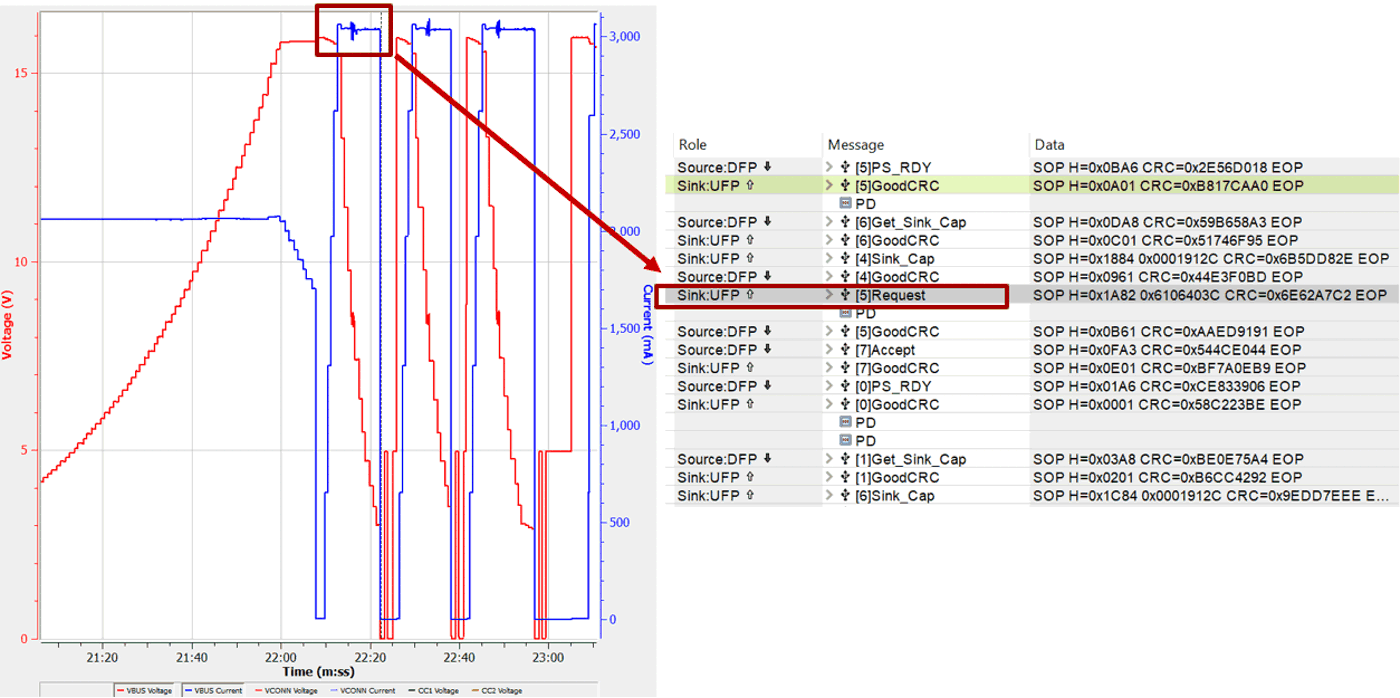

Figure 4-8 SPT.7 Total-Phase Analyzer Data Log Figure 4-9 SPT.7 Failure Data Log

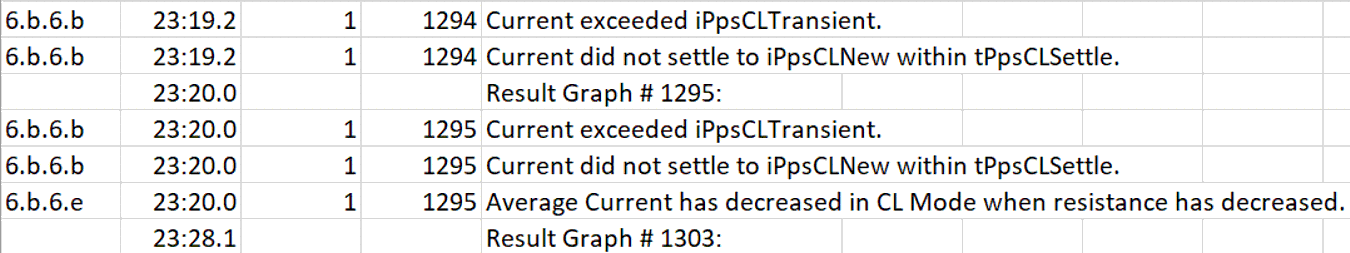

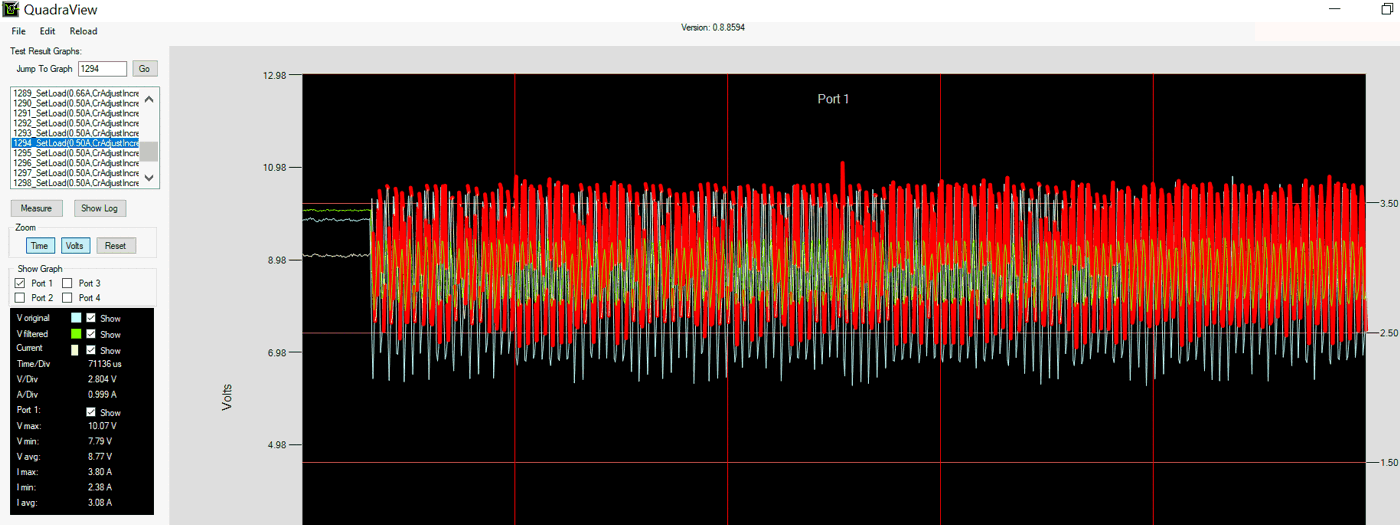

Figure 4-9 SPT.7 Failure Data Log Based on .cvs log, search image #1294 by QuadView shown in Figure 4-10 and clearly displays oscillation as increase current by 500mA step. Also check Total-phase data log depicted in Figure 4-11 for more information. Similar oscillation occurs. But the protocol negotiation is normal. So try to figure out some methods to stabilize current, such as increasing capacitance around BUS pin, or check filtering circuit of current limit loop. For most current limit test, simply increase BUS capacitance being able to solve several failures.

Figure 4-10 QuadView Data Log of SPT.7

Figure 4-10 QuadView Data Log of SPT.7 Figure 4-11 Total-Phase Data Log of SPT.7

Figure 4-11 Total-Phase Data Log of SPT.7