SLVUCS1A july 2023 – august 2023

3.1.5 Overcurrent Protection

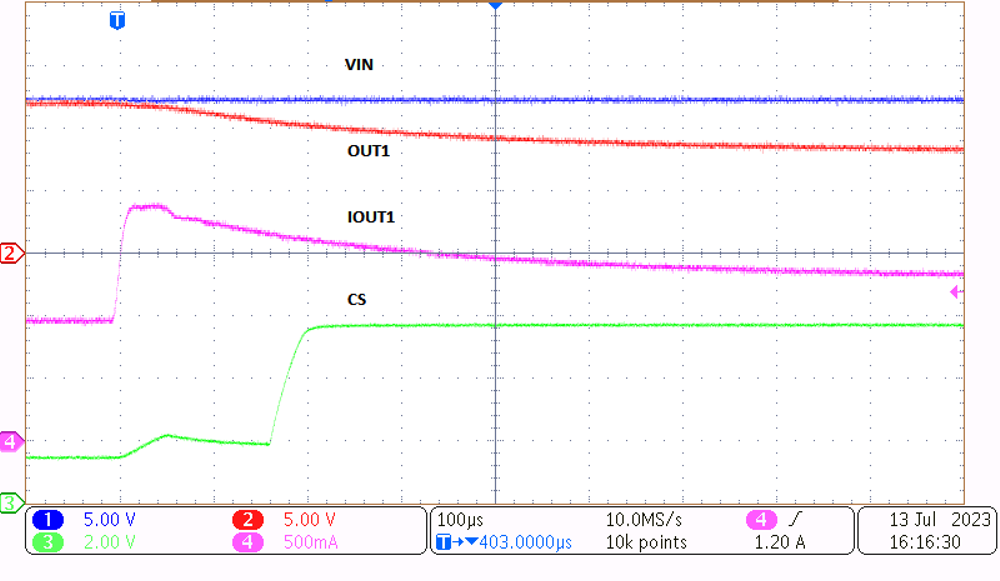

Figure 3-7 OCP Assertion at RLoad = 6 Ω

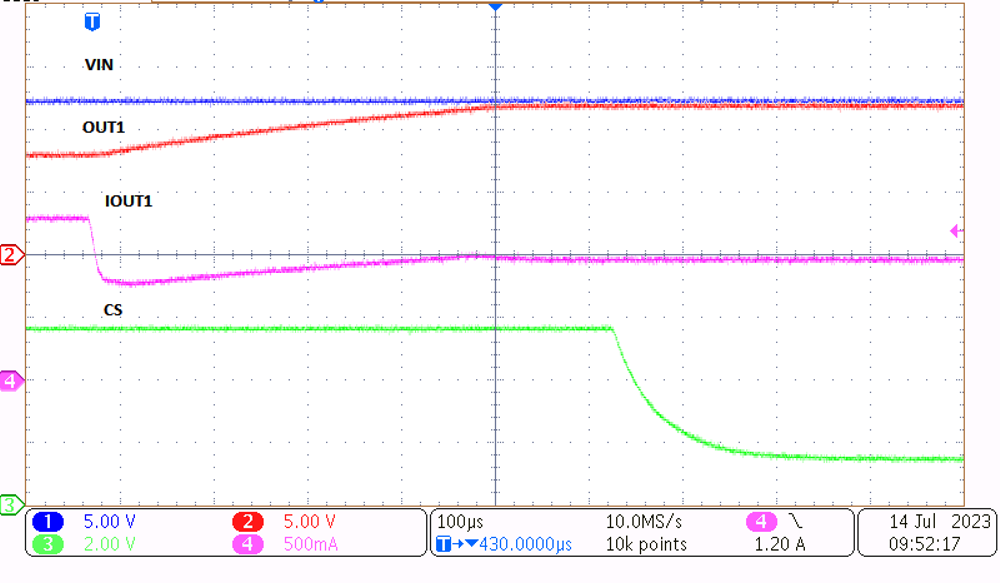

Figure 3-7 OCP Assertion at RLoad = 6 Ω Figure 3-8 OCP Deassertion by returning RLoad = 12 Ω

Figure 3-8 OCP Deassertion by returning RLoad = 12 ΩBoth tests were performed using VIN = 12 V, and a load between 6 Ω and 12 Ω.

SLVUCS1A july 2023 – august 2023

Figure 3-7 OCP Assertion at RLoad = 6 Ω

Figure 3-7 OCP Assertion at RLoad = 6 Ω Figure 3-8 OCP Deassertion by returning RLoad = 12 Ω

Figure 3-8 OCP Deassertion by returning RLoad = 12 ΩBoth tests were performed using VIN = 12 V, and a load between 6 Ω and 12 Ω.