SPRACV3 December 2020 AM6412 , AM6422 , AM6442

- Trademarks

- 1Simulations

-

2Models

- 2.1 IBIS-AMI Model Kit

- 2.2 The Kit Structure

- 2.3 Contents of the Kit

- 2.4 IBIS Analog Models

- 2.5

Algorithmic Models

- 2.5.1

Transmitter (Tx) Model

- 2.5.1.1 TX AMI Parameters for Gen 1

- 2.5.1.2 TX AMI Parameters for Gen 2

- 2.5.1.3 TX AMI Parameters for Gen 3

- 2.5.1.4 TX AMI Parameters for Sgmii

- 2.5.1.5 TX AMI Parameters for Qsgmii

- 2.5.1.6 TX AMI Parameters for USB3.0

- 2.5.1.7 TX AMI Parameters for USB3.1

- 2.5.1.8 TX AMI Parameters for USXGMII

- 2.5.1.9 TX AMI Parameters for Display Port

- 2.5.1.10 Transmitter Specifications

- 2.5.1.11 TX_Jitter Injection Parameters

- 2.5.2 Receiver (Rx) Model

- 2.5.1

Transmitter (Tx) Model

- 2.6 Valid Simulation Condition

- 2.7 Eye Mask Requirement

1.1.1 Introduction

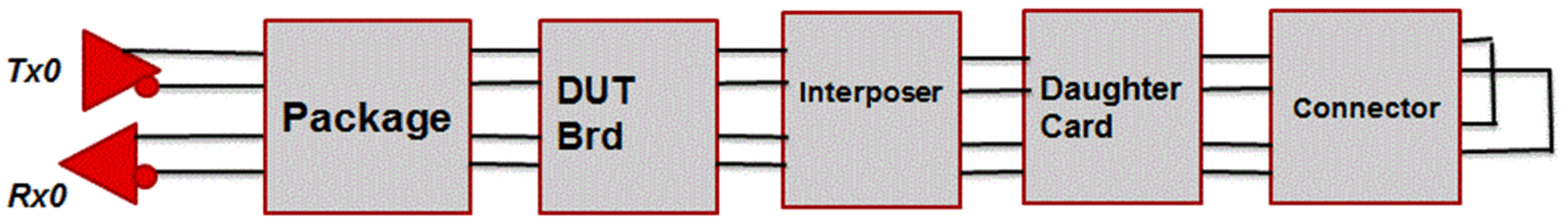

The general methodology for evaluating signal integrity for high-speed SERDES interfaces is illustrated in Figure 1-1. This involves running a channel simulation for the serial link. The methodology uses IBIS-Algorithmic Modeling Interface (AMI) models for the Tx/Rx blocks. The basic setup and settings documented here can be used to validate all SerDes links and also across a variety of EDA Signal Integrity simulators. This channel simulation should be performed as a signoff check for all high-speed Serial Link interfaces.

Figure 1-1 Signal Integrity Analysis Setup -

Channel Simulation

Figure 1-1 Signal Integrity Analysis Setup -

Channel Simulation