SPRADE1 March 2024 AM2434

2.2 The PRU Implement Parallel Port

Due to the maximum flexibility of the PRU, this makes the PRU also suitable parallel port application scenarios as well. In this section, the PRU’s GPIO direct input and output mode is also applied. The PRU can implement a parallel port with either direct input/output mode, or parallel capture mode. Parallel capture mode uses an external clock to latch data on the rising or falling edge of the clock. Direct input/output mode can be used to provide a clock for the parallel port output. Set and clr instructions can be used to toggle the clock output. For example, set r30, r30, 0 will set the PRUx_GPO0 pin to high voltage level, while clr r30, r30, 0 sets the pin to a low voltage level. The PRU can also compensate for the settling time of the data as well as the hold time due to its determinism of the instructions.

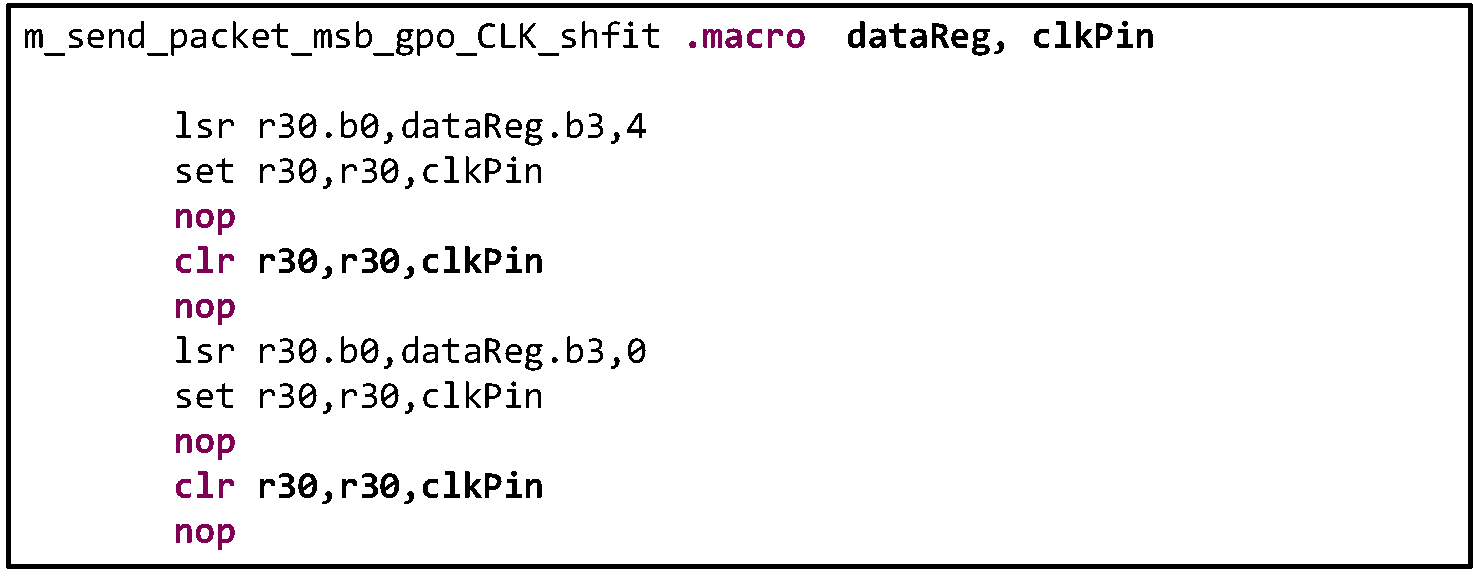

A simple macro for the parallel port is shown in Figure 2-10, where the clock cycles are 5 PRU cycles.

Figure 2-10 Macro of Parallel Port

Output

Figure 2-10 Macro of Parallel Port

Output