TIDT261 March 2022

3.1 Switching

|

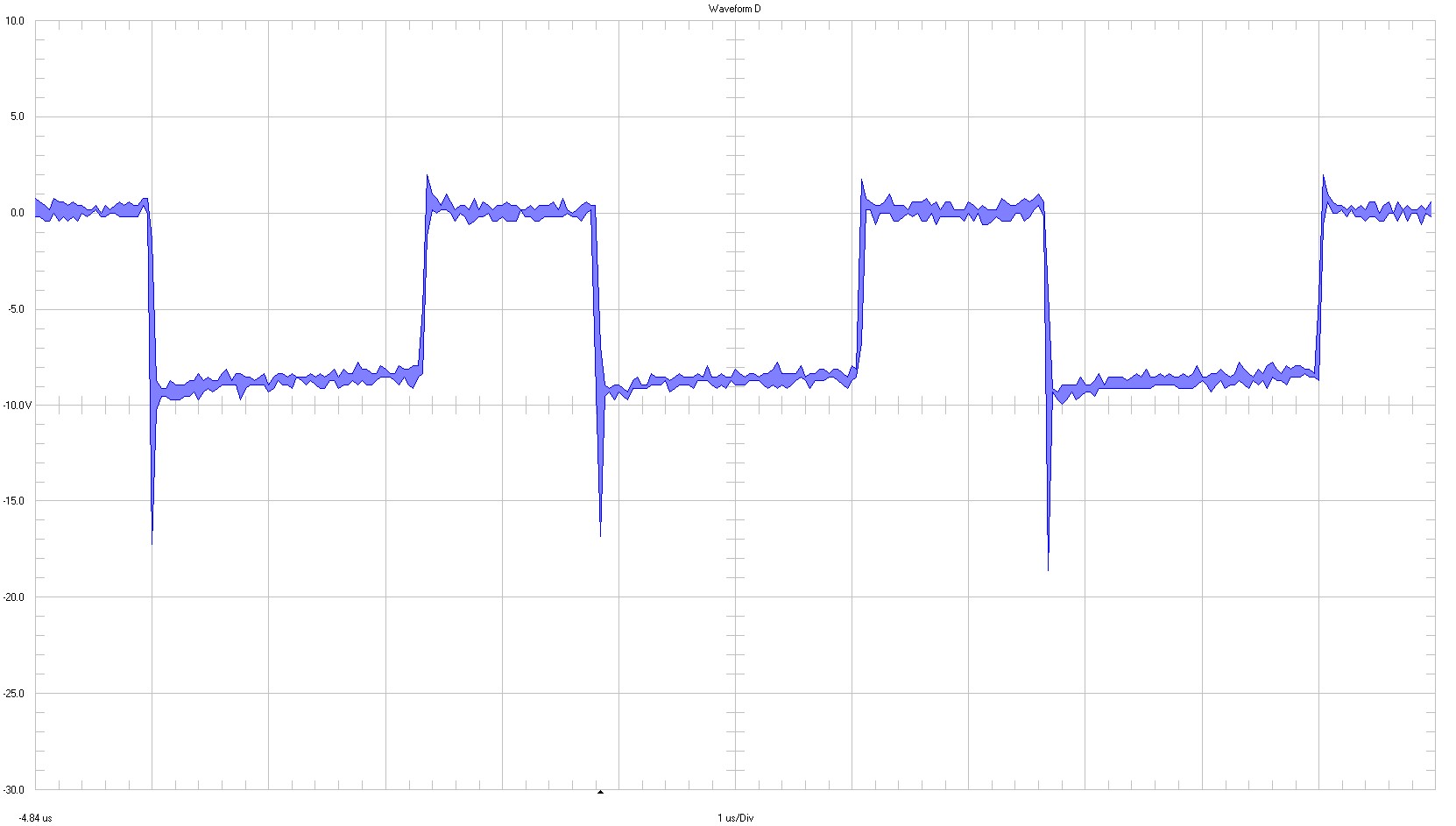

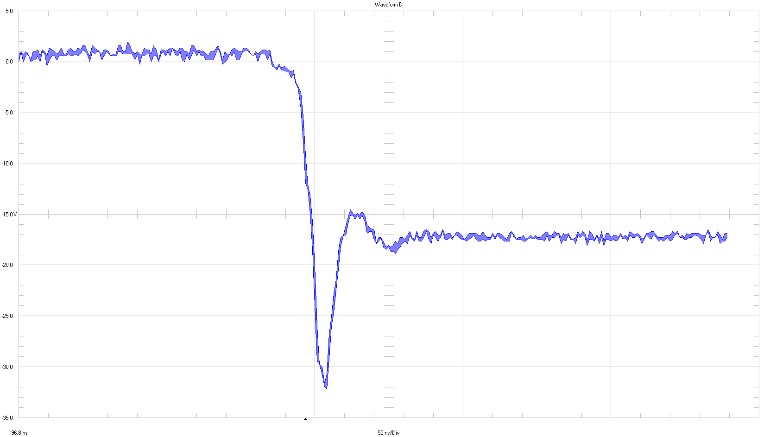

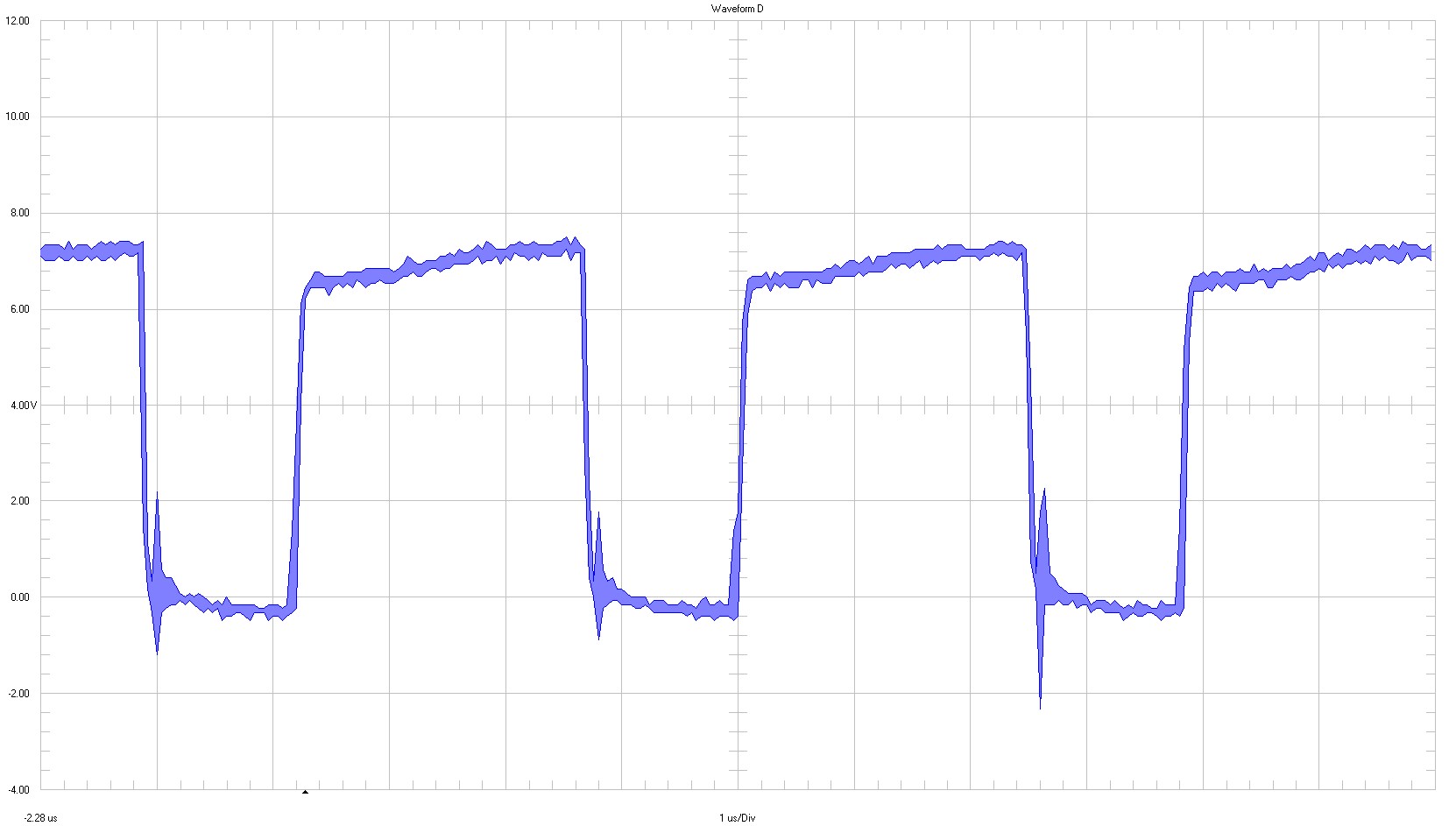

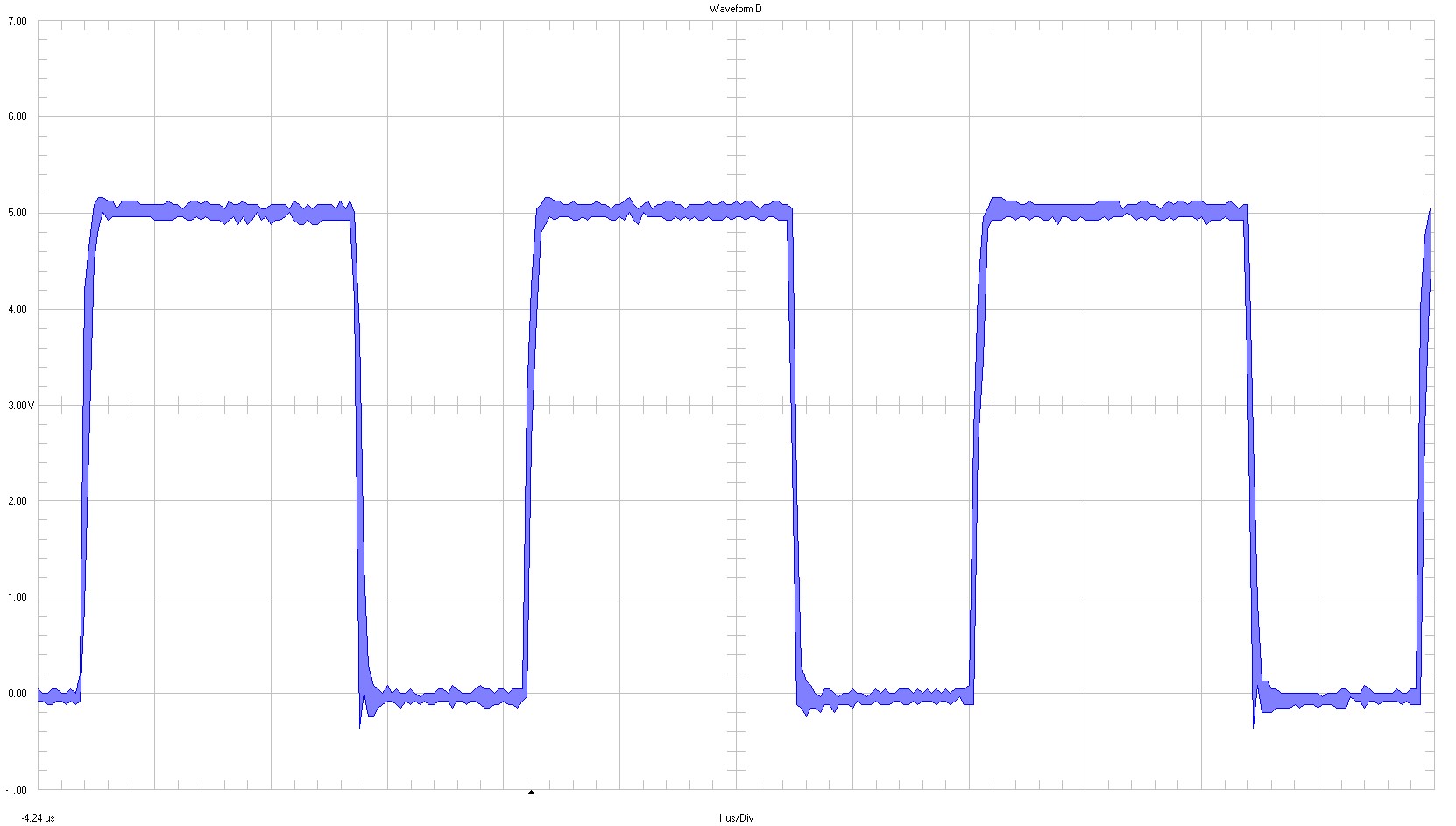

CH1 ⇒ 5 V / div 1-µs /div full bandwidth |

|

|

|

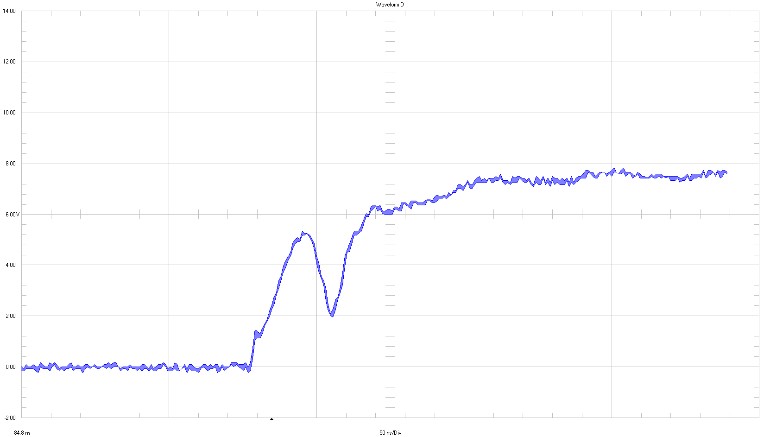

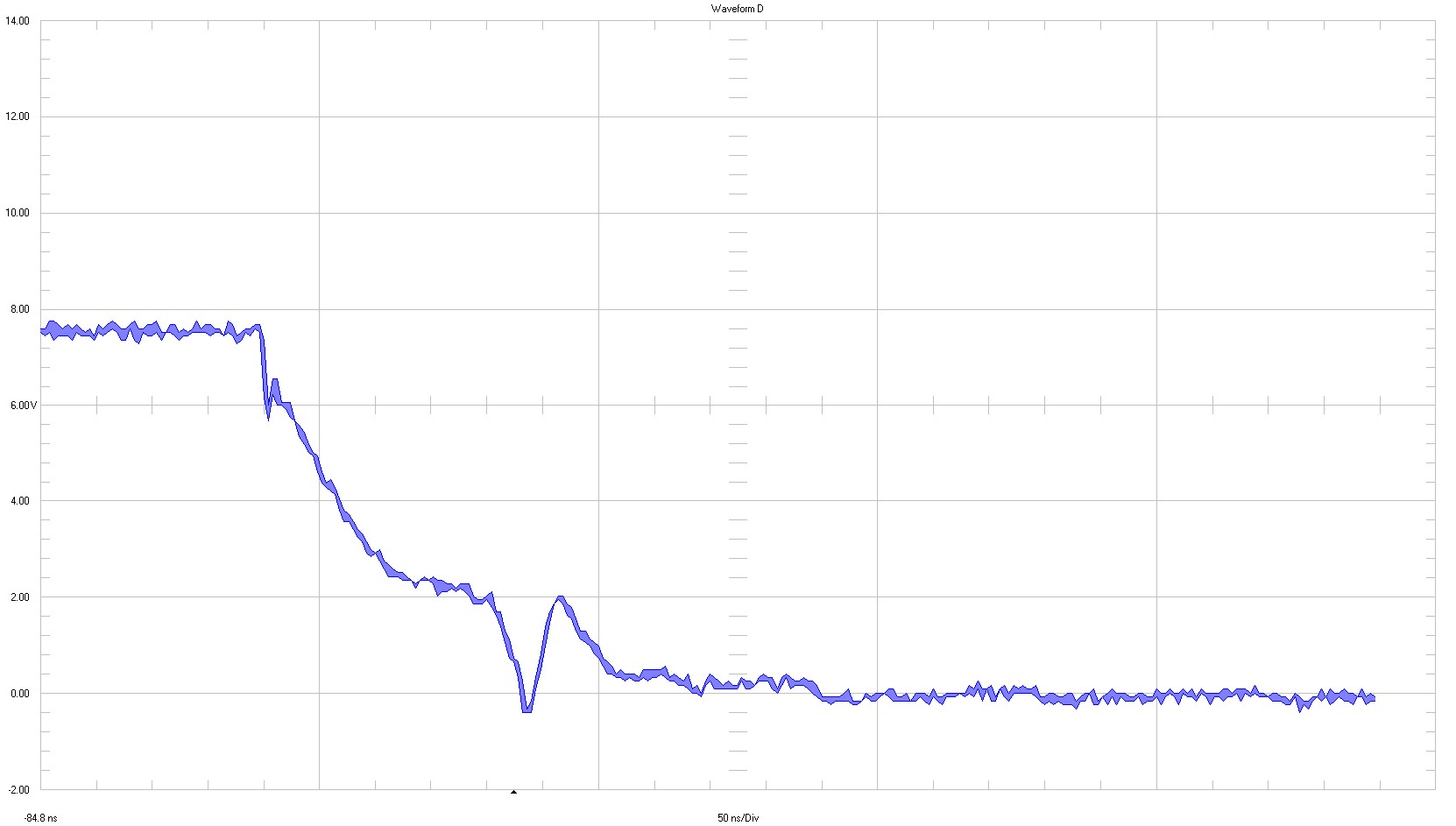

CH1 ⇒ 5 V / div 50 ns / major div full bandwidth |

Figure 3-1 Q1 (High Side FET) Source-Drain

(Referenced to VOUT), 4-V Input Voltage

|

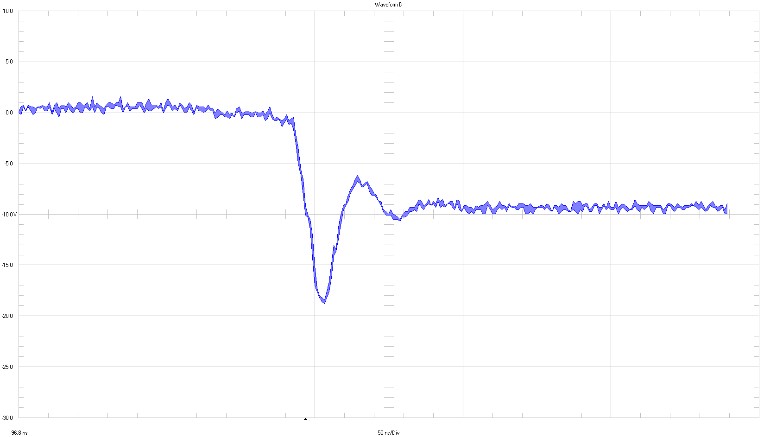

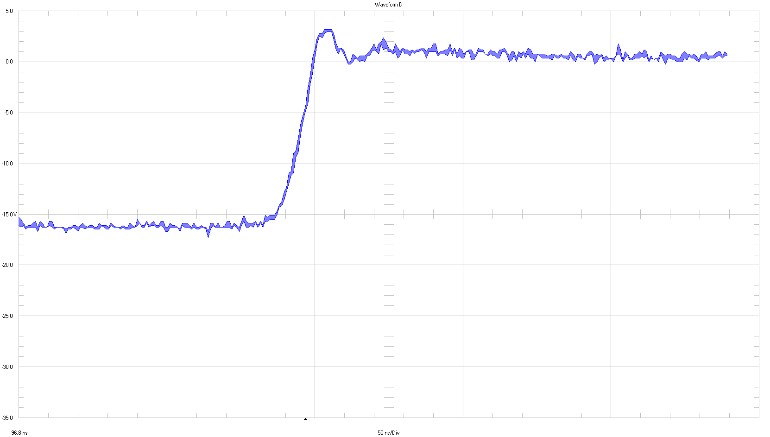

CH1 ⇒ 5-V / div 1-µs / div |

|

|

|

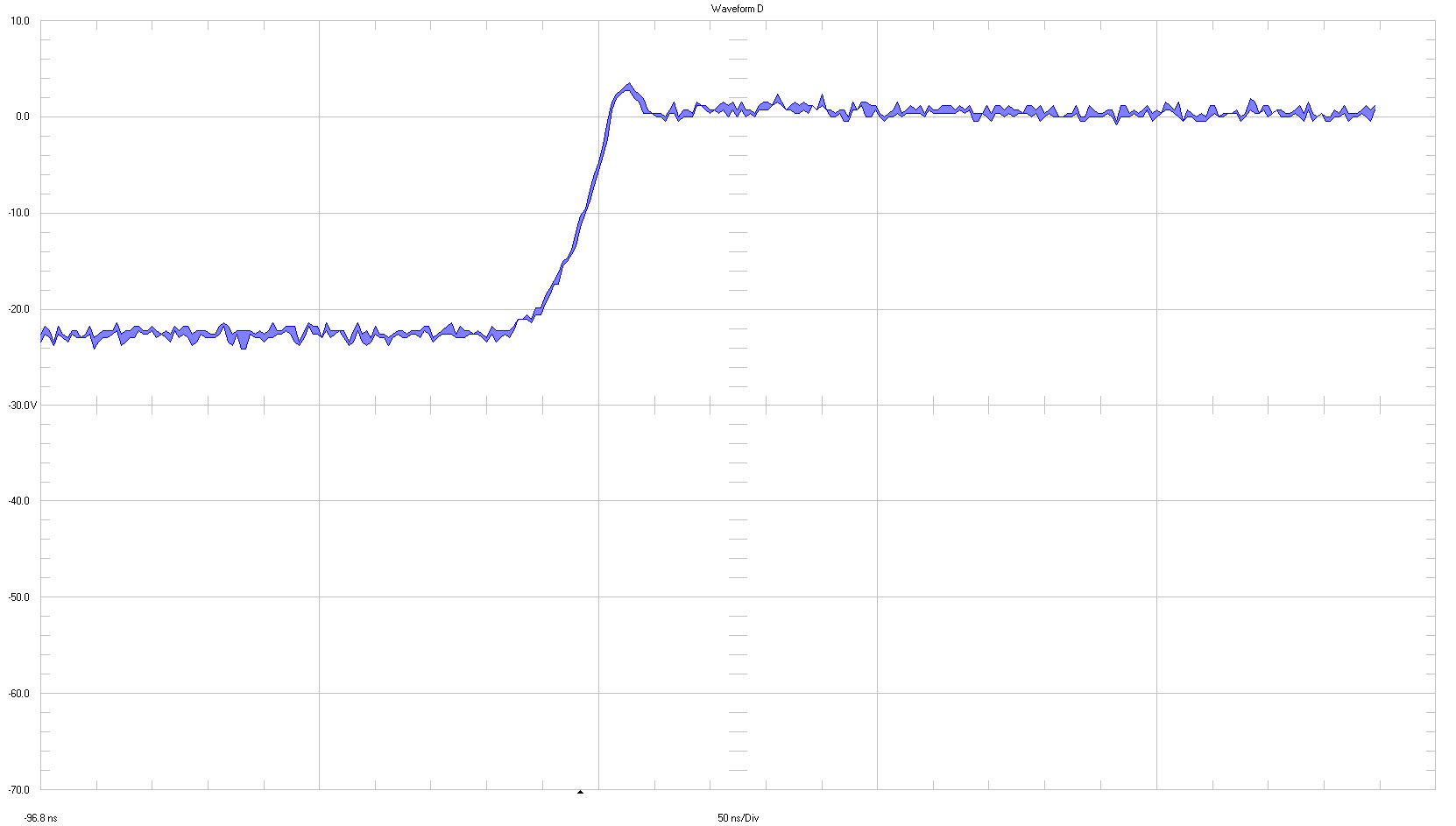

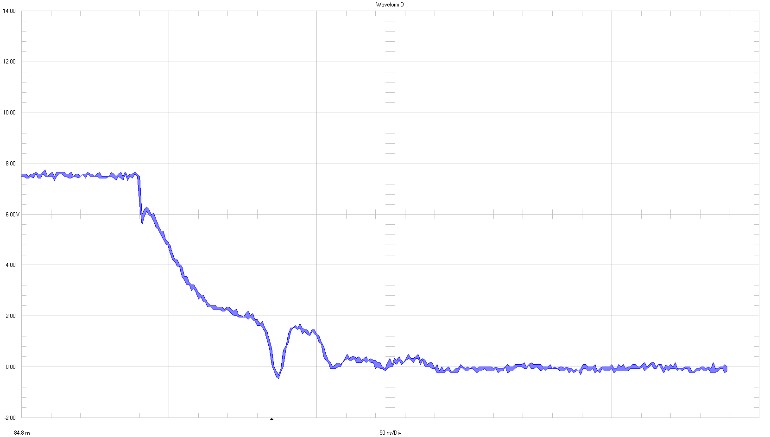

CH1 ⇒ 50-ns / major div |

Figure 3-2 Q1 (High Side FET) Source-Drain

(Referenced to VOUT), 12-V Input Voltage

|

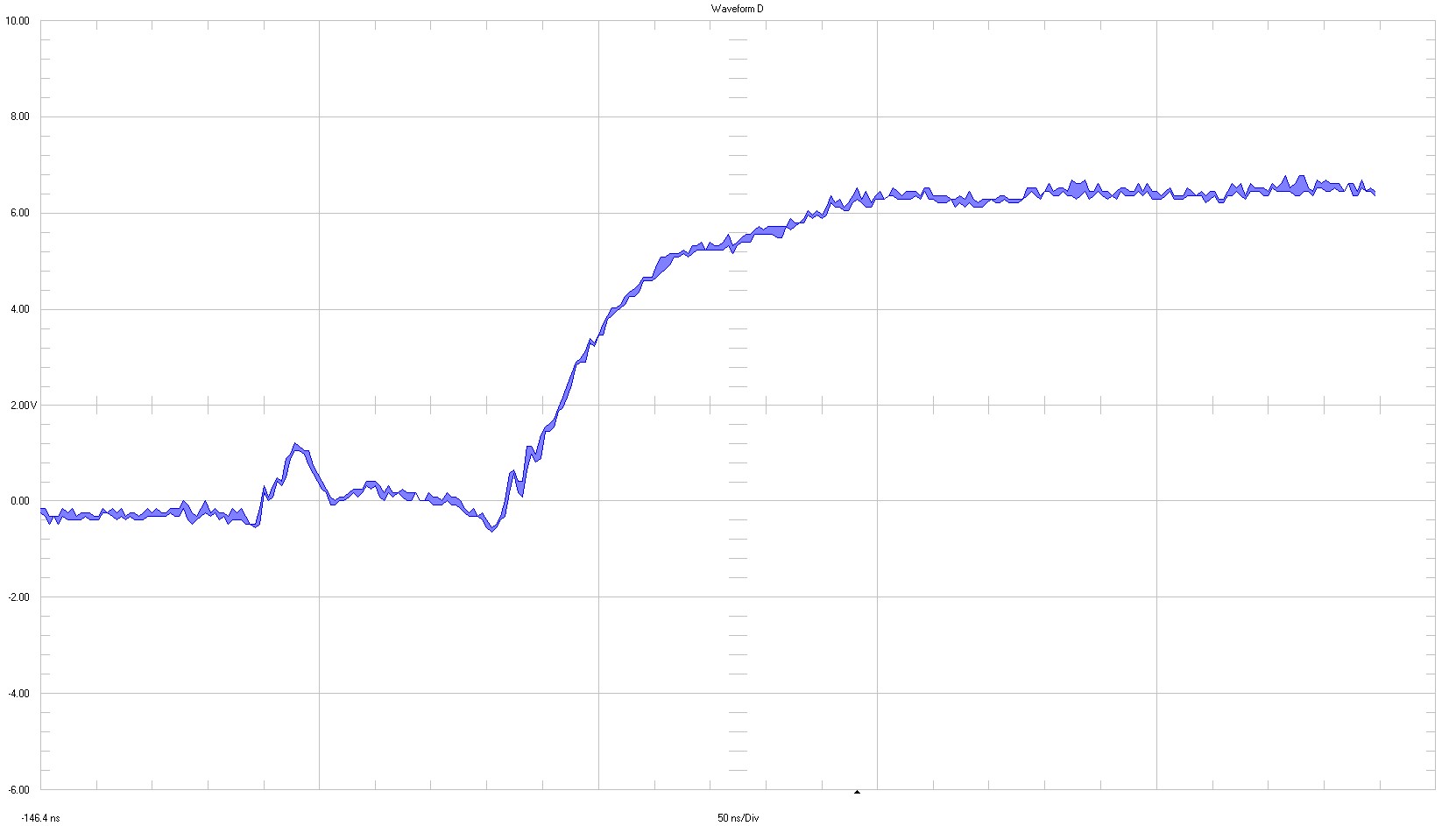

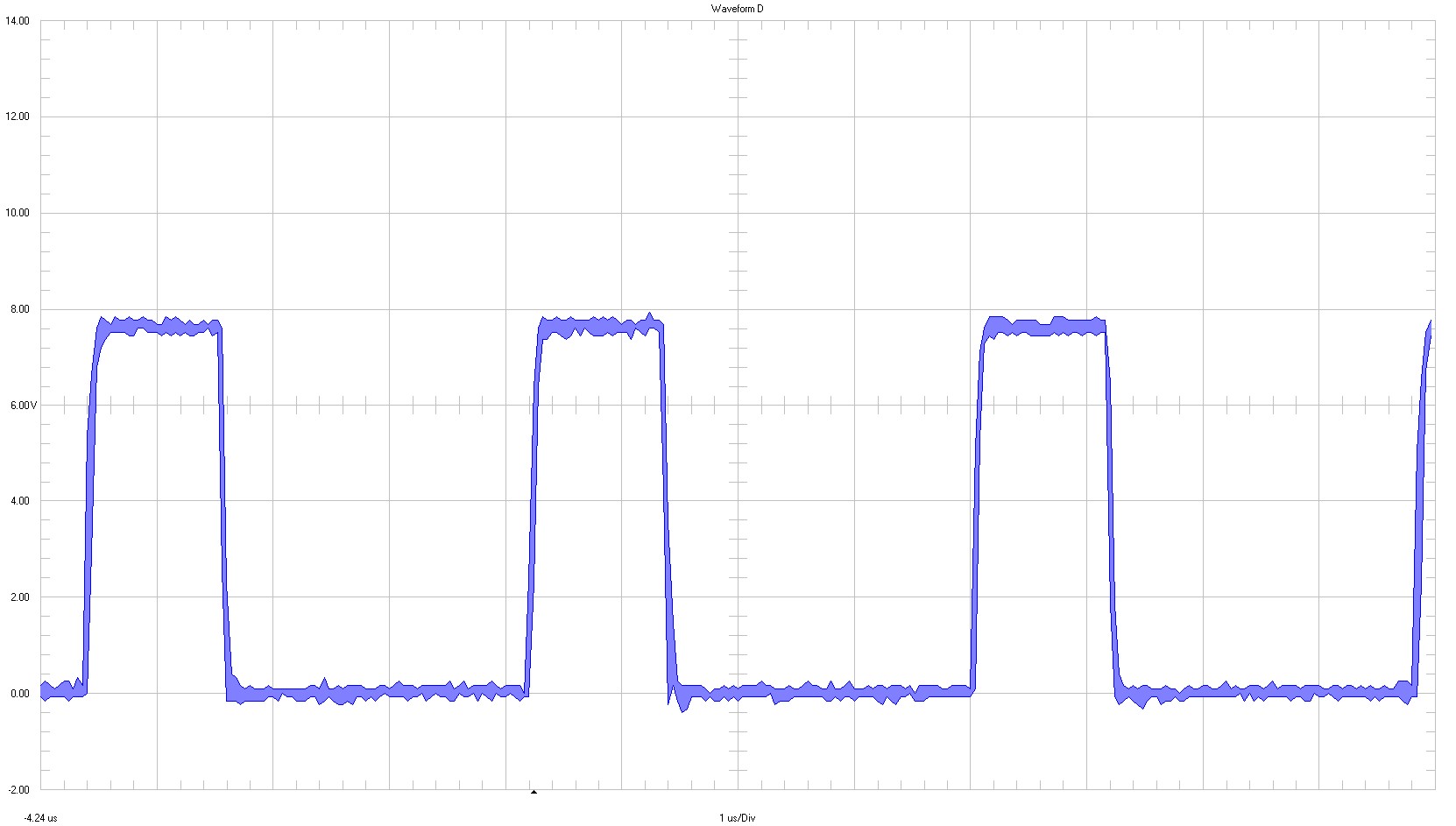

CH1 ⇒ 10-V / div 1-µs / div |

|

|

|

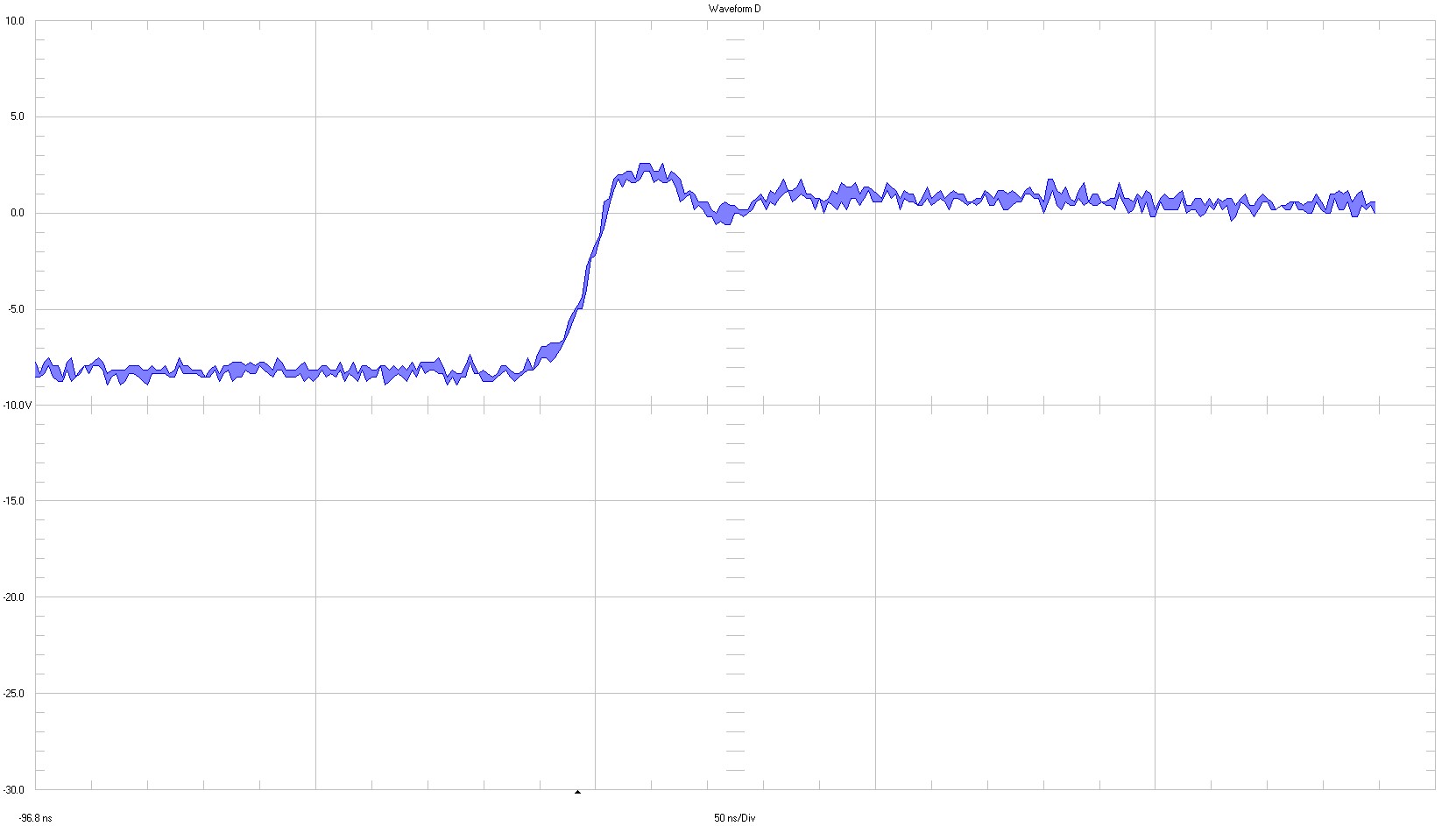

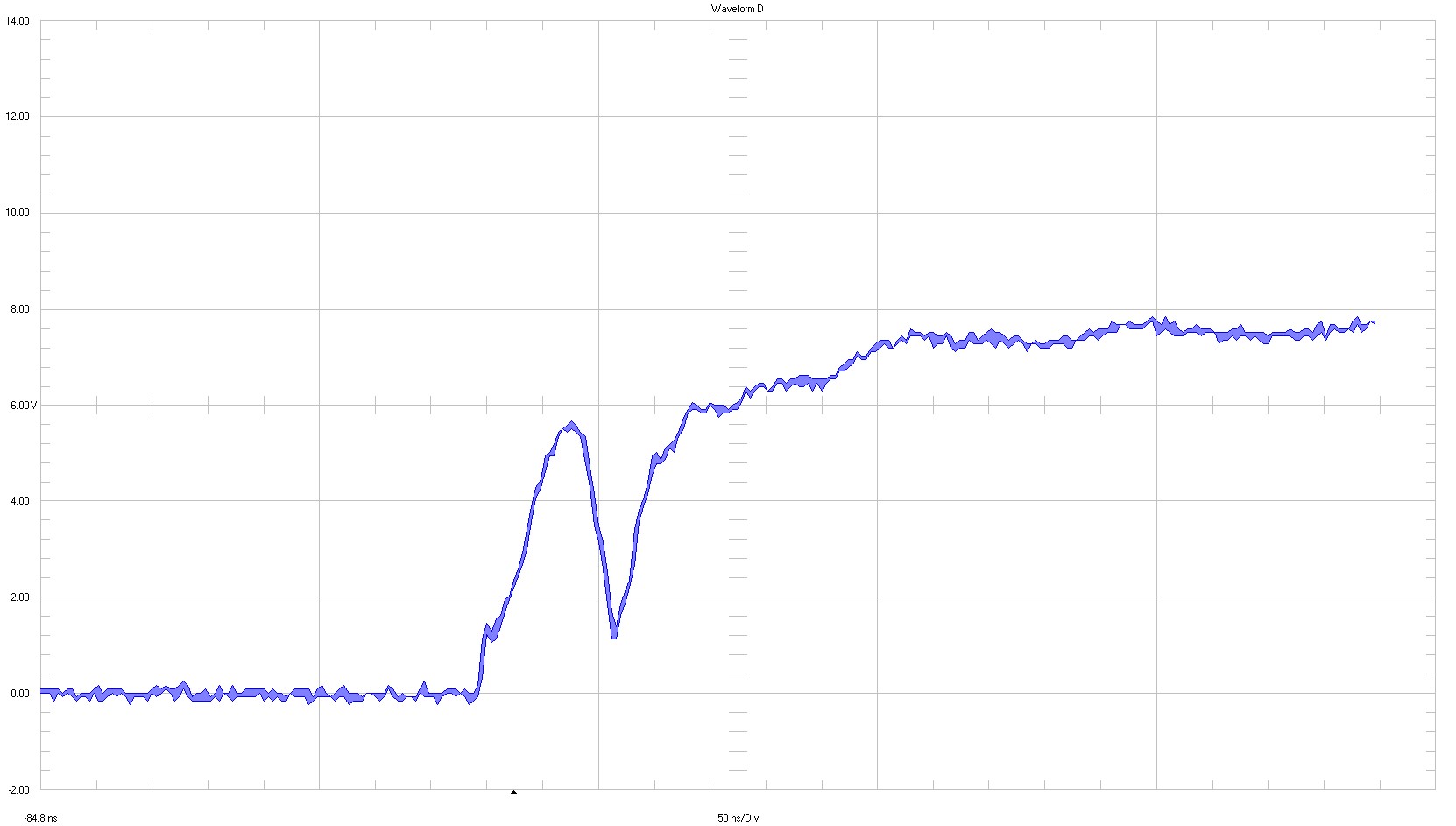

CH1 ⇒ 50-ns / major div |

Figure 3-3 Q1 (High Side FET) Source-Drain

(Referenced to VOUT), 18-V Input Voltage

|

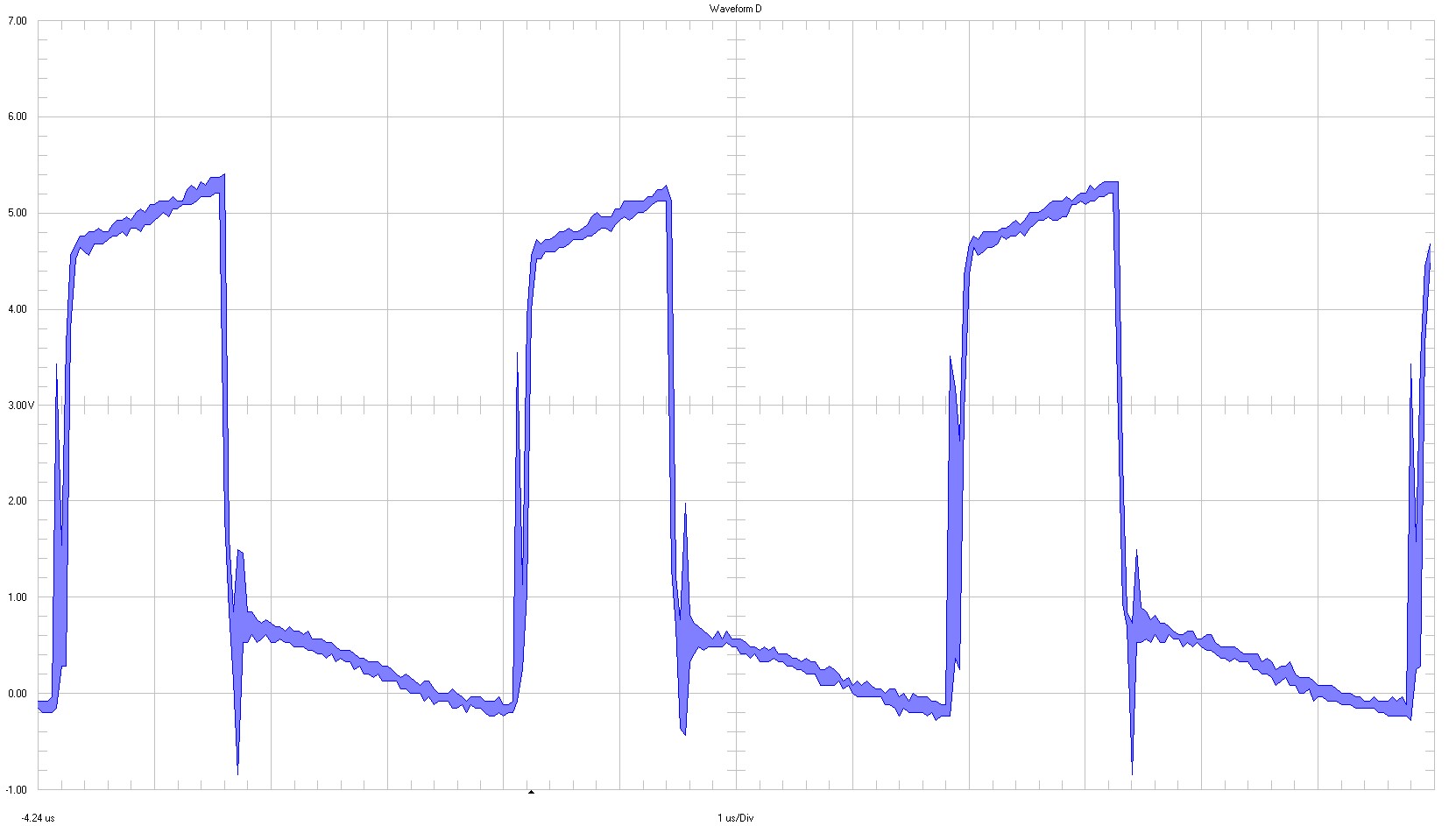

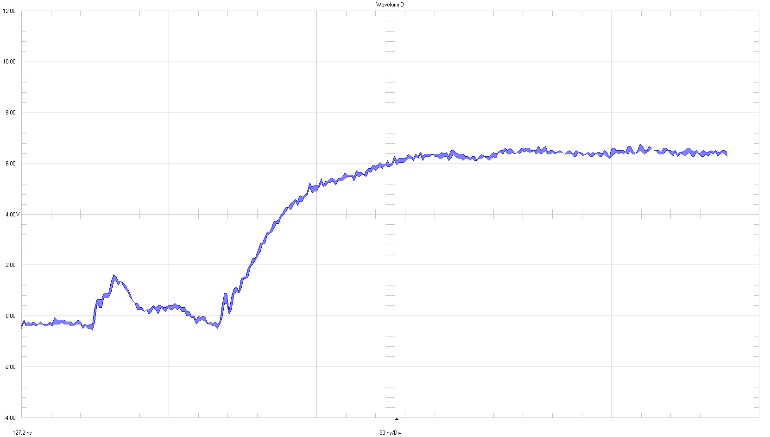

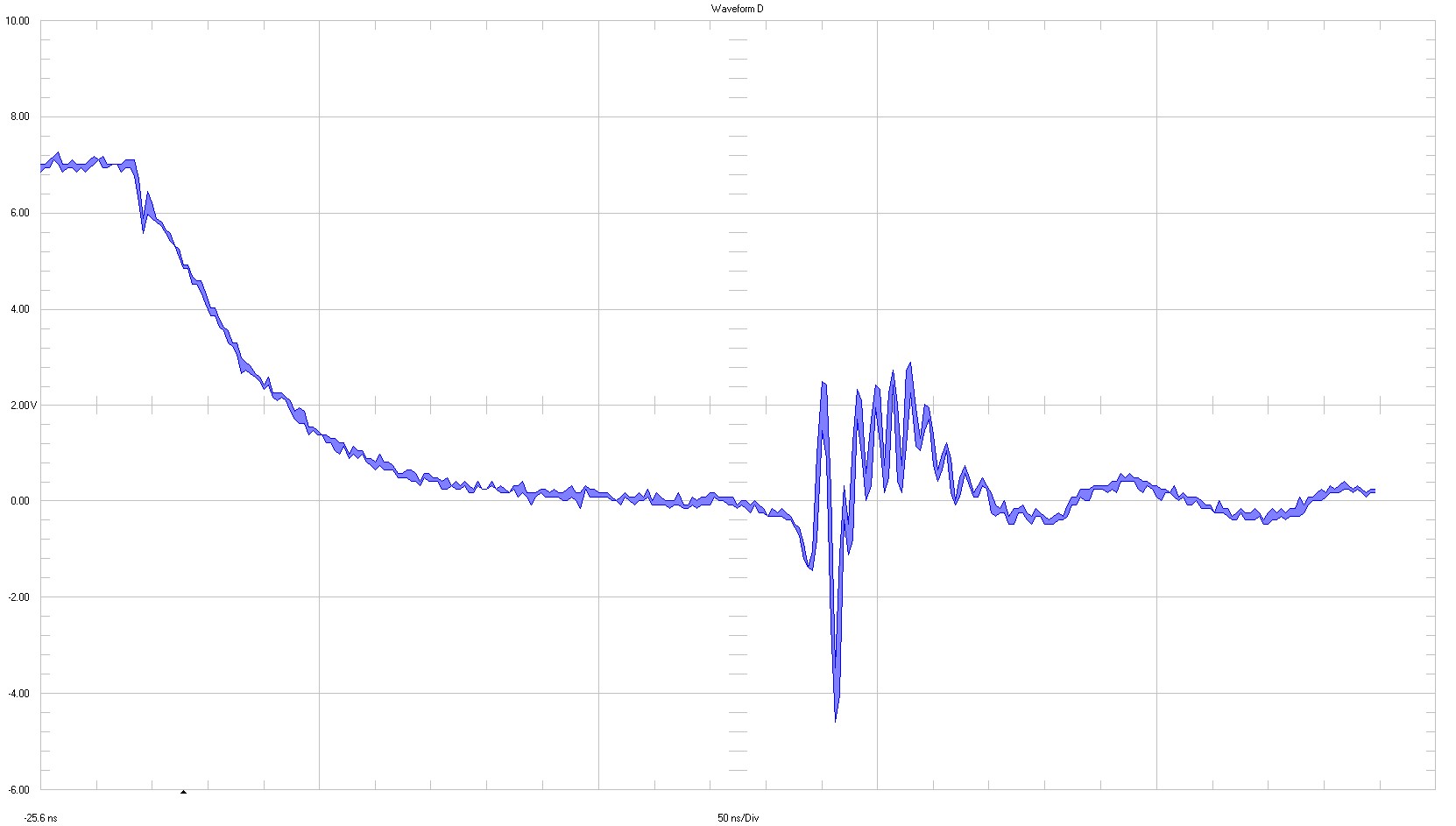

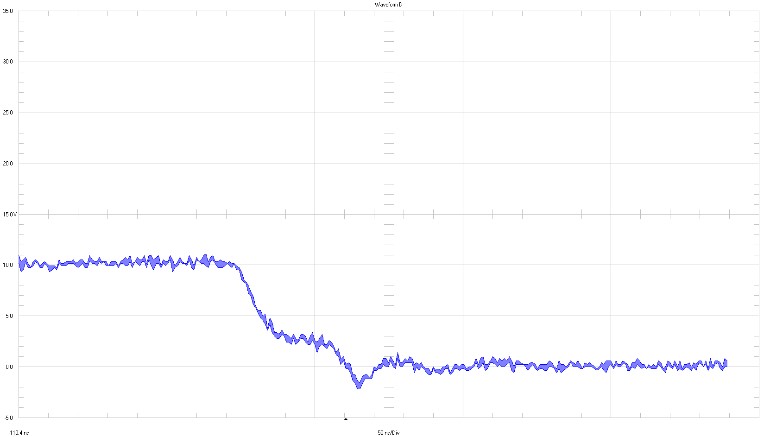

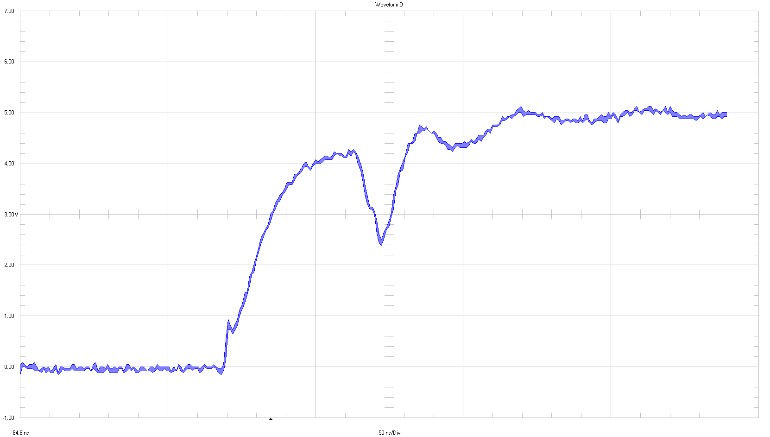

CH1 ⇒ 1-V / div 1-µs / div full bandwidth |

|

|

|

CH1 ⇒ 50-ns / major div |

Figure 3-4 Q1 Gate, 4-V Input Voltage

|

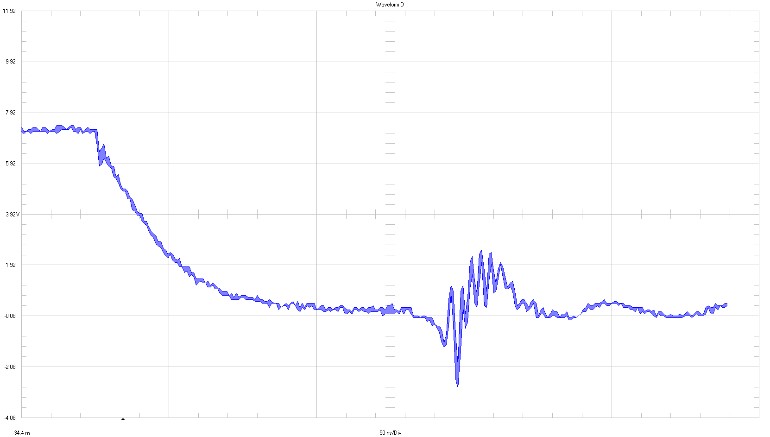

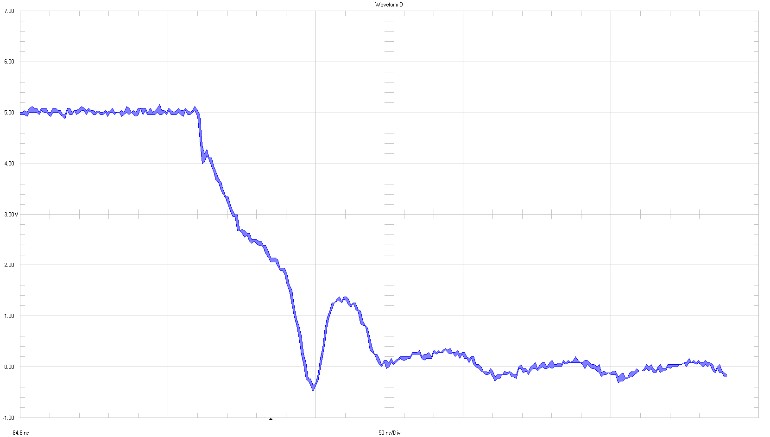

CH1 ⇒ 1-V / div 1-µs / div full bandwidth |

|

|

|

CH1 ⇒ 50-ns / major div |

Figure 3-5 Q1 Gate, 12-V Input Voltage

|

CH1 ⇒ 2-V / div 1-µs / div full bandwidth |

|

|

|

CH1 ⇒ 50-ns / major div |

Figure 3-6 Q1 Gate, 18-V Input Voltage

|

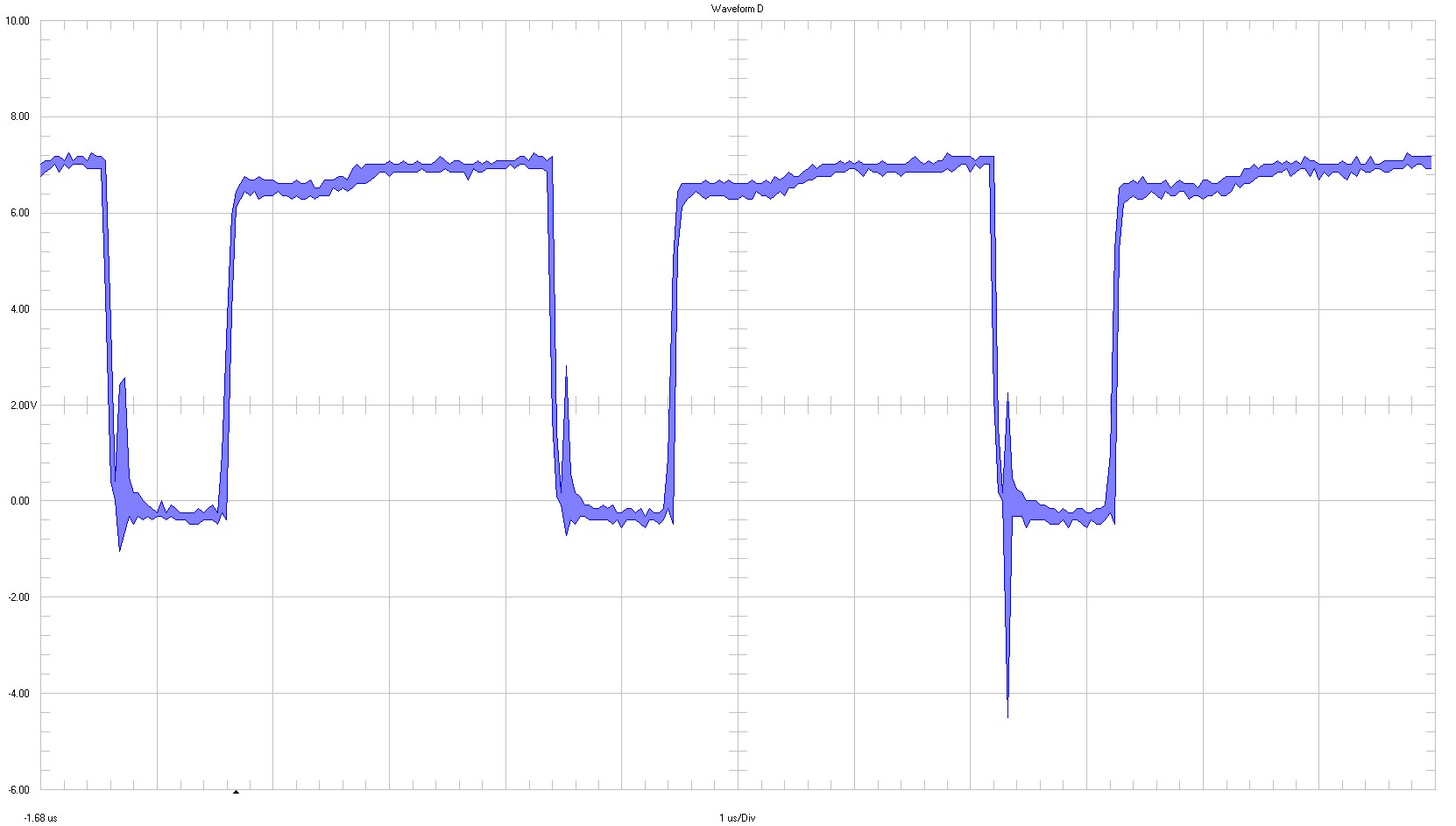

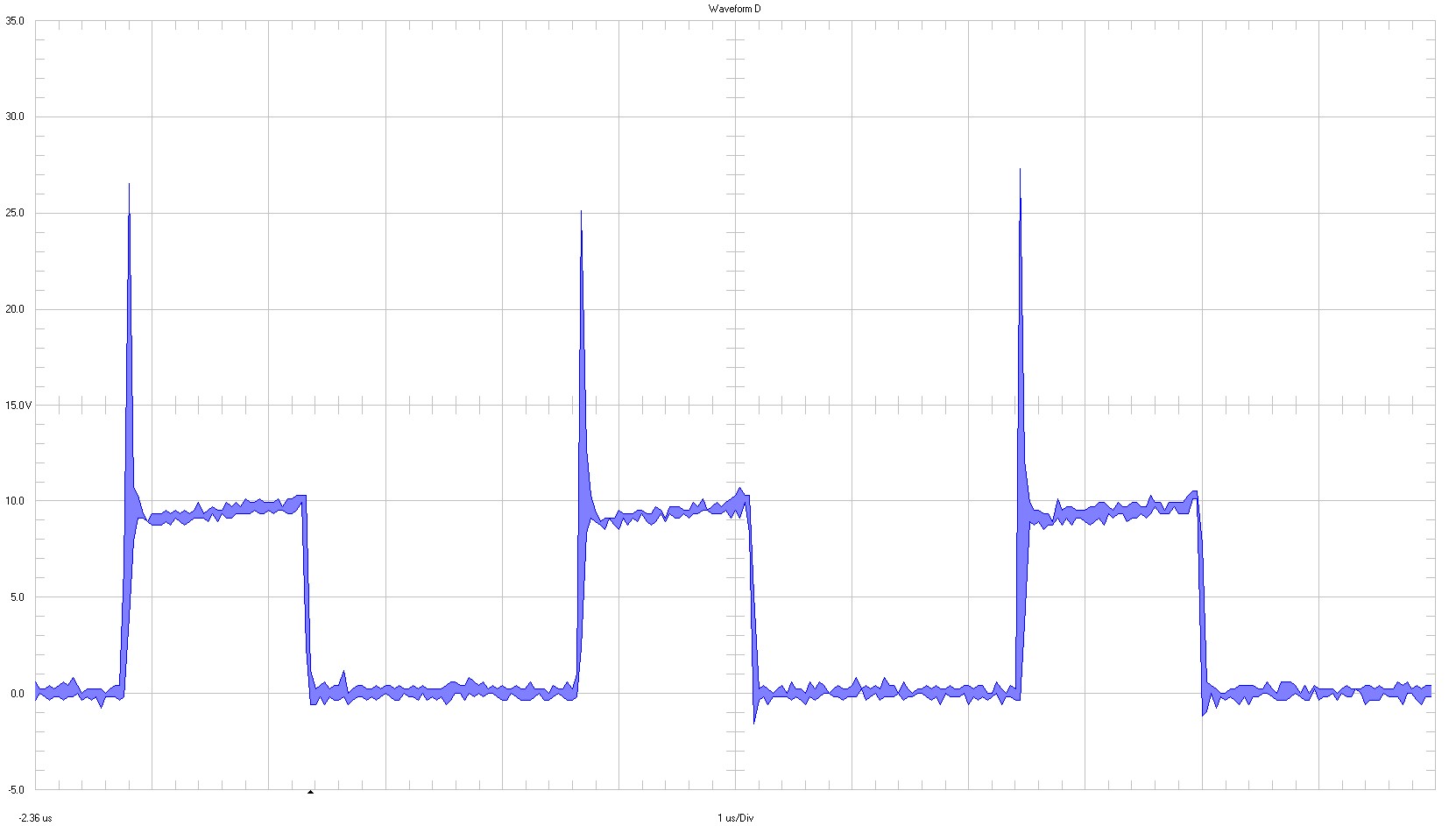

CH1 ⇒ 5-V / div 1-µs / div full bandwidth |

|

|

|

CH1 ⇒ 50-ns / major div |

Figure 3-7 Q2 (LoSide FET) Drain Source, 4-V

Input Voltage

|

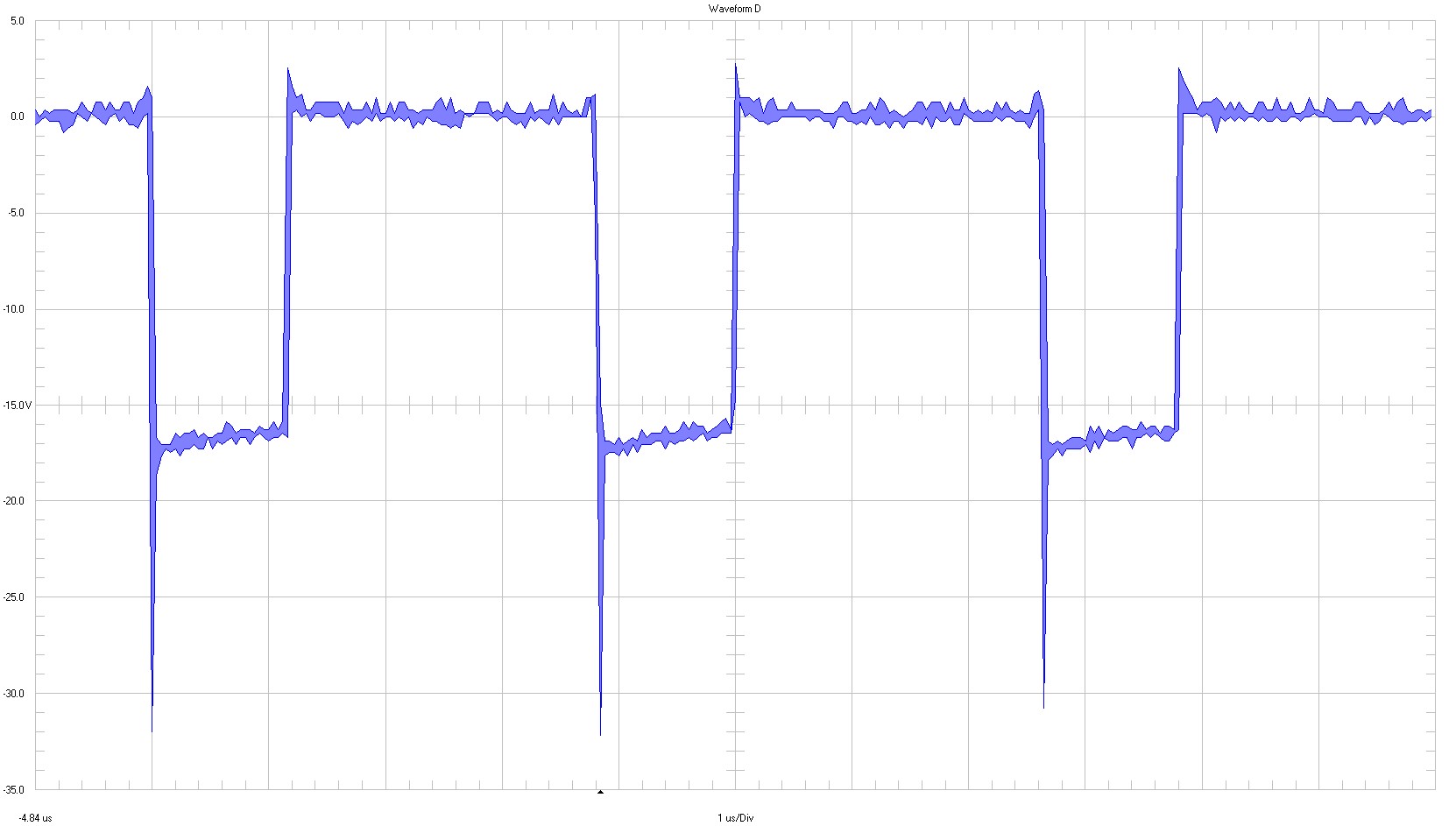

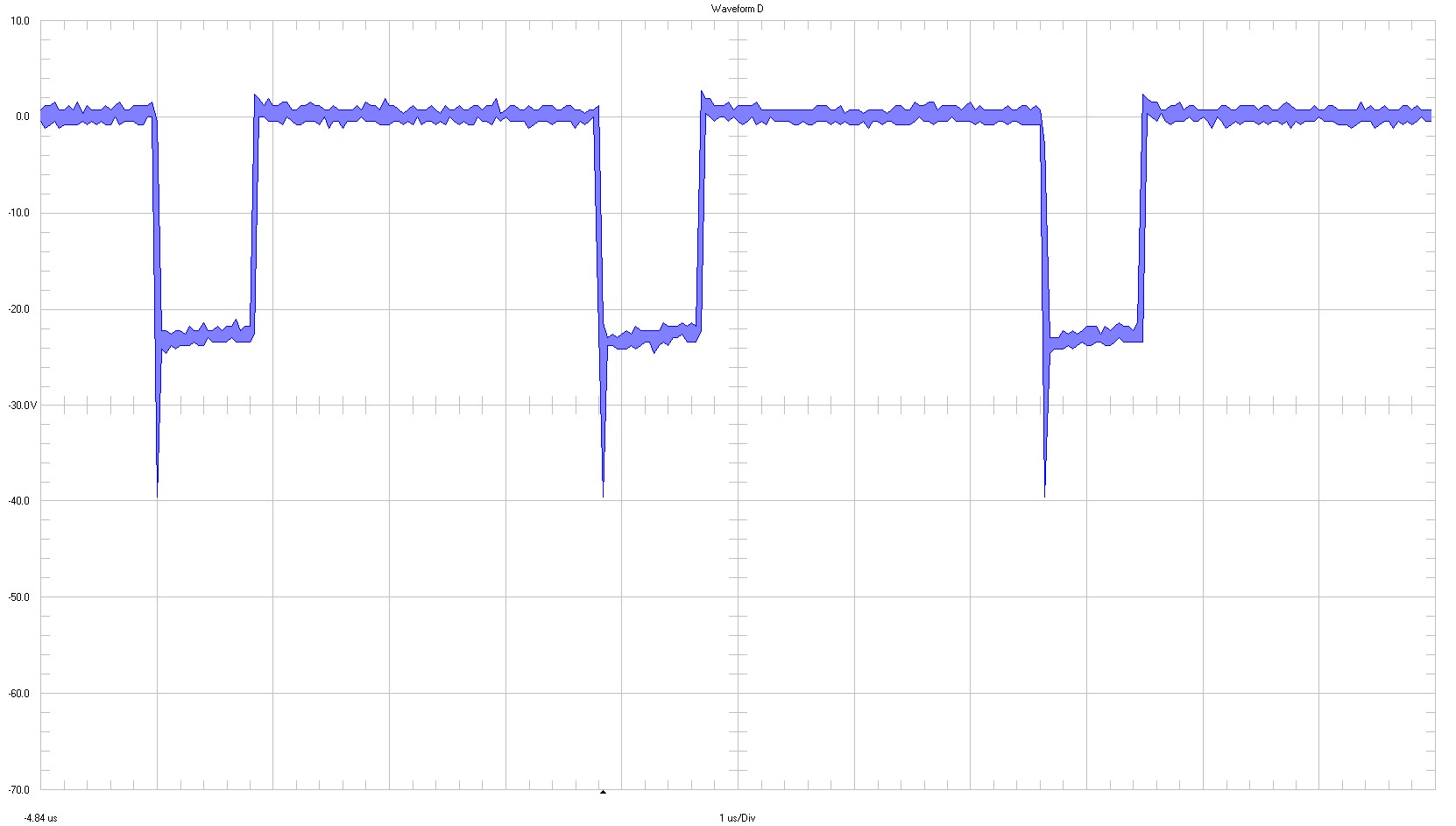

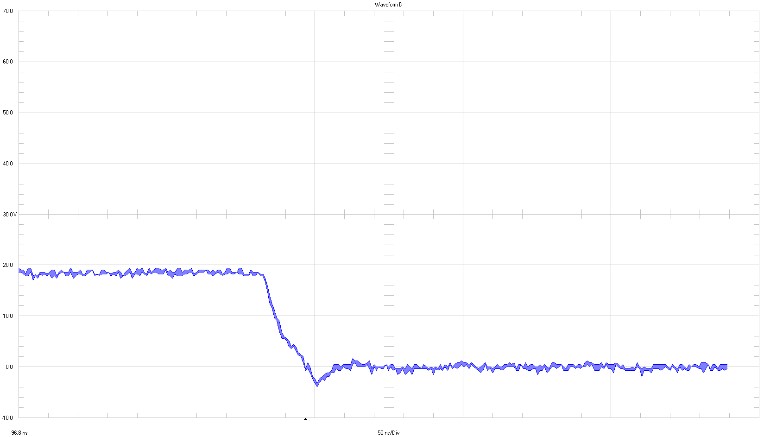

CH1 ⇒ 10-V / div 1-µs / div full bandwidth |

|

|

|

CH1 ⇒ 50-ns / major div |

Figure 3-8 Q2 (LoSide FET) Drain Source, 12-V

Input Voltage

|

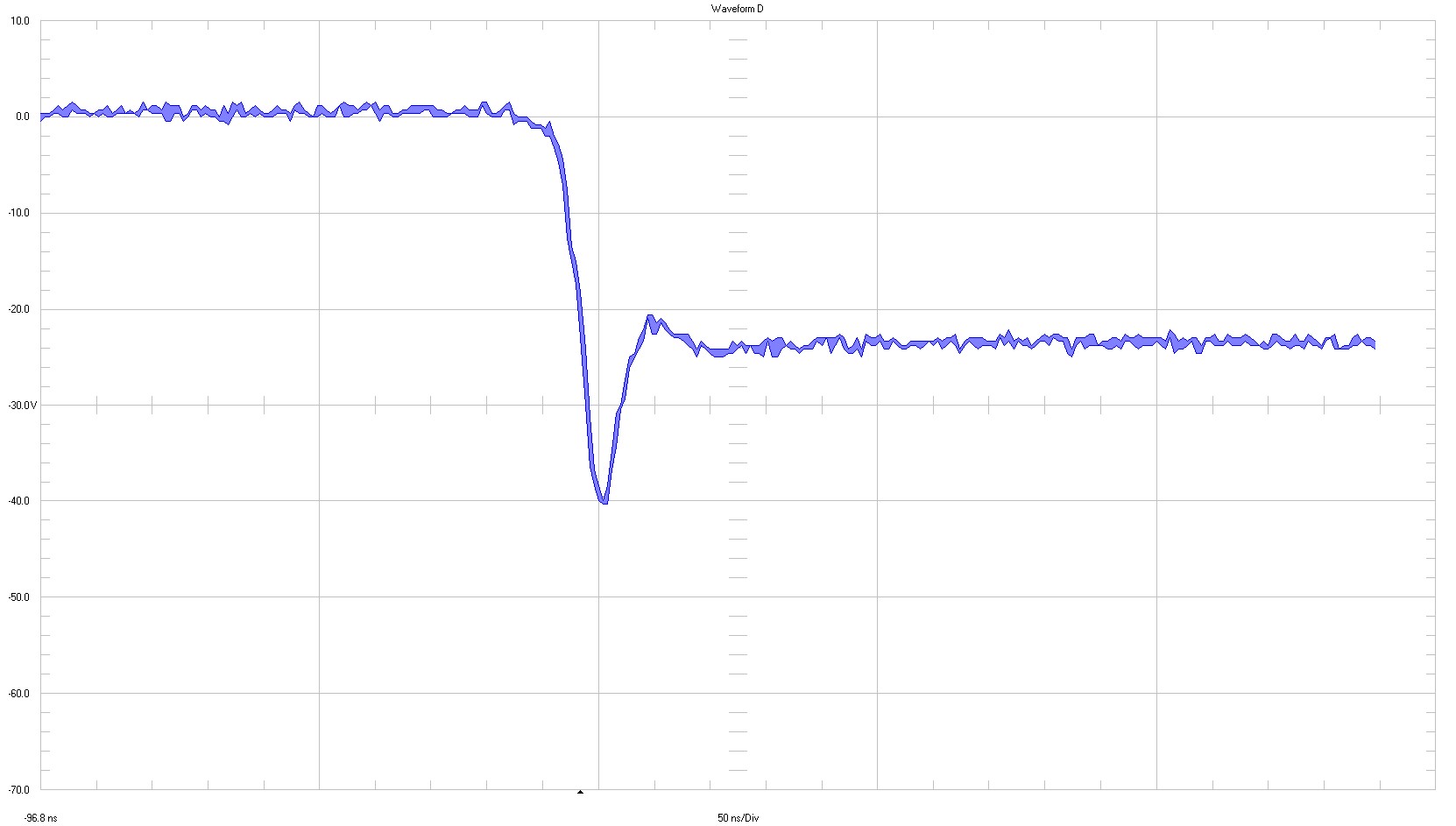

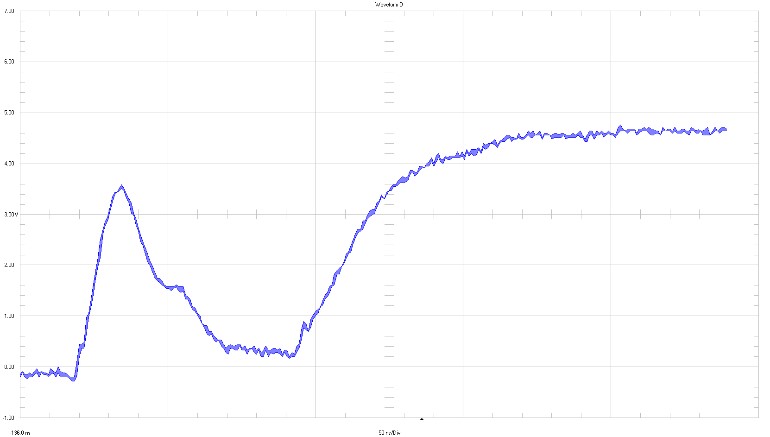

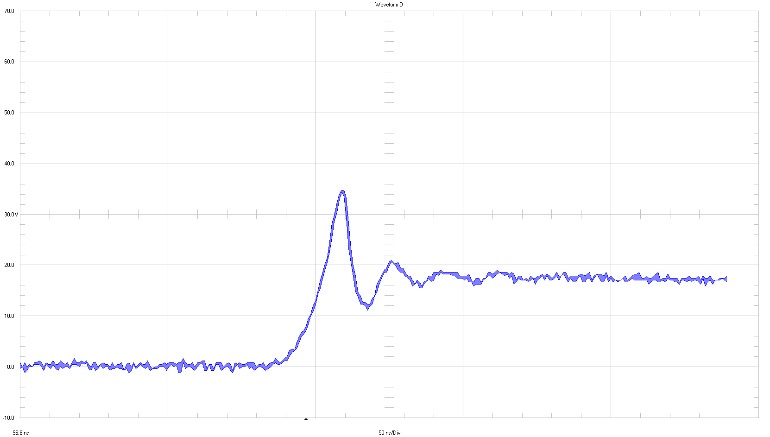

CH1 ⇒ 1-V / div 1 µs / div full band width |

|

|

|

CH1 ⇒ 50-ns / major div |

Figure 3-9 Q2 (LoSide FET) Drain Source, 4-V

Input Voltage

|

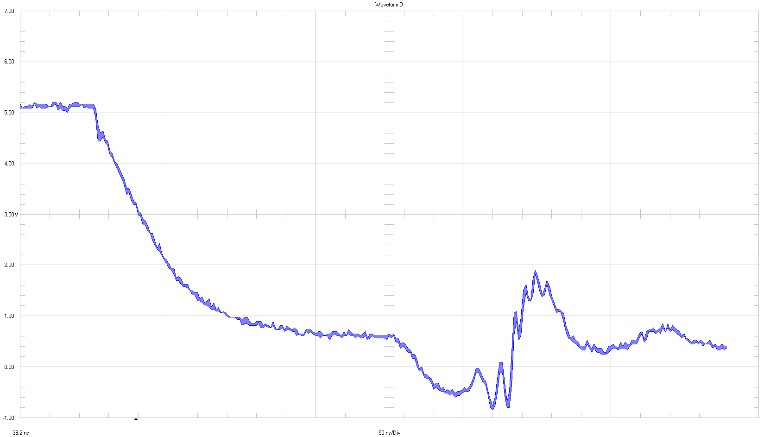

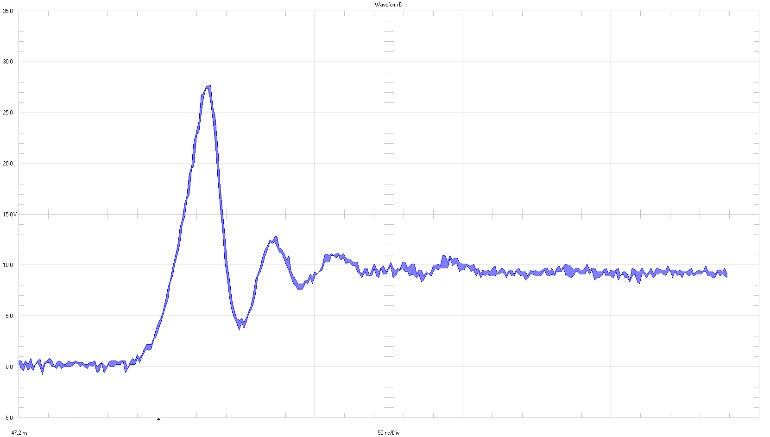

CH1 ⇒ 2-V / div 1-µs / div full bandwidth |

|

|

|

CH1 ⇒ 50-ns major div |

Figure 3-10 Q2 Gate, 12-V Input Voltage

|

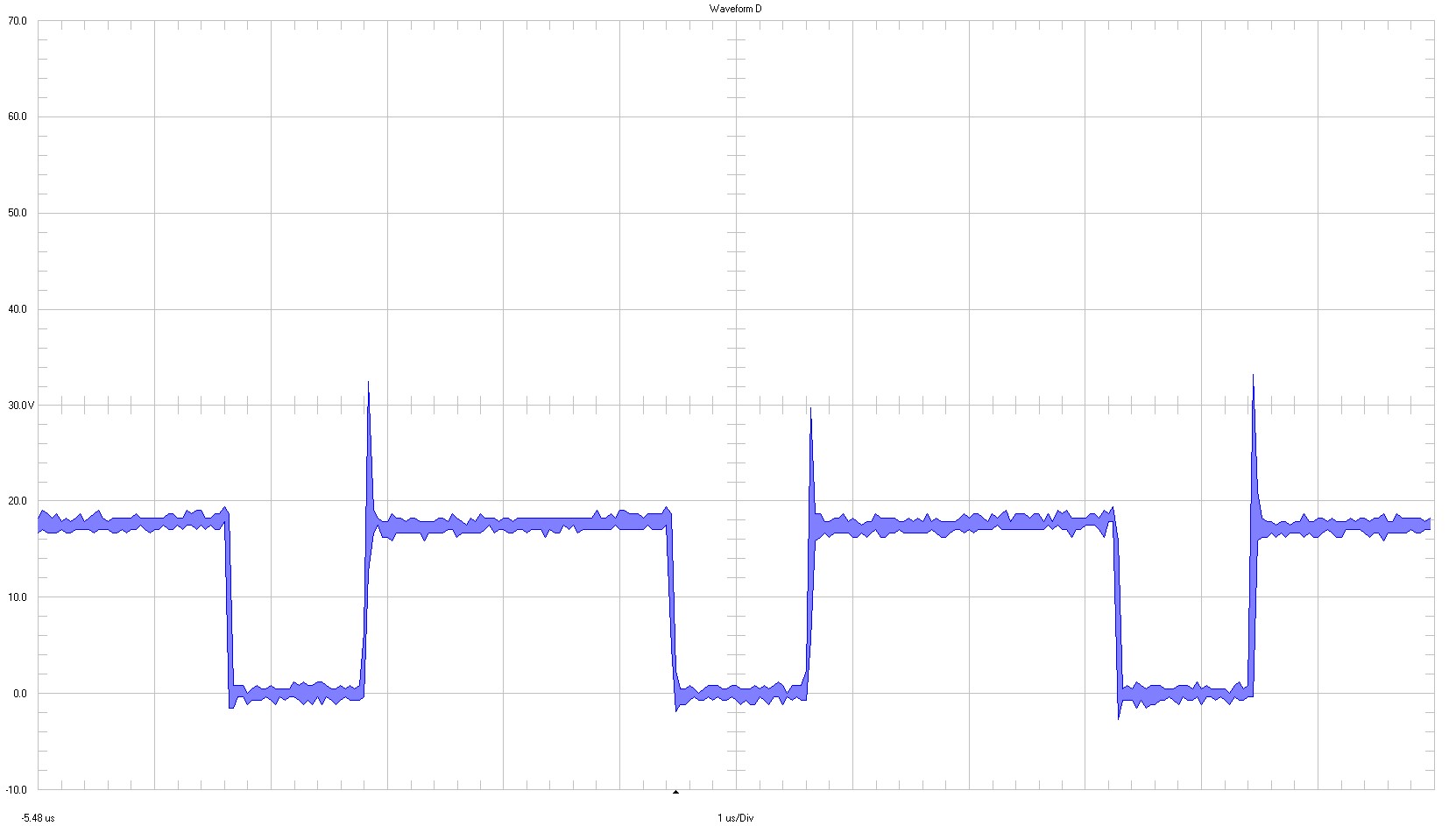

CH1 ⇒ 2-V / div 1-µs / div |

|

|

|

CH1 ⇒ 2-V / div 50-ns / div |

Figure 3-11 Q2 Gate, 18-V Input Voltage