SLAAEF8 January 2024 MSPM0L1105 , MSPM0L1105

5.3 Power/Communication Software Design

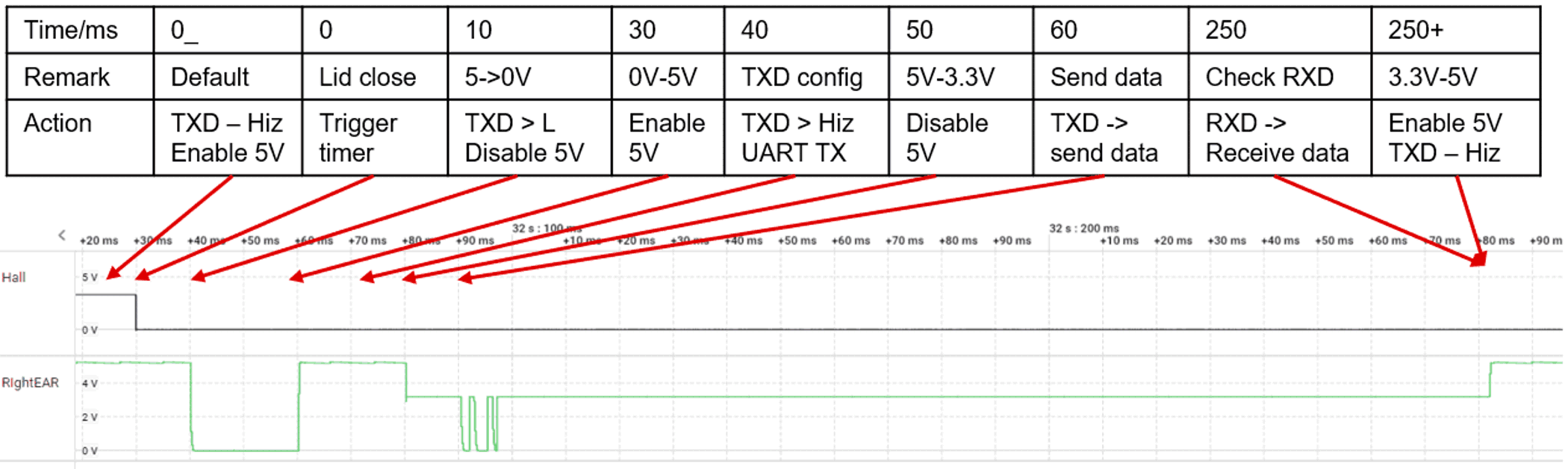

The general-purpose timer (TIMG) is used to mimic the waveform in Figure 5-3. MSPM0L series provides up to four individual timer modules each has extensive event generation capabilities, such as counter overflow, reload, and capture/compare actions for a variety of use cases. In this design, the timer is used as a clock which triggers every 10 ms. The corresponding actions in each time sample can be seen in the figure below. This design successfully generates communication and power waveforms.

Figure 5-3 Actions in Each Time Sample and Final Waveform

Figure 5-3 Actions in Each Time Sample and Final Waveform