SLAZ162J October 2012 – May 2021 MSP430F2131

- 1Functional Advisories

- 2Preprogrammed Software Advisories

- 3Debug Only Advisories

- 4Fixed by Compiler Advisories

- 5Nomenclature, Package Symbolization, and Revision Identification

-

6Advisory Descriptions

- 6.1 BCL6

- 6.2 BCL8

- 6.3 BCL9

- 6.4 BCL10

- 6.5 BCL11

- 6.6 BCL12

- 6.7 BCL13

- 6.8 BCL14

- 6.9 BSL5

- 6.10 CPU4

- 6.11 CPU5

- 6.12 CPU6

- 6.13 CPU11

- 6.14 CPU12

- 6.15 CPU13

- 6.16 CPU14

- 6.17 CPU19

- 6.18 CPU45

- 6.19 EEM20

- 6.20 FLASH16

- 6.21 FLASH17

- 6.22 FLASH18

- 6.23 FLASH19

- 6.24 FLASH20

- 6.25 FLASH22

- 6.26 FLASH24

- 6.27 FLASH27

- 6.28 FLASH36

- 6.29 JTAG15

- 6.30 PORT8

- 6.31 PORT10

- 6.32 SYS15

- 6.33 TA12

- 6.34 TA16

- 6.35 TA21

- 6.36 TAB22

- 6.37 XOSC5

- 6.38 XOSC8

- 7Revision History

6.12 CPU6

CPU Module

Category

Compiler-Fixed

Function

Incorrect execution of ADD instruction

Description

When the CPU executes an ADD (.B or .W) instruction using indirect addressing mode with destination R1 or R4 to R15, directly after a RET or RETI instruction, the addition will be executed twice. This bug does not apply in the case that the indirect source working register is R2 or R3 (constant generator access for #2 or #4 are valid).

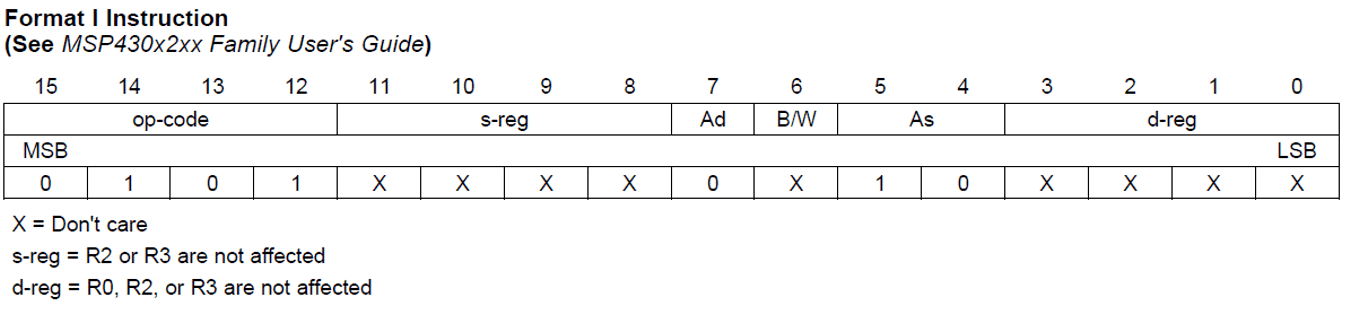

The instruction word mask that corresponds to the CPU6 condition is as follows:

Workaround

1. (Preferred) Use indexed addressing with offset 0 instead of indirect addressing:

ADD(.B/.W) 0(R10),R11

Note that some assemblers may convert this instruction to indirect addressing.

Alternatively, when the source is in assembly, making the following changes works around the bug. Perform the following only if Workaround 1 cannot be implemented.

or

2. Place an instruction (for example NOP) between any instances of CALL and ADD(.B/.W) instructions where the ADD immediately follows the CALL.

or

3. Replace all RETI instructions with 'DW 01301h'. The instruction word for RETI is 01300h. By replacing this directly in assembly with 01301h, the bug is avoided and the RETI instruction is executed properly; for example:

WDT_ISR ; Exit LPM3 on reti

bic.w #LPM3,0(SP) ;

;reti ; Replace RETI with

DW 01301h ; this line of code

Refer to the table below for compiler-specific fix implementation information.

| IDE/Compiler | Version Number | Notes |

|---|---|---|

| IAR Embedded Workbench | IAR EW430 v4.x or later | User is required to add the compiler flag option below. --hw_workaround=CPU6 Add -h option for Assembler |

| TI MSP430 Compiler Tools (Code Composer Studio) | Fix not available | |

| MSP430 GNU Compiler (MSP430-GCC) | Fix not available |