SLLU346 April 2022 SN6507

4 EVM Configuration Options

The pin diagram of SN6507 in the DGQ package is shown in Figure 4-1.

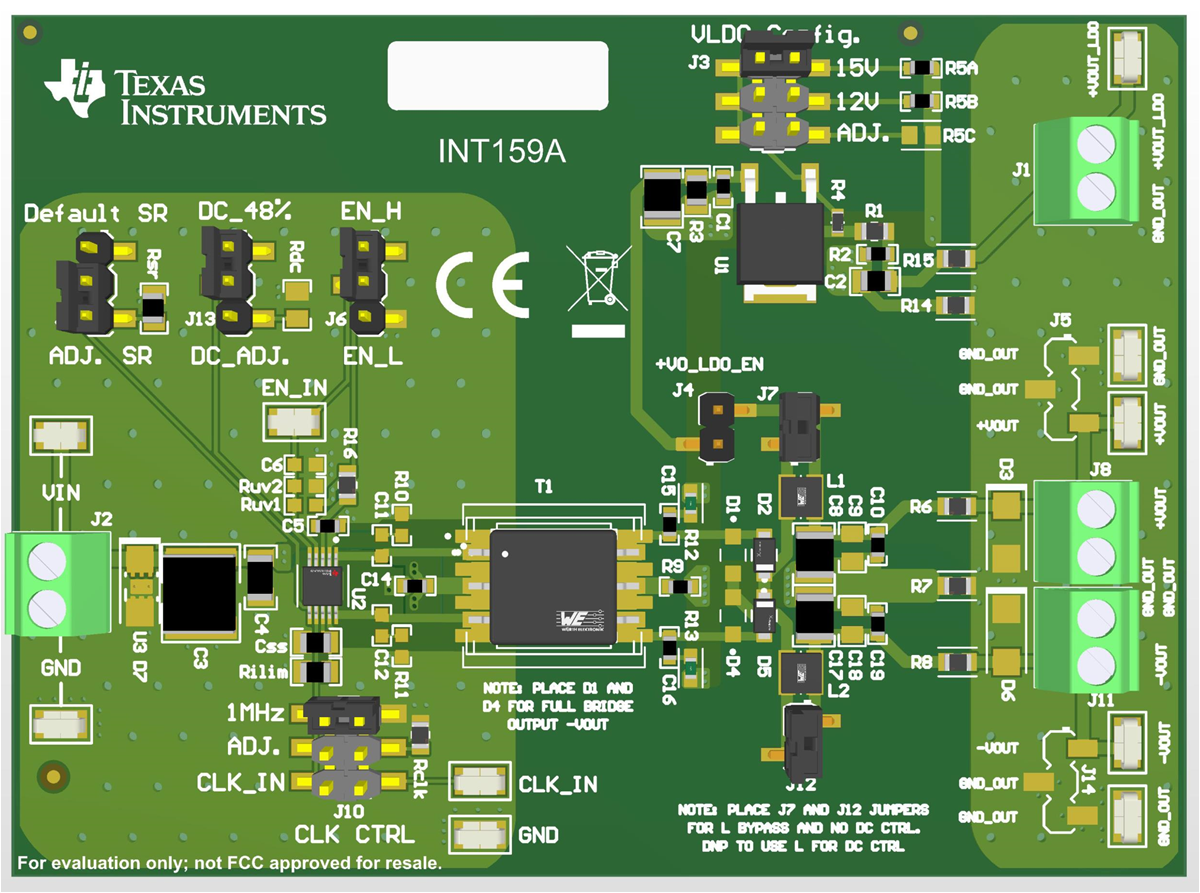

The SN6507DGQEVM is designed for flexibility in evaluation of the SN6507 device by providing placeholder options for several external components. The SN6507 pin-configurable options, snubber circuit components, full-bridge output configurations, LDO output, and the isolation transformer itself may all be adjusted using component-footprint and jumper provisions on this EVM. The transformer footprint, T1, is compatible with many commercially-available push-pull isolation transformers. The EVM PCB is shown in Figure 4-2.

Figure 4-2 SN6507DGQEVM Top View

Figure 4-2 SN6507DGQEVM Top ViewDetails for the various configuration options of the SN6507 EVM are listed below.

Pin-configurations using RCs: Configuration options for pin-adjustable features of SN6507, including Enable, UVLO, SW1/SW2 switching frequency (CLK), duty cycle control, slew rate adjustment, soft-start time, and over-current protection limit can be found in the SN6507 data sheet. Corresponding component footprints on this EVM are as follows:

-

Ruv1 and Ruv2 correspond to RENT and RENB for UVLO and EN programming

-

RDC is used for duty cycle control programming and is active when pins 2-3 of J13 are connected. If duty cycle control is used, ensure a compatible transformer is placed in footprint T1 and output inductors with sufficient inductance are populated in place of L1 (and L2 as needed)

-

RCLK can be used to program the internal CLK and is active when pins 3-4 of J10 are connected

-

RSR is used to adjust the slew rate of the switching pins, SW1 and SW2, and is active when pins 2-3 of J9 are connected

-

Rilim is used to adjust the over-current protection limit of SN6507

-

Css is used to adjust the soft start time of SN6507 during power-up

Transformer replacement: A 24 V IN to 15 V OUT transformer is included by default in place of T1. To evaluate different transformers, de-solder this transformer and replace it with a 6-pin or 8-pin push-pull transformer that is compatible with the T1 footprint.

Secondary-side snubber circuit: An RC snubber circuit of 100 Ω, 62pF is populated on R12, C15 and R13, C16 by default to help minimize electromagnetic emissions. These components are optional, so they may be replaced with other components or removed from the EVM and excluded from designs using the SN6507 device.

Primary-side snubber circuits: Primary-side snubber circuits can be placed using footprints for R10, C11 and R11, C12 to further reduce emissions. Primary-side snubber circuit values can be calculated using the steps in How to Reduce Emissions in Push-Pull Isolated Power Supplies (SLLA566).

Output rectifier: Diode placeholders D1, D2, D4, D5, and resistor R9 are included to allow system designers to experiment with the different output topologies push-pull power supplies can support. D2 and D5 are populated by default as this is the typical application topology, and some example output designs found in the SN6507 data sheet can be configured on this EVM to achieve bi-polar or voltage-doubling outputs using the “-Vout” net by populating D1 and D4 on the EVM. Make sure the output LDO, U1, is bypassed by disconnecting pins 1-2 of J4 if R9 is removed since the ISO_GND potential will be floating.

Ferrite bead options: To reduce emissions when power supply outputs are connected to long cables or have high ringing, ferrites can be soldered in place of R15, R14, R6, R7, and R8. A ferrite with 1 kΩ impedance or greater at 100 MHz like the Würth Elektroniks 742792662 is recommended.

Input-side transient protection: Provisions for a flat-clamp diode like TVS3300, U3, or a TVS diode like SMAJ36A, D7, are included to protect the power supply input from external transients above the desired power supply level.

Output-side transient protections: TVS diode placeholders D3 and D6 are included to protect the SN6507 output from external transients above the desired output power supply level.

LDO output: The included LM317A can be configured to change the regulated output voltage level by connecting either of the R5x resistors using jumper J3. When configuring the LDO, ensure the LDO input voltage is within the LDO’s recommended limits and high enough to support the desired output voltage level and the dropout voltage of the LM317A. A regulated 15 V output can be configured by connecting pins 1-2 of J3, a regulated 12 V output can be configured by connecting pins 2-3 of J3, or a custom output voltage value can be configured by connecting pins 5-6 of J3 and changing R5C to a value which meets the desired output voltage using Equation 1.

A table of calculated resistor values for R5C to achieve common voltage outputs is shown Table 4-1:

|

Desired VOUT (V) |

R4 value (Ω) |

R5C value (Ω) |

|---|---|---|

|

3.3 |

240 |

390 |

|

5 |

240 |

713 |

|

12 |

240 |

2044 |

|

15 |

240 |

2615 |

|

24 |

240 |

4326 |

|

36 |

240 |

6609 |

Jumper configurations:Table 4-2 details the jumper configuration information of the SN6507DGQEVM.

|

Connection |

Label |

Function |

|---|---|---|

|

J3 |

15 V, 12 V, ADJ. |

Connect pins 1-2, 2-3, or 5-6 of J3 to select the desired regulated output voltage of either 15 V, 12 V, or a custom value respectively between +VOUT_LDO and GND_OUT |

|

J4 |

+VO_LDO_EN |

Connect this jumper to enable the regulated output LDO, U1 |

|

J5 |

+VOUT, GND_OUT |

A surface-mount 3x1 terminal block can be soldered onto this footprint for additional measurement points of each labelled pad |

|

J6 |

EN_H, EN_L |

Connect pins 1-2 of J6 to enable or pins 2-3 of J6 to disable SN6507 respectively. Do not connect any pins of J6 if enable signals are controlling SN6507 using TP6 or if UVLO is configured using Ruv1 and Ruv2 |

|

J7 |

NOTE |

Connect pins 1-2 of J7 to bypass output inductor L1 if duty cycle control is not used. Disconnect these pins to use output inductor L1 for duty cycle control |

|

J9 |

Default SR, ADJ. SR |

Connect pins 1-2 of J9 to use the default switching slew rate of SN6507 or connect pins 2-3 to adjust the slew rate using RSR. If J9 is completely disconnected, SN6507 will use its default slew rate |

|

J10 |

1 MHz, ADJ., CLK_IN |

Connect pins 5-6 of J10 for SN6507 to use the internal 1 MHz clock for switching SW1 and SW2. Connect pins 3-4 of J10 to use an adjustable clock value based on the resistance of RCLK. Connect pins 1-2 of J10 to use an external clock input connected to the test point CLK_IN, described as SYNC Mode in Section 7.4.4 of the SN6507 datasheet. |

|

J12 |

NOTE |

Connect pins 1-2 of J12 to bypass output inductor L2 if duty cycle control is not used. Disconnect these pins to use output inductor L2 for duty cycle control |

|

J13 |

DC_48%, DC_ADJ. |

Connect pins 1-2 of J13 to use the default switching duty cycle of SN6507 or connect pins 2-3 to adjust the slew rate using RDC. If J13 is completely disconnected, SN6507 will use its default switching duty cycle |

|

J14 |

-VOUT, GND_OUT |

A surface-mount 3x1 terminal block can be soldered onto this footprint for additional measurement points of each labelled pad |