SLOS782C July 2013 – May 2017 TAS5760L

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Device Comparison Table

- 6 Pin Configuration and Functions

-

7 Specifications

- 7.1 Absolute Maximum Ratings

- 7.2 ESD Ratings

- 7.3 Recommended Operating Conditions

- 7.4 Thermal Information

- 7.5 Digital I/O Pins

- 7.6 Master Clock

- 7.7 Serial Audio Port

- 7.8 Protection Circuitry

- 7.9 Speaker Amplifier in All Modes

- 7.10 Speaker Amplifier in Stereo Bridge-Tied Load (BTL) Mode

- 7.11 Speaker Amplifier in Mono Parallel Bridge-Tied Load (PBTL) Mode

- 7.12 I²C Control Port

- 7.13 Typical Idle, Mute, Shutdown, Operational Power Consumption

- 7.14 Typical Speaker Amplifier Performance Characteristics (Stereo BTL Mode)

- 7.15 Typical Performance Characteristics (Mono PBTL Mode)

- 8 Parameter Measurement Information

-

9 Detailed Description

- 9.1 Overview

- 9.2 Functional Block Diagram

- 9.3 Feature Description

- 9.4

Device Functional Modes

- 9.4.1

Hardware Control Mode

- 9.4.1.1 Speaker Amplifier Shut Down (SPK_SD Pin)

- 9.4.1.2 Serial Audio Port in Hardware Control Mode

- 9.4.1.3 Soft Clipper Control (SFT_CLIP Pin)

- 9.4.1.4 Speaker Amplifier Switching Frequency Select (FREQ/SDA Pin)

- 9.4.1.5 Parallel Bridge Tied Load Mode Select (PBTL/SCL Pin)

- 9.4.1.6 Speaker Amplifier Sleep Enable (SPK_SLEEP/ADR Pin)

- 9.4.1.7 Speaker Amplifier Gain Select (SPK_GAIN [1:0] Pins)

- 9.4.1.8 Considerations for Setting the Speaker Amplifier Gain Structure

- 9.4.2 Software Control Mode

- 9.4.1

Hardware Control Mode

- 9.5

Register Maps

- 9.5.1 Control Port Registers - Quick Reference

- 9.5.2

Control Port Registers - Detailed Description

- 9.5.2.1 Device Identification Register (0x00)

- 9.5.2.2 Power Control Register (0x01)

- 9.5.2.3 Digital Control Register (0x02)

- 9.5.2.4 Volume Control Configuration Register (0x03)

- 9.5.2.5 Left Channel Volume Control Register (0x04)

- 9.5.2.6 Right Channel Volume Control Register (0x05)

- 9.5.2.7 Analog Control Register (0x06)

- 9.5.2.8 Reserved Register (0x07)

- 9.5.2.9 Fault Configuration and Error Status Register (0x08)

- 9.5.2.10 Reserved Controls (9 / 0x09) - (15 / 0x0F)

- 9.5.2.11 Digital Clipper Control 2 Register (0x10)

- 9.5.2.12 Digital Clipper Control 1 Register (0x11)

-

10Application and Implementation

- 10.1 Application Information

- 10.2

Typical Applications

- 10.2.1 Stereo BTL Using Software Control

- 10.2.2 Stereo BTL Using Hardware Control

- 10.2.3 Mono PBTL Using Software Control

- 10.2.4 Mono PBTL Using Hardware Control

- 10.2.5 Stereo BTL Using Software Control, 32-Pin DAP Package Option

- 10.2.6 Stereo BTL Using Hardware Control, 32-Pin DAP Package Option

- 10.2.7 Mono PBTL Using Software Control, 32-Pin DAP Package Option

- 10.2.8 Mono PBTL Using Hardware Control, 32-Pin DAP Package Option

- 11Power Supply Recommendations

- 12Layout

- 13Device and Documentation Support

- 14Mechanical, Packaging, and Orderable Information

1 Features

- Audio I/O Configuration:

- General Operational Features:

- Selectable Hardware or Software Control

- Integrated Digital Output Clipper

- Programmable I²C Address (1101100[R/W] or 1101101[R/W])

- Closed-Loop Amplifier Architecture

- Adjustable Switching Frequency for Speaker Amplifier

-

Robustness Features:

- Clock Error, DC, and Short-Circuit Protection

- Overtemperature and Programmable Overcurrent Protection

- Audio Performance (PVDD = 12 V, RSPK = 8 Ω, SPK_GAIN[1:0] Pins = 01)

2 Applications

- LCD/LED TV and Multipurpose Monitors

- Sound Bars, Docking Stations, PC Audio

- General-Purpose Audio Equipment

3 Description

The TAS5760L is a stereo I2S input device which includes hardware and software (I²C) control modes, integrated digital clipper, several gain options, and a wide power supply operating range to enable use in a multitude of applications. The TAS5760L operates with a nominal supply voltage from 4.5 to 15 VDC.

An optimal mix of thermal performance and device cost is provided in the 120-mΩ RDS(ON) of the output MOSFETs. Additionally, a thermally enhanced 48-Pin TSSOP provides excellent operation in the elevated ambient temperatures found in modern consumer electronic devices.

The entire TAS5760xx family is pin-to-pin compatible in the 48-Pin TSSOP package. Alternatively, to achieve the smallest possible solutions size for applications where pin-to-pin compatibility and a headphone or line driver are not required, a 32-Pin TSSOP package is offered for the TAS5760M and TAS5760L devices. The I2C register map in all of the TAS5760xx devices are identical, to ensure low development overhead when choosing between devices based upon system-level requirements.

Device Information(1)

| PART NUMBER | PACKAGE | BODY SIZE (NOM) |

|---|---|---|

| TAS5760L | HTSSOP (48) | 12.50 mm × 6.10 mm |

| HTSSOP (32) | 11 mm × 6.2 mm |

- For all available packages, see the orderable addendum at the end of the datasheet.

Functional Block Diagram

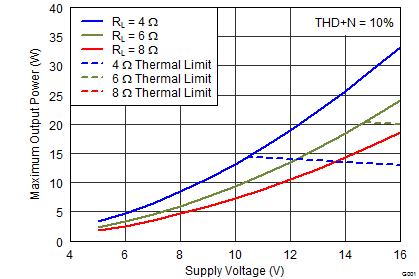

Output Power vs PVDD

NOTE:

Thermal Limits were determined via the TAS5760xxEVM