CVBUS = 2*10µF,

CPMID= 3*10µF, CSYS = 5*10µF, CBAT = 2*10µF, L1

= 1µH (SPM6530T-1R0M120) and L2 = 2.2µH (WE-LHMI-74437346022)

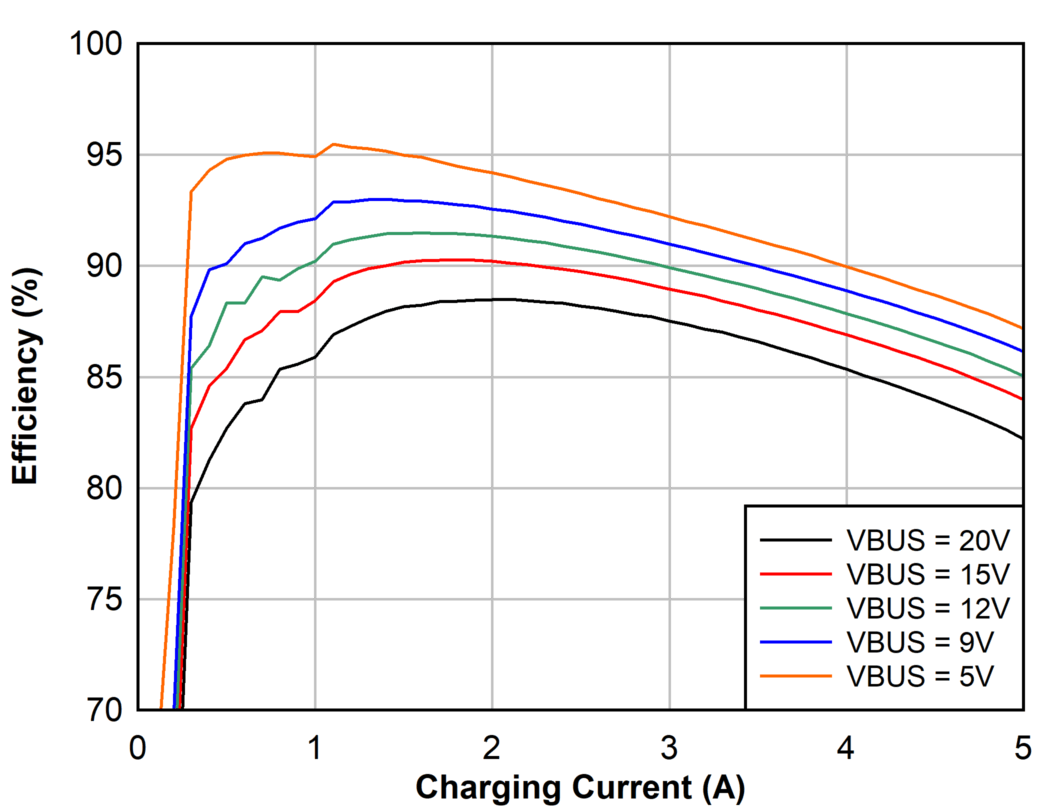

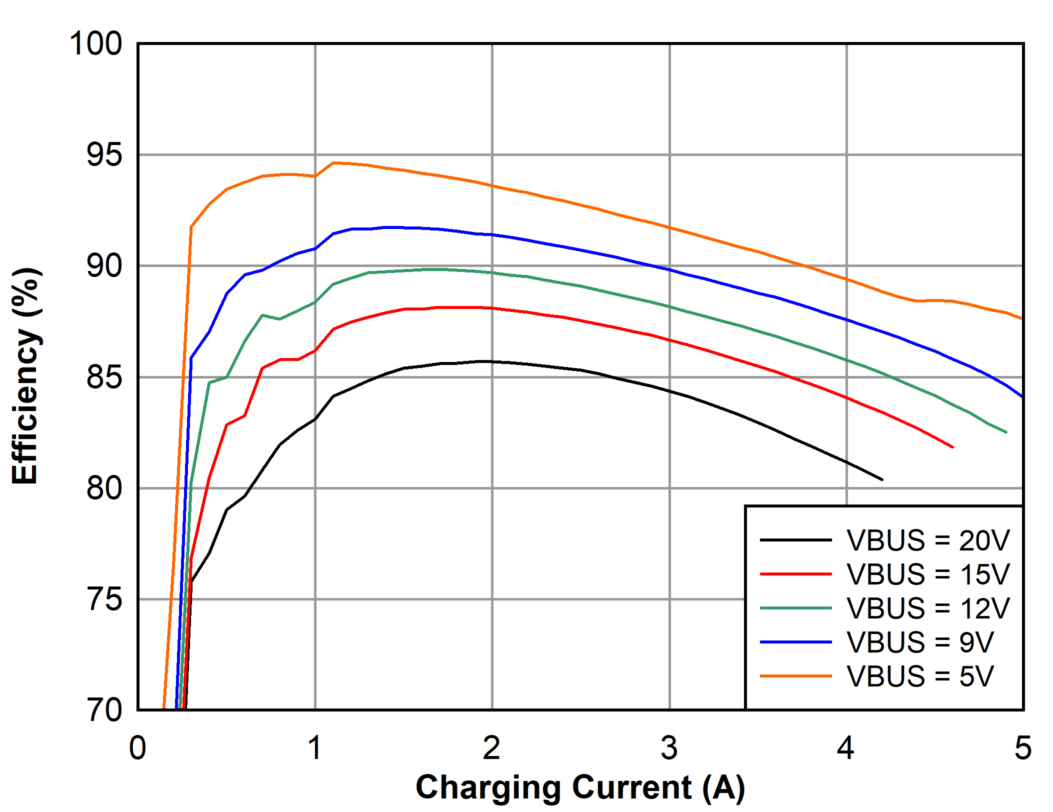

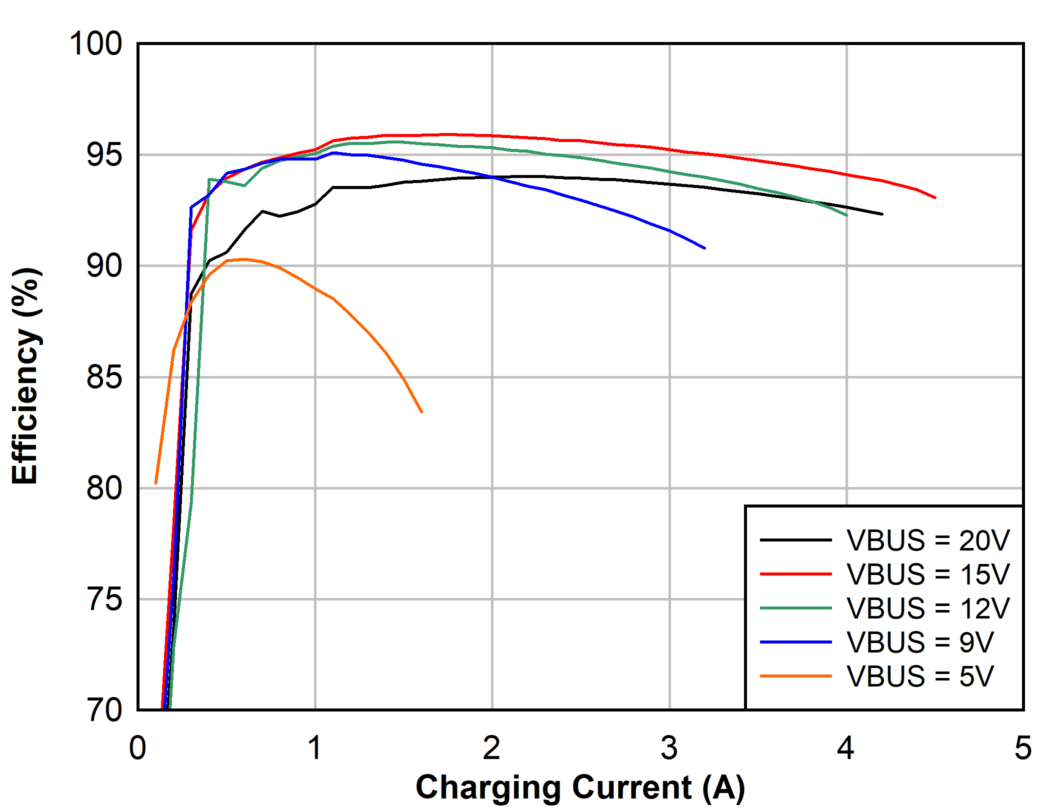

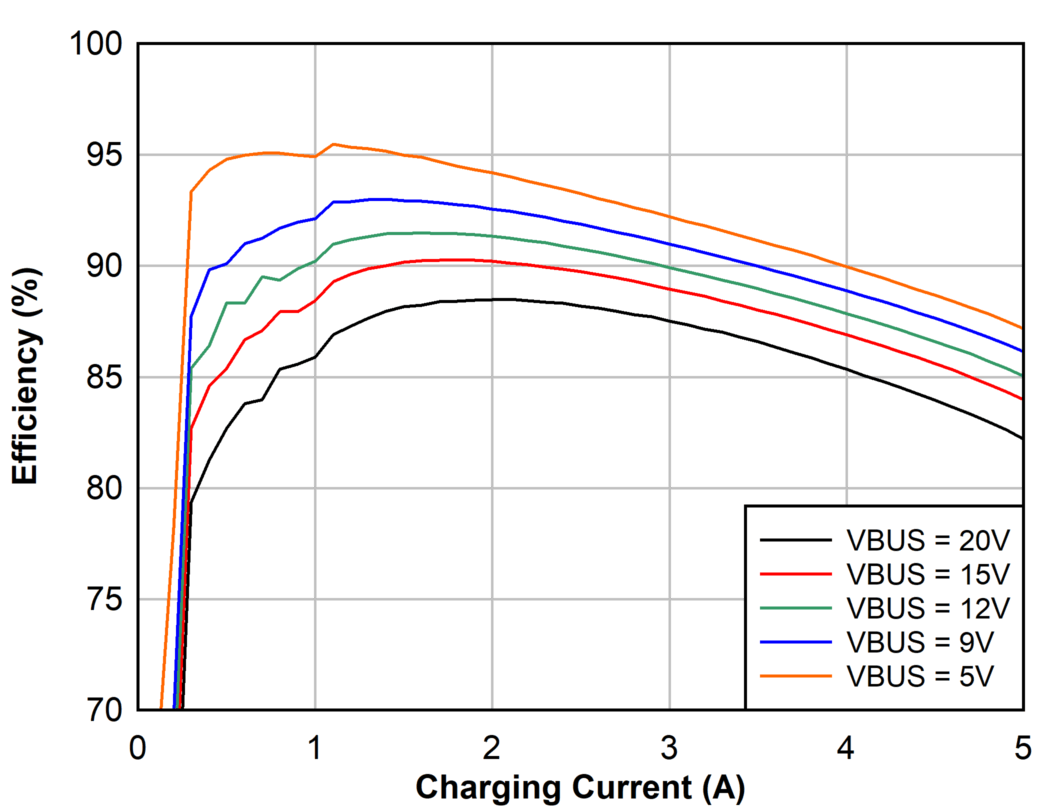

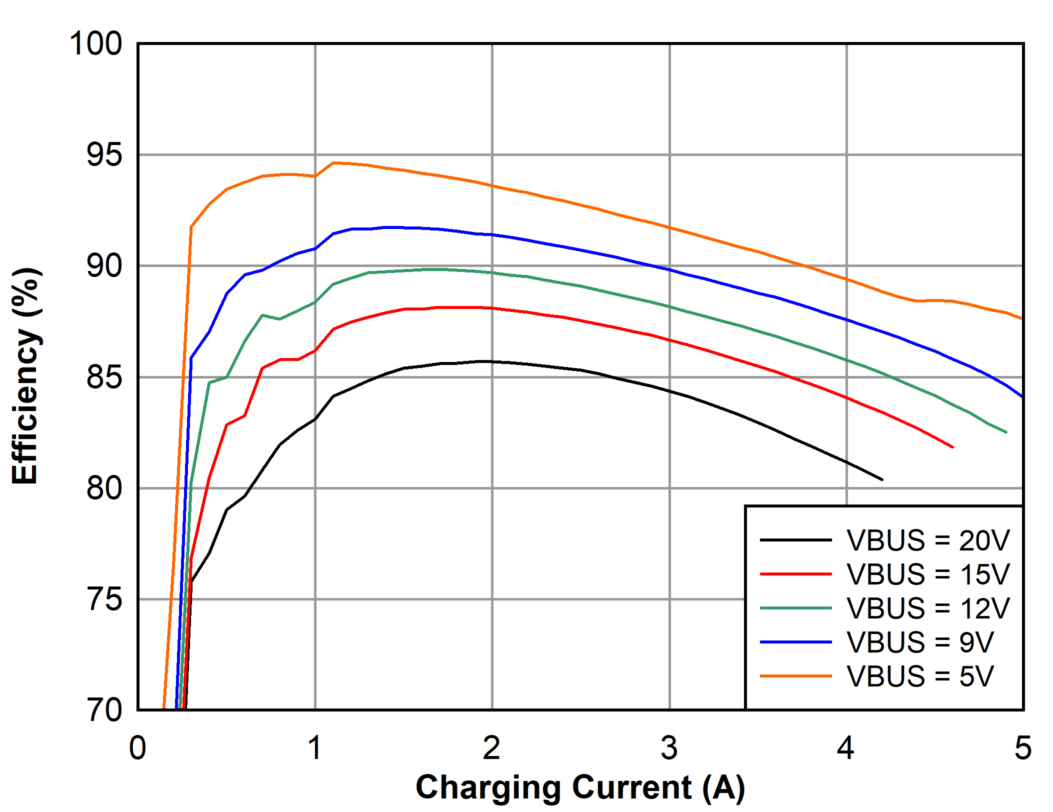

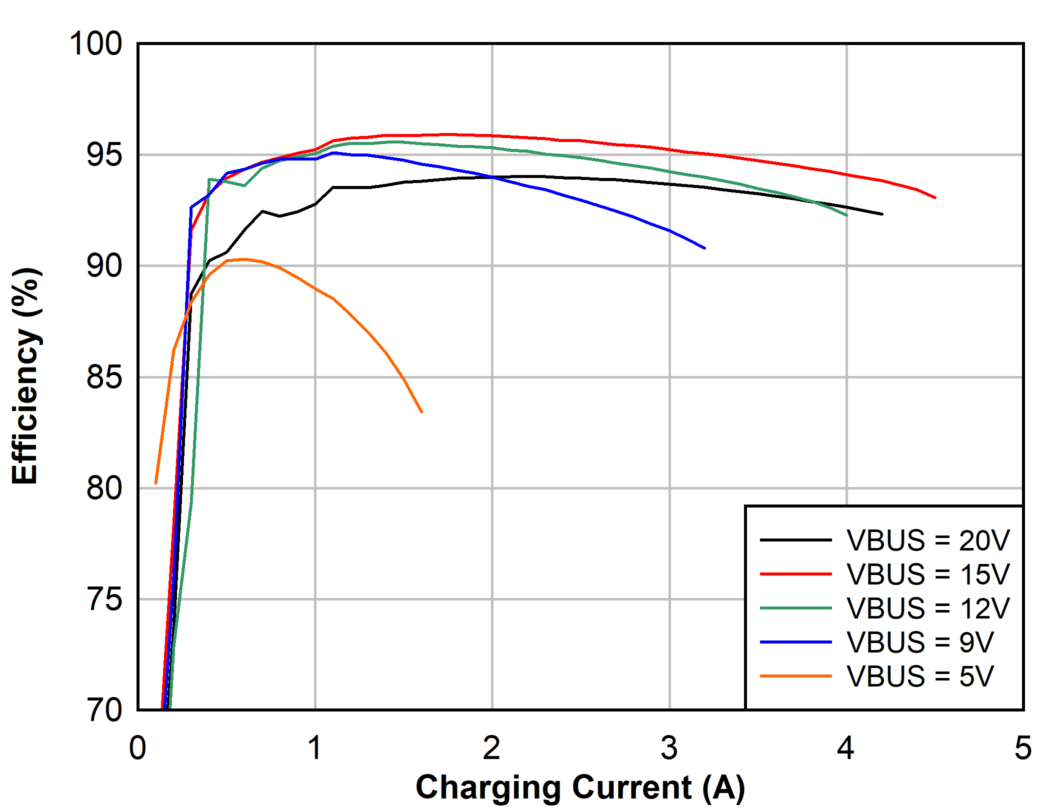

| VBAT

= 4V, Fsw = 750 kHz with L2 = 2.2µH, PFM

disabled |

Figure 8-1 1s

Battery Charge Efficiency, 750 kHz

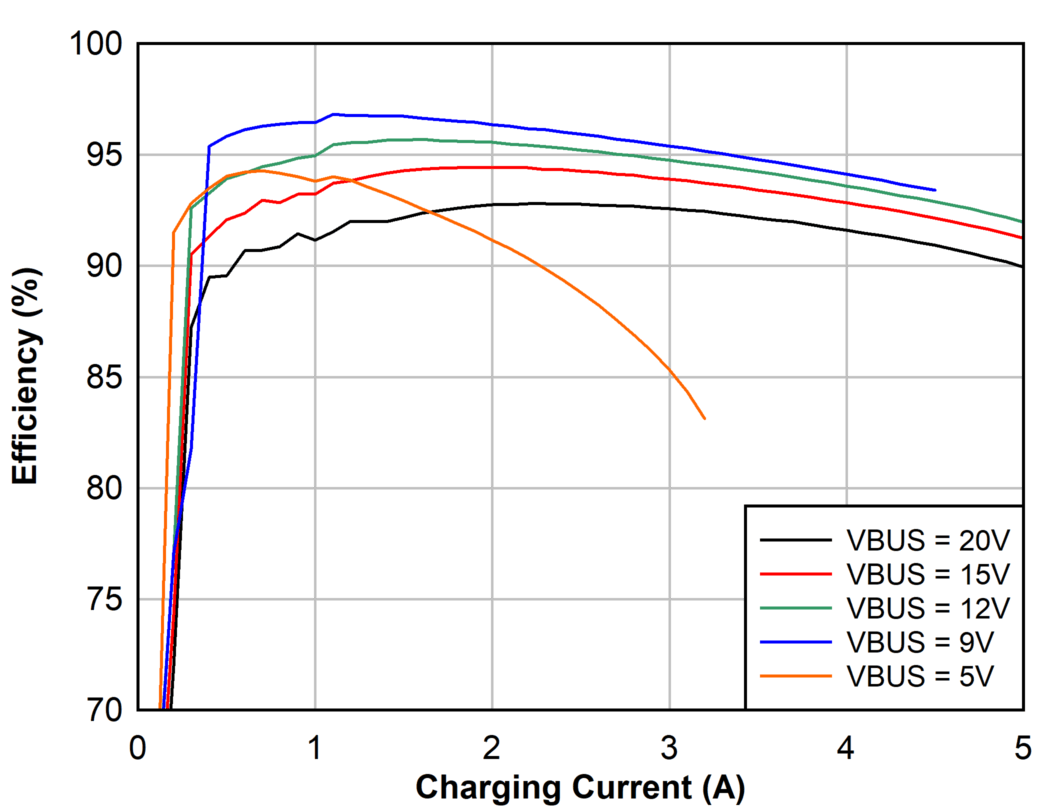

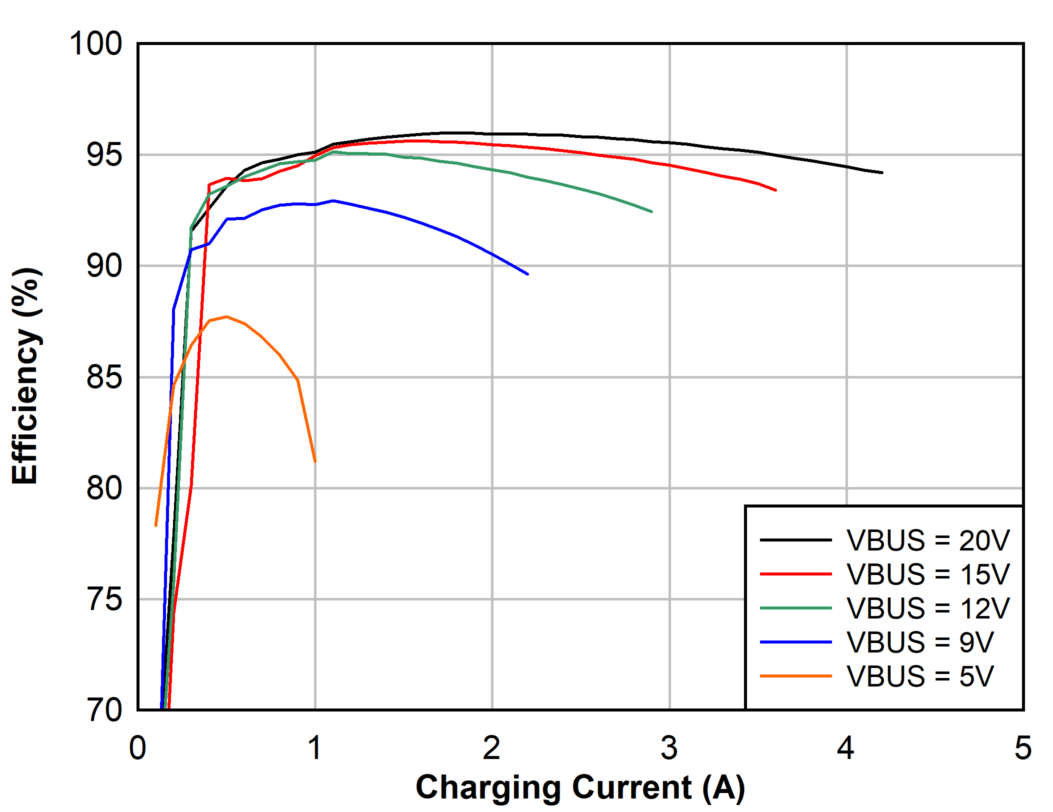

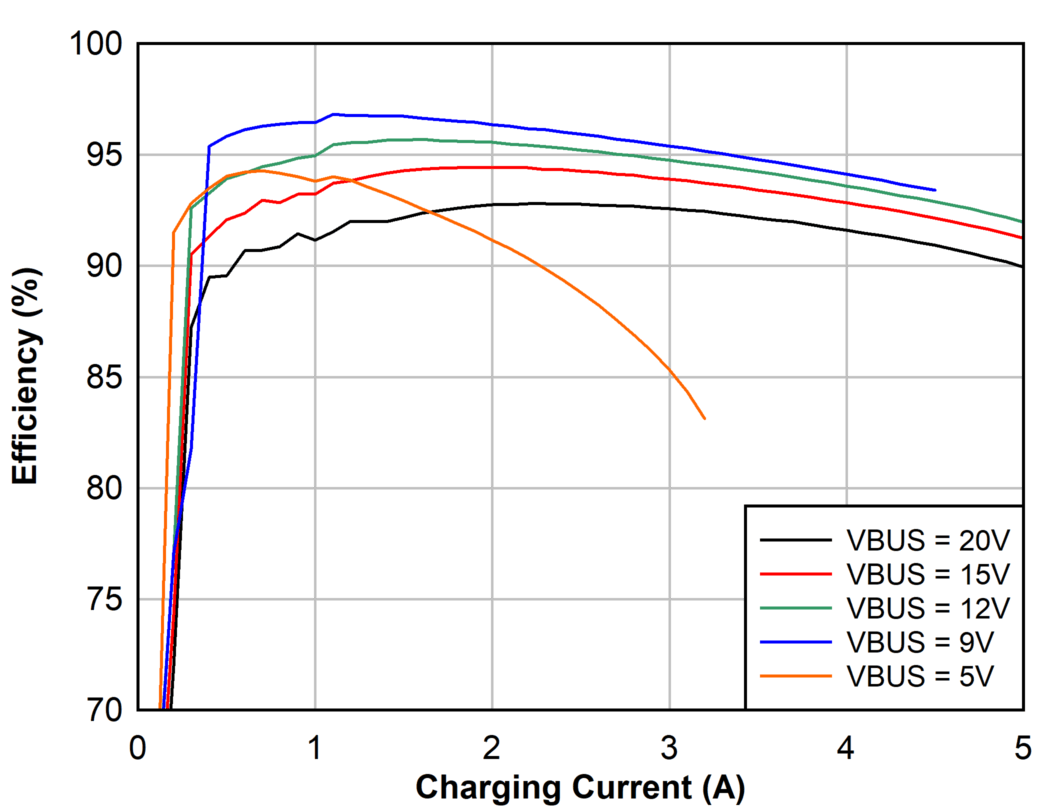

| VBAT

= 8V, Fsw = 750 kHz with L2 = 2.2µH, PFM

disabled |

Figure 8-3 2s

Battery Charge Efficiency, 750 kHz

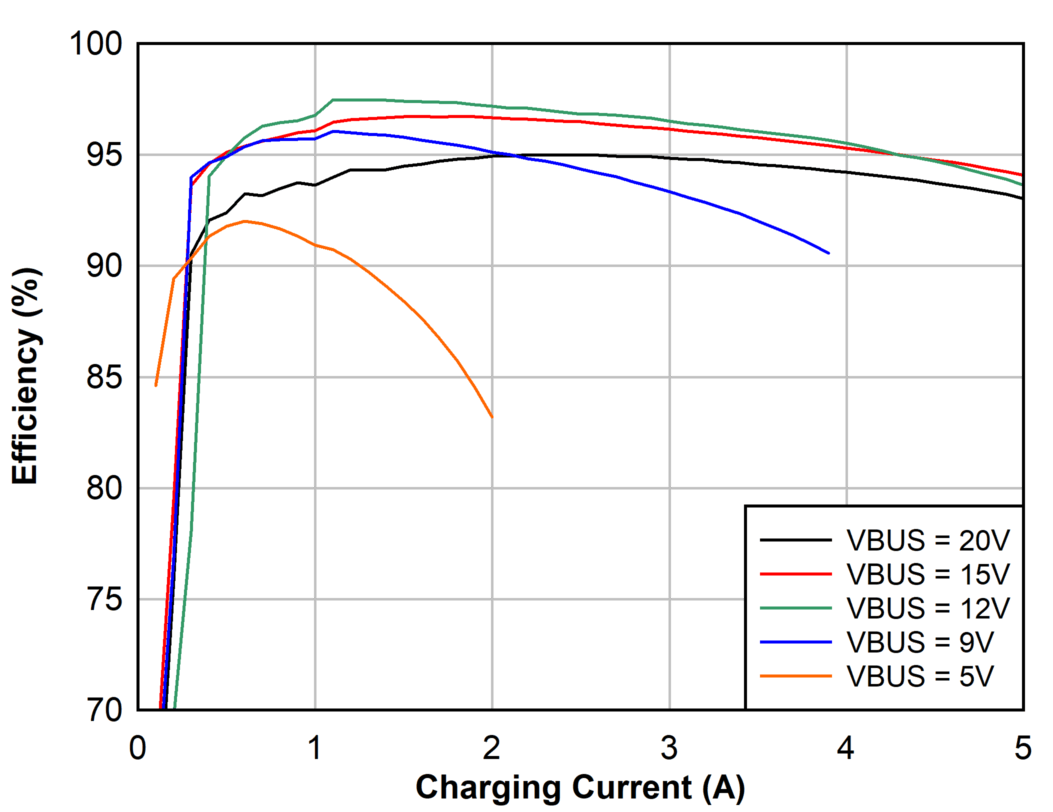

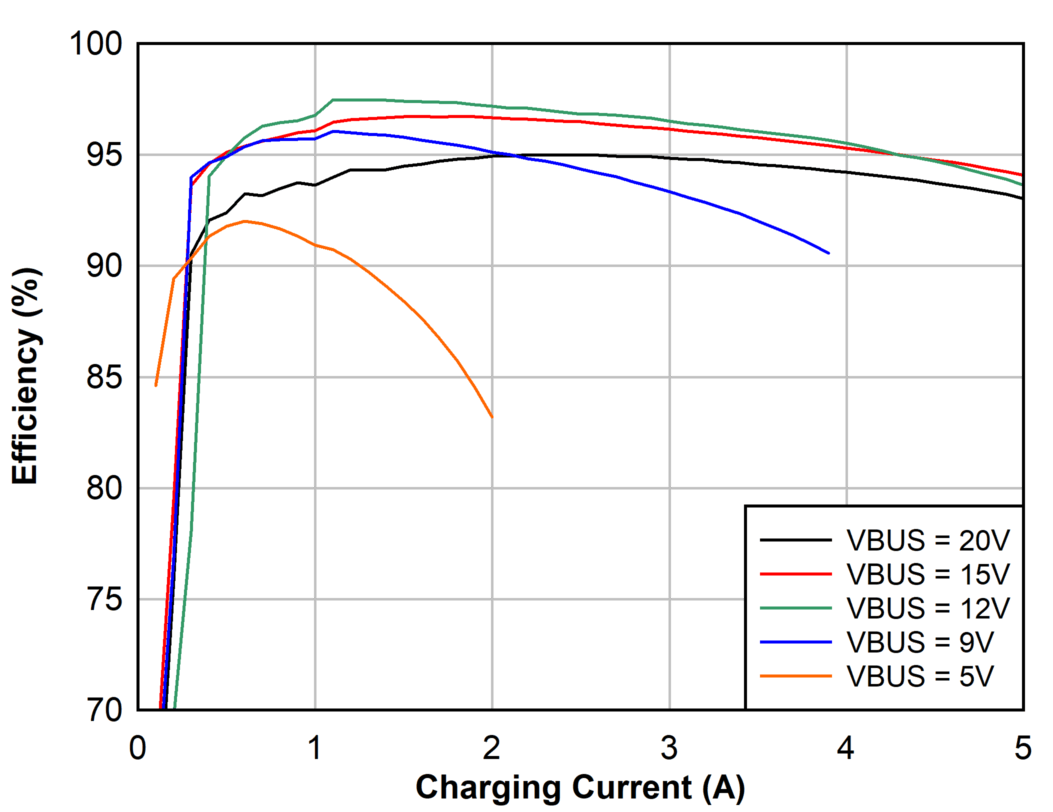

| VBAT

= 12V, Fsw = 750 kHz with L2 = 2.2µH, PFM

disabled |

Figure 8-5 3s

Battery Charge Efficiency, 750 kHz

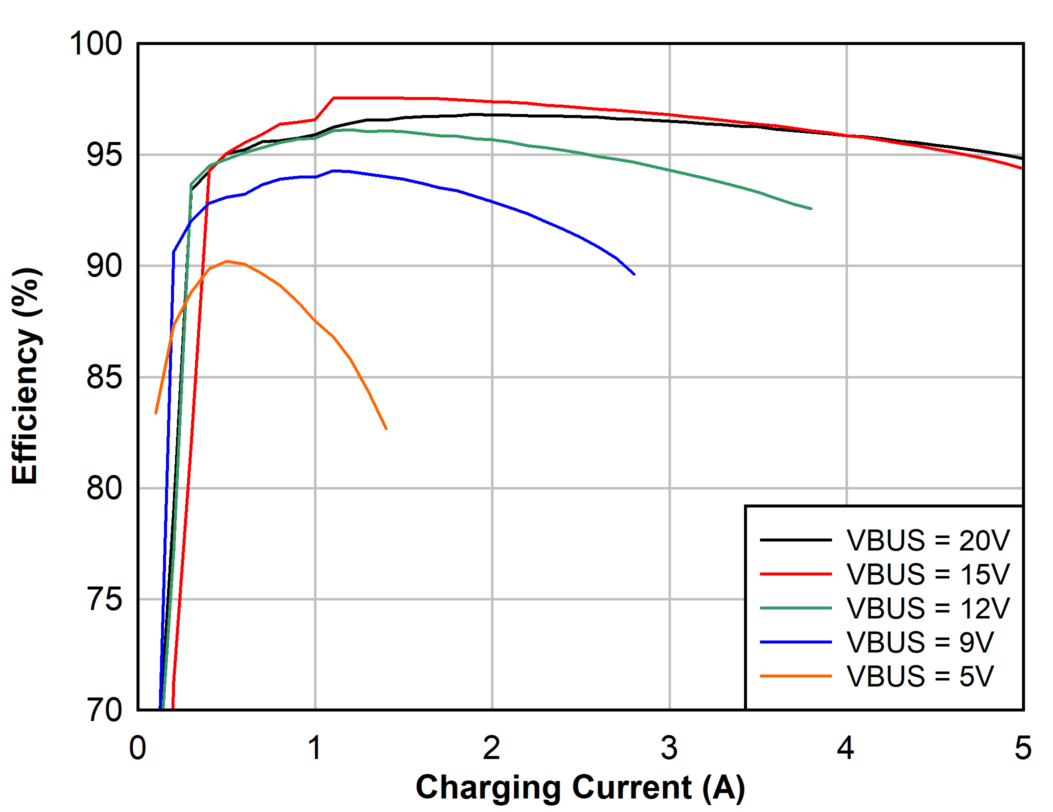

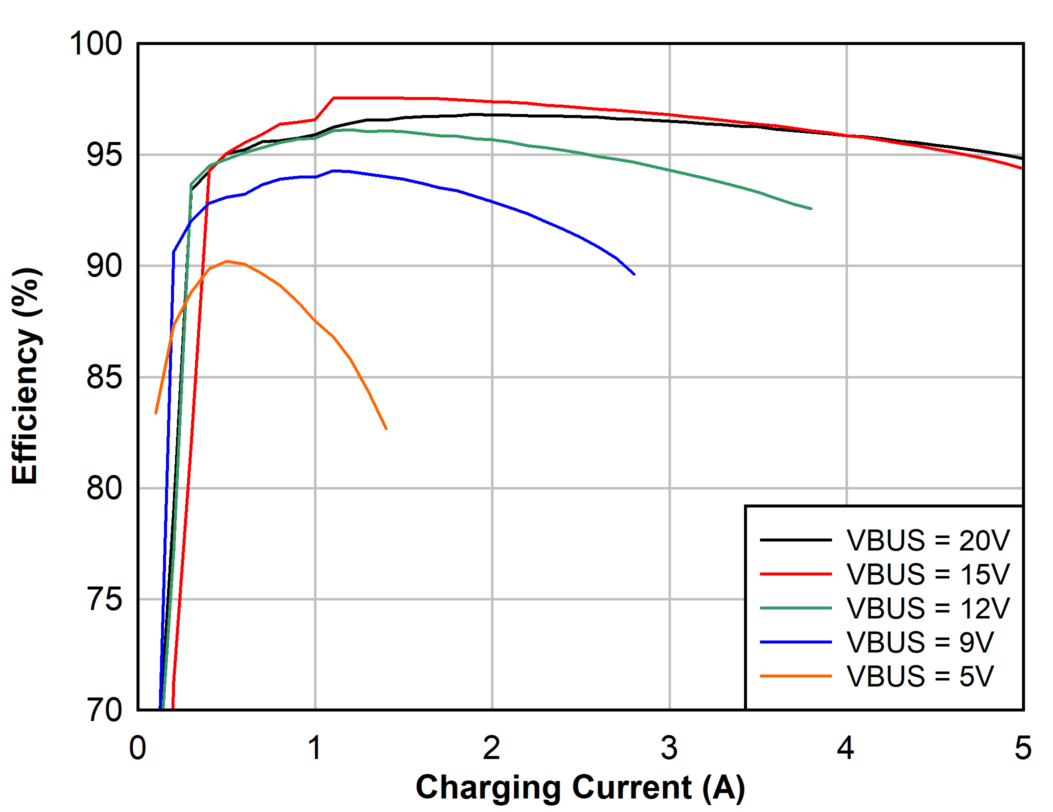

| VBAT

= 16V, Fsw = 750 kHz with L2 = 2.2µH, PFM

disabled |

Figure 8-7 4s

Battery Charge Efficiency, 750 kHz

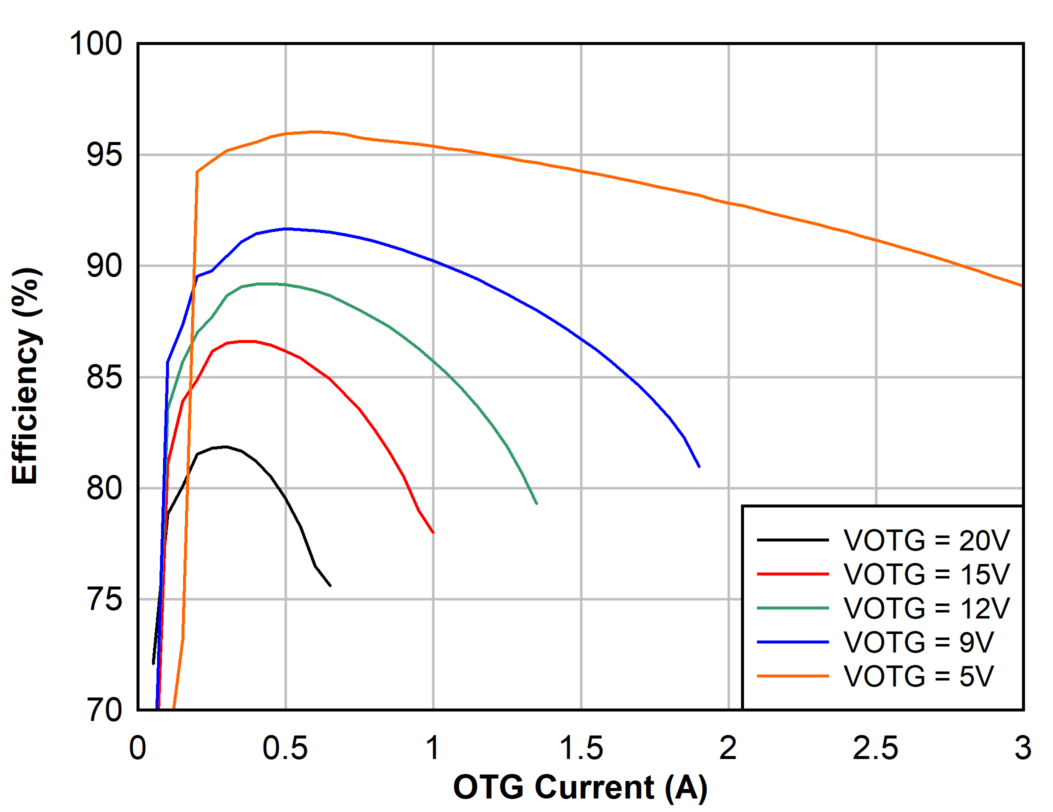

| VBAT

= 4.2V, Fsw = 750 kHz with L2 = 2.2 µH, PFM

disabled |

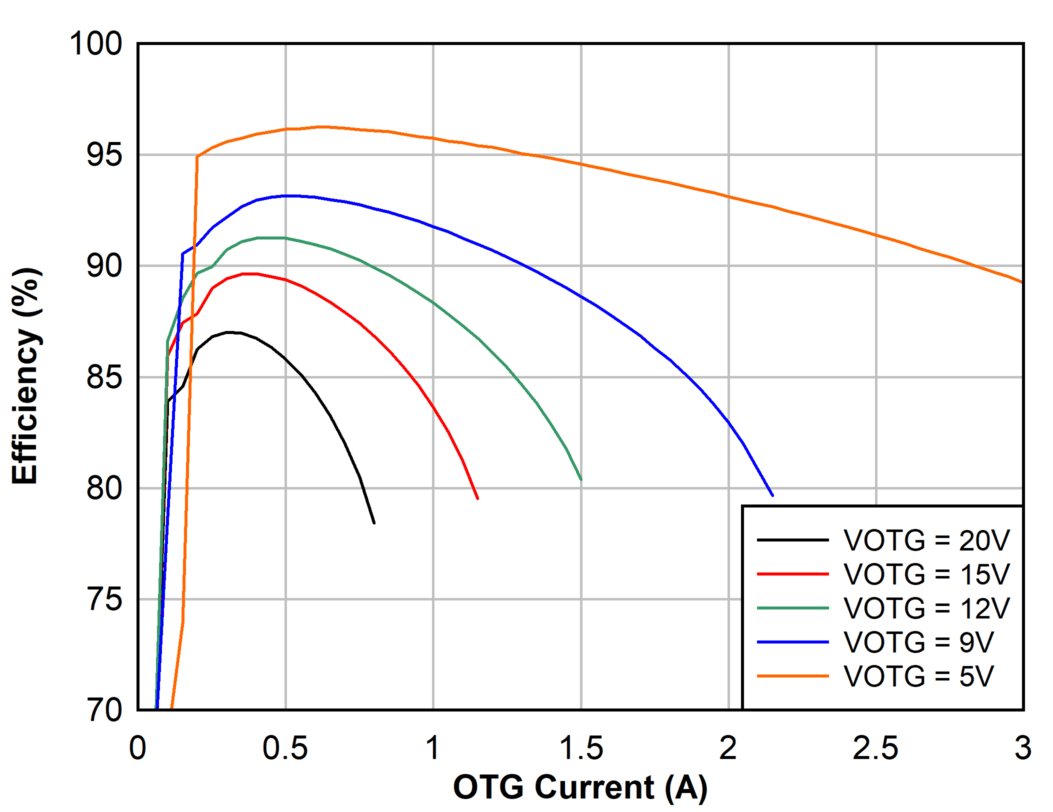

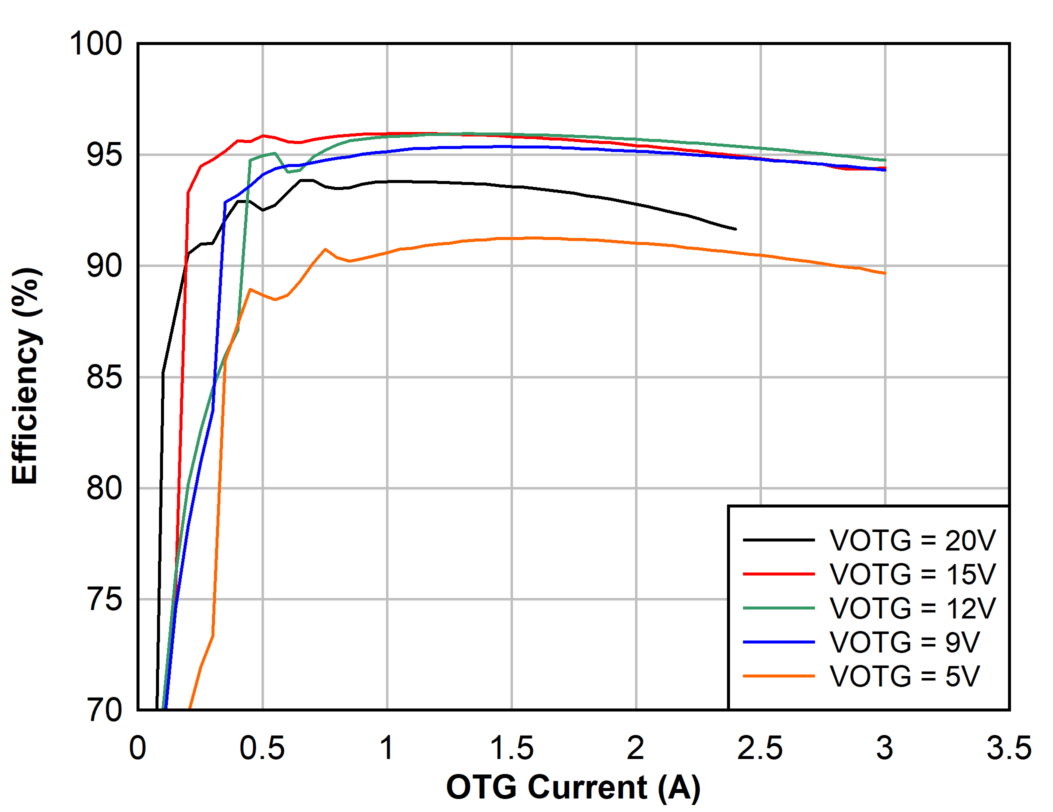

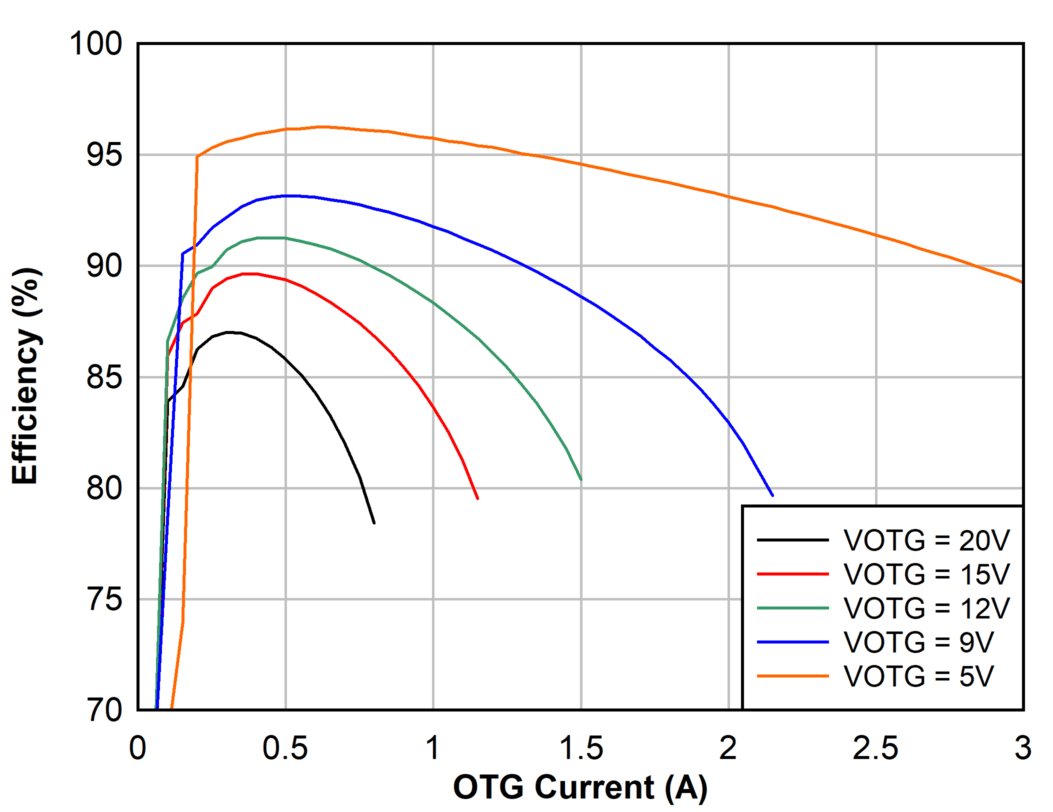

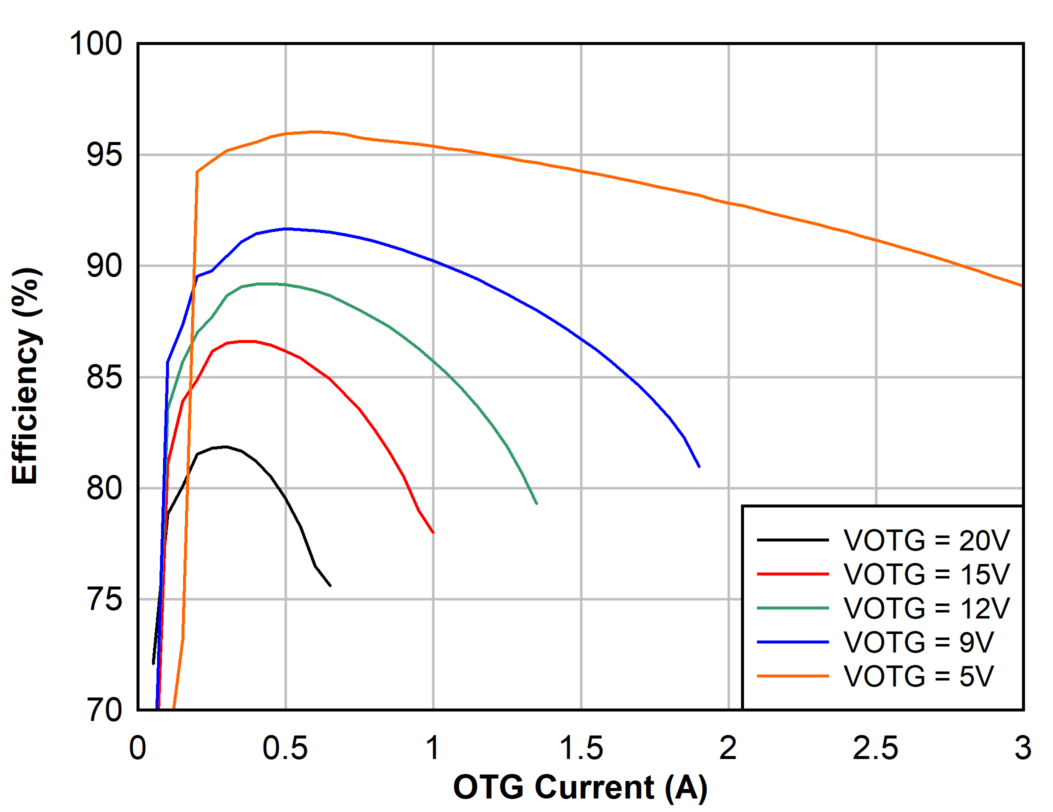

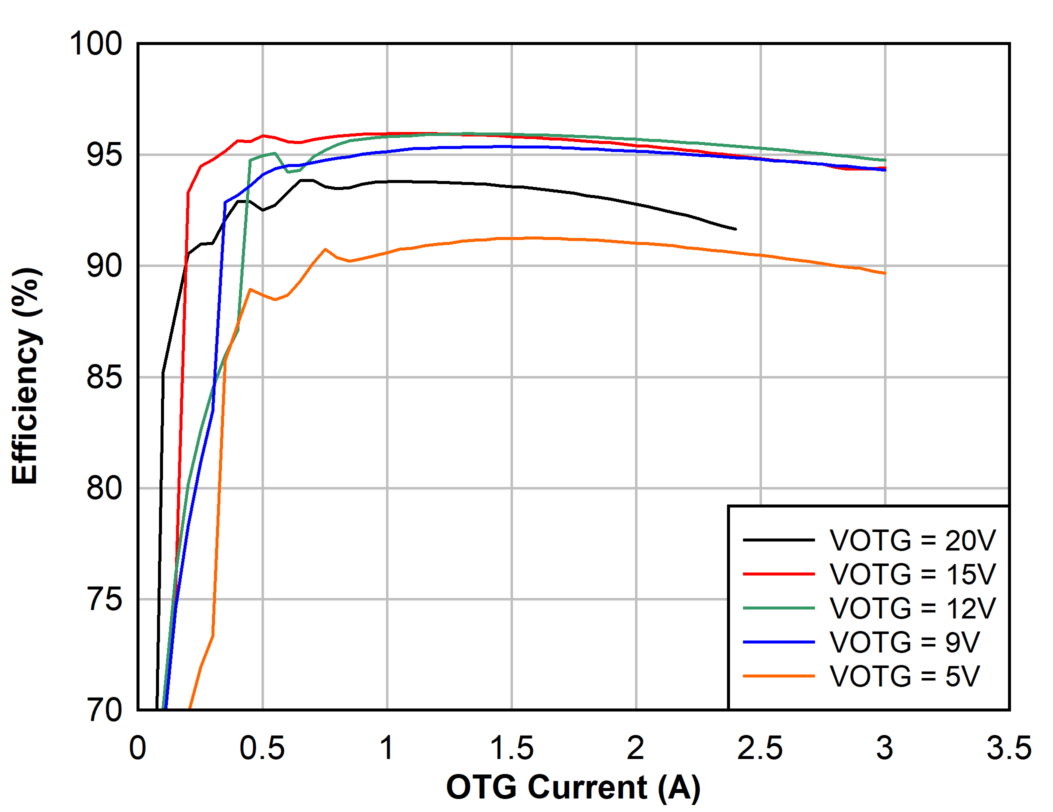

Figure 8-9 1s

Battery OTG Efficiency, 750 kHz

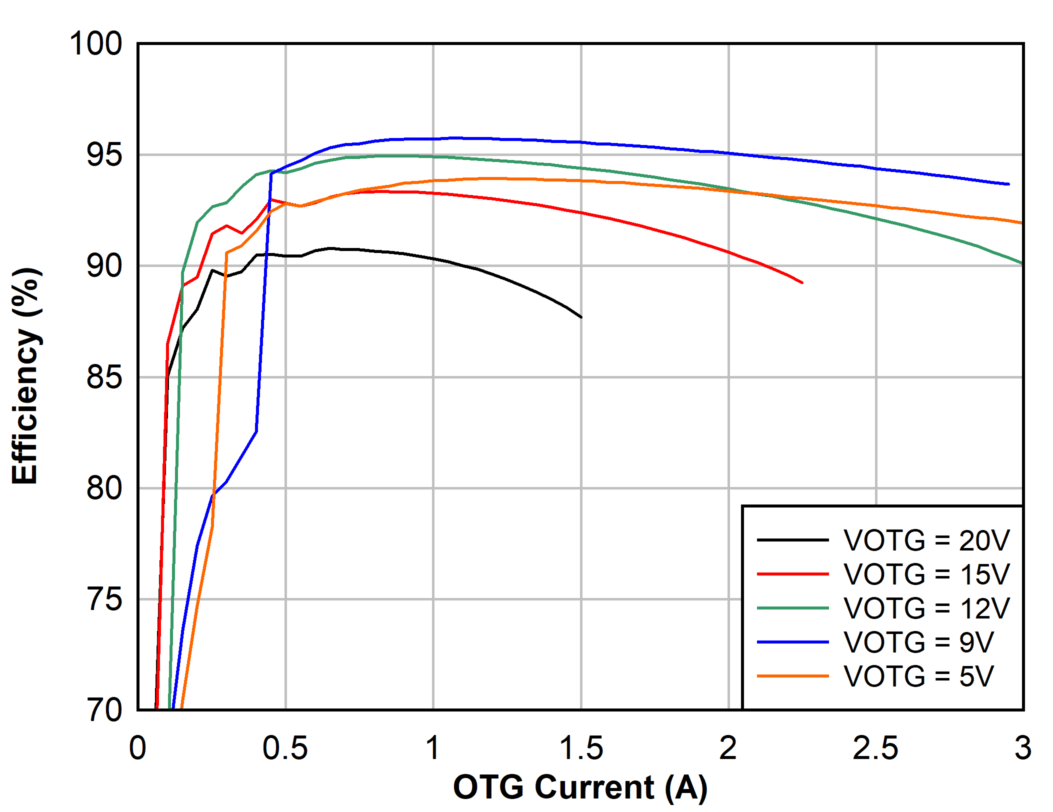

| VBAT

= 8.4V, Fsw = 750 kHz with L2 = 2.2µH, PFM

disabled |

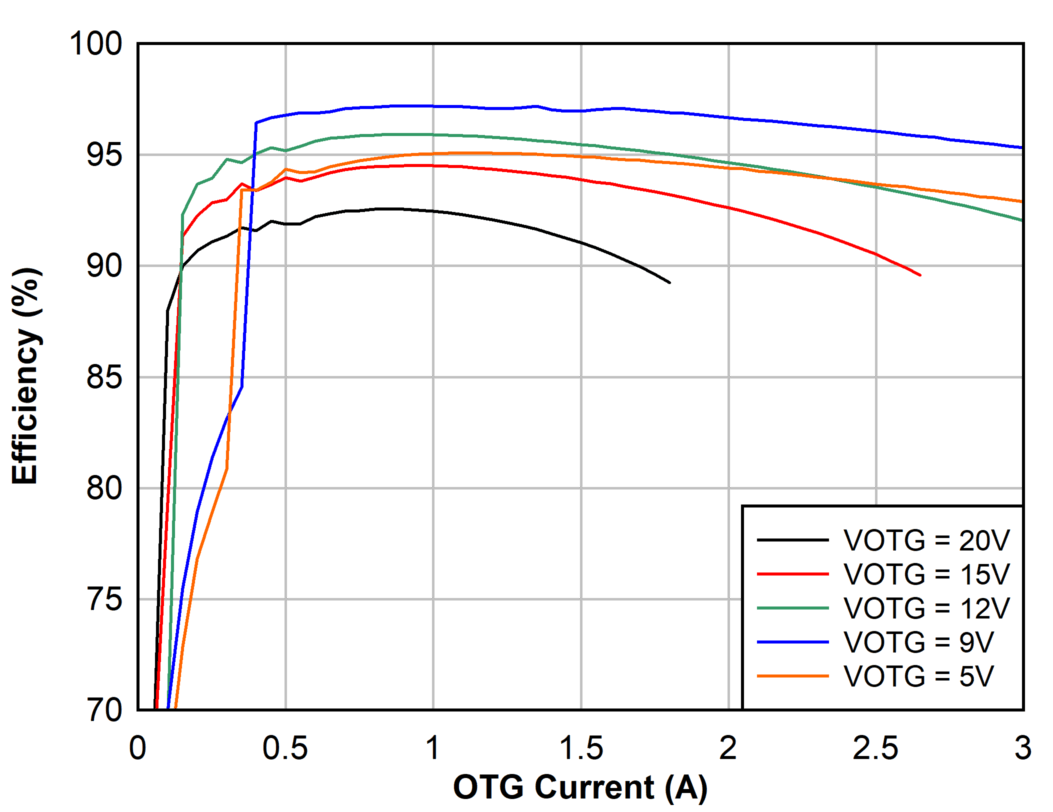

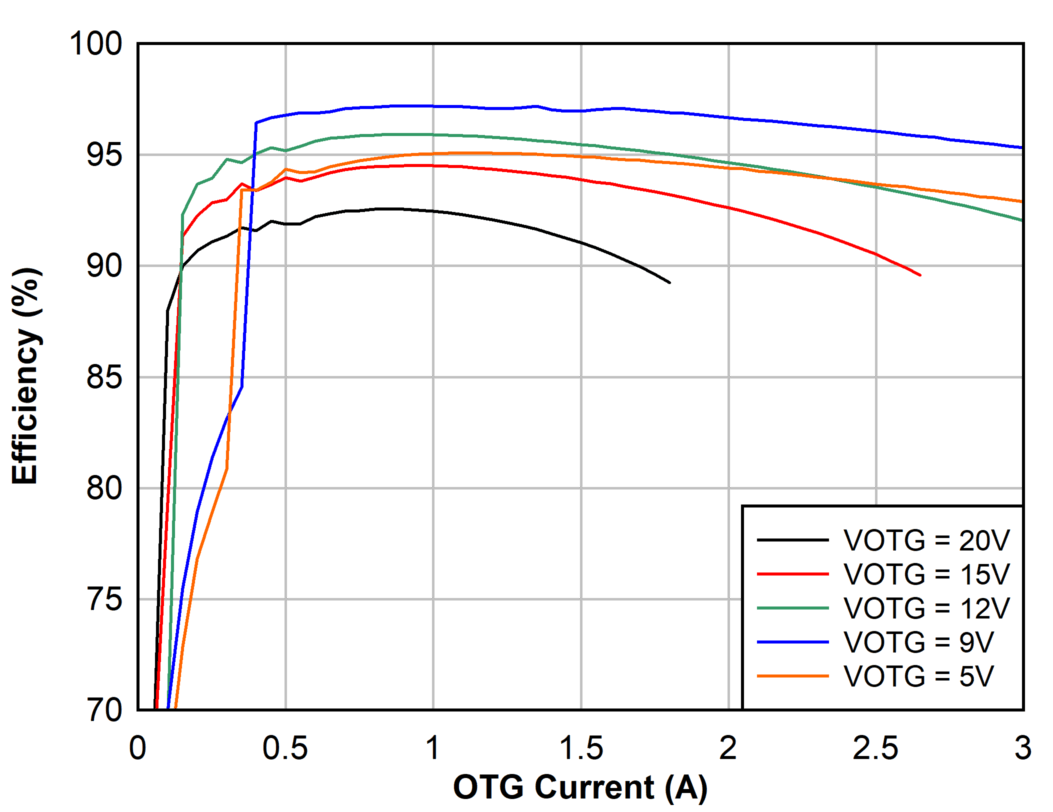

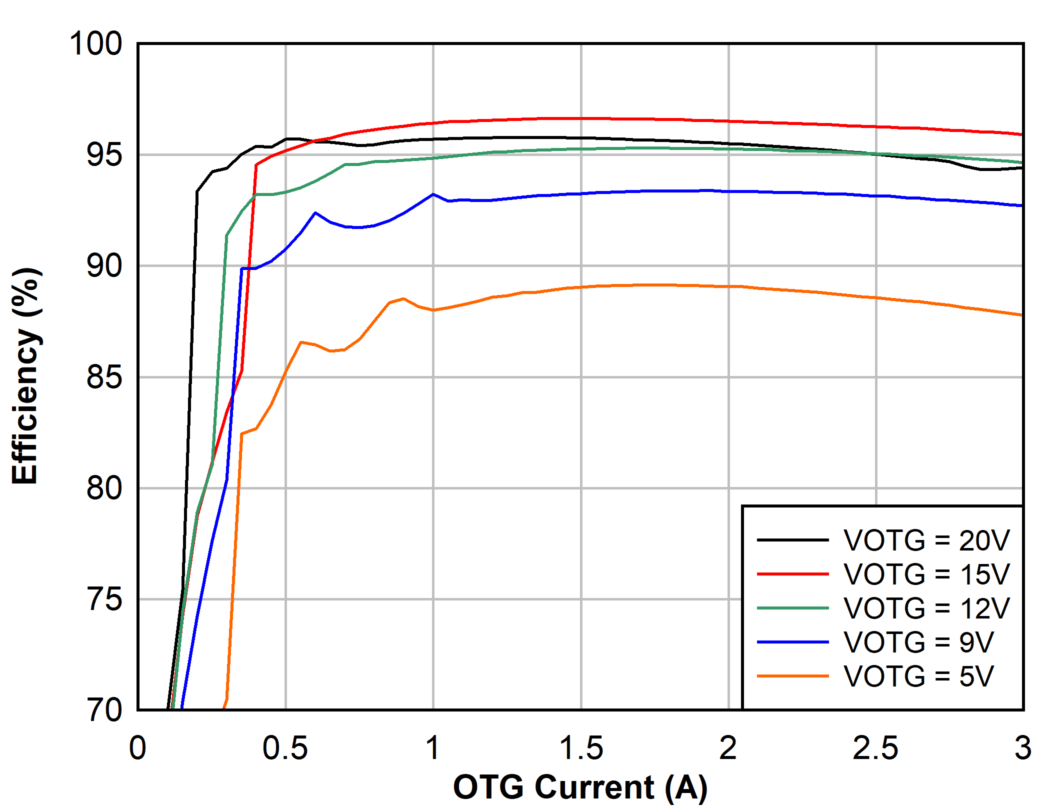

Figure 8-11 2s

Battery OTG Efficiency, 750 kHz

| VBAT

= 12.6V, Fsw = 750 kHz with L2 = 2.2µH, PFM

disabled |

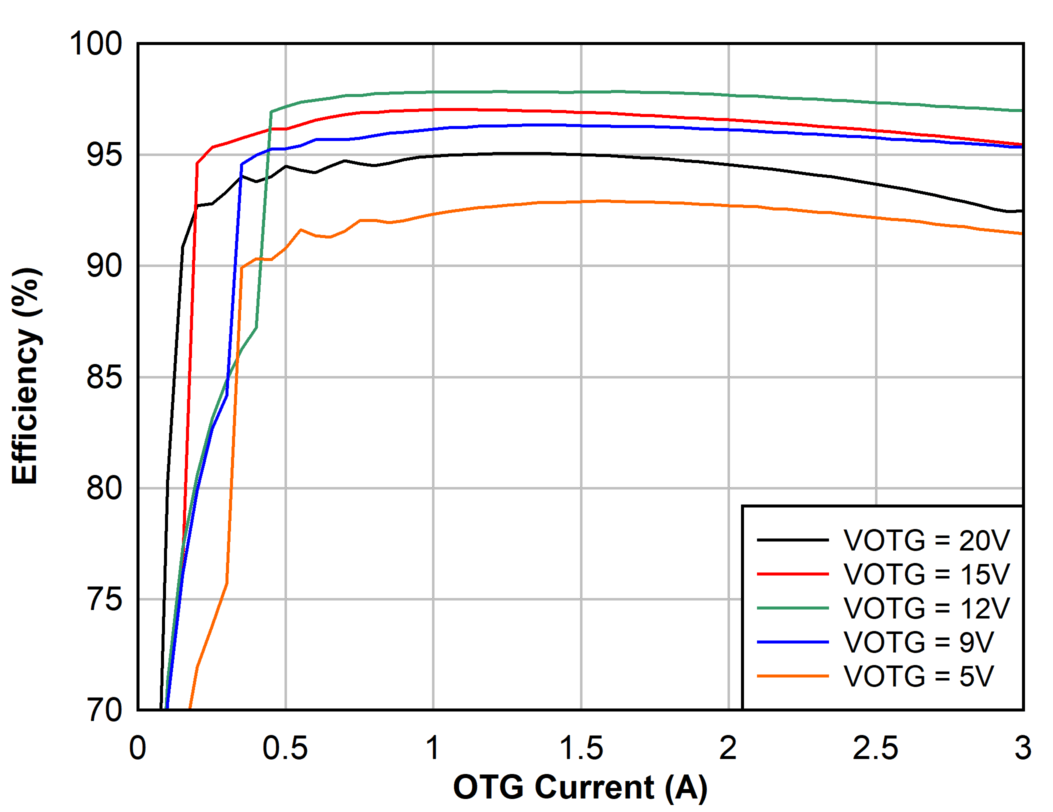

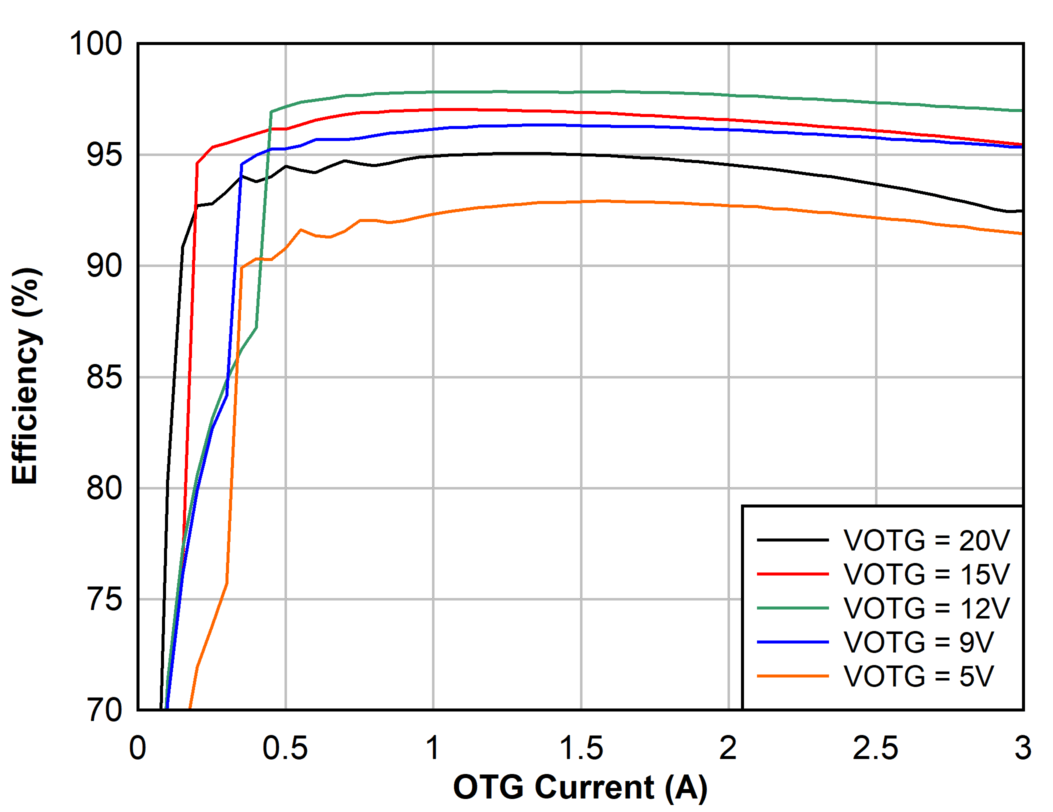

Figure 8-13 3s

Battery OTG Efficiency, 750 kHz

| VBAT

= 16.8V, Fsw = 750 kHz with L2 = 2.2µH, PFM

disabled |

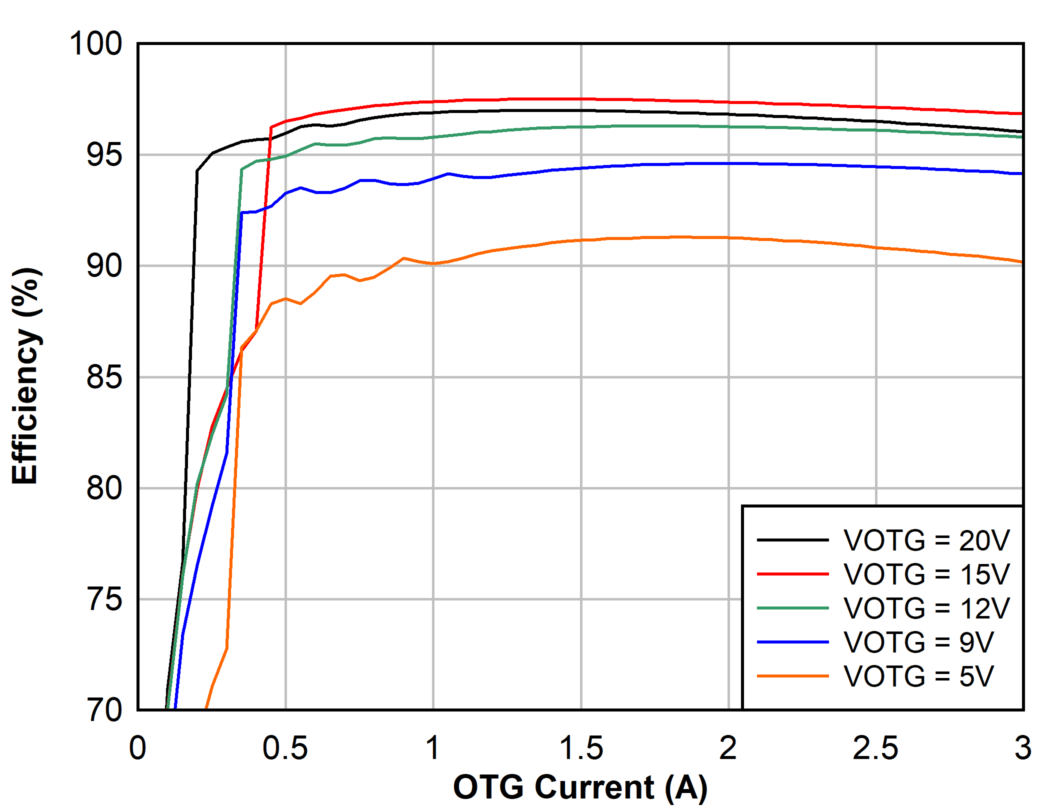

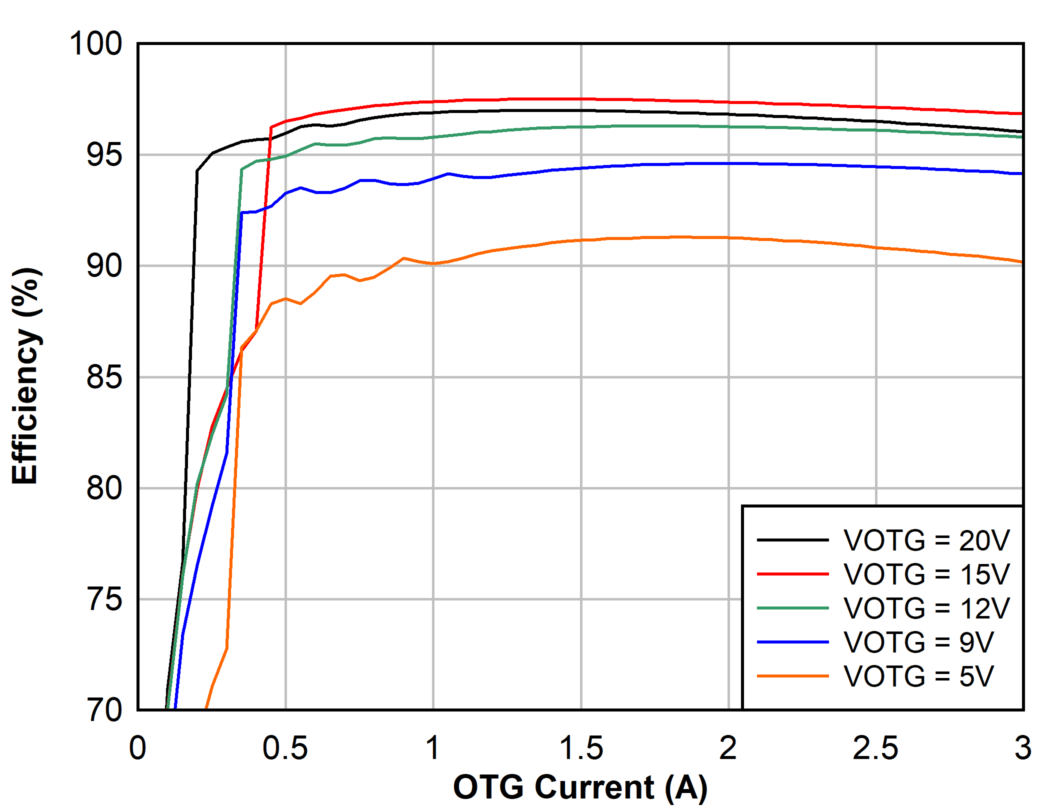

Figure 8-15 4s

Battery OTG Efficiency, 750 kHz

| VBAT

= 8V, Fsw = 1.5MHz with L1 = 1µH |

Figure 8-17 Input

Current Regulation (IINDPM) Accuracy

| VBAT

= 8.4V, Fsw = 1.5MHz with L1 = 1µH |

|

Figure 8-19 OTG

Voltage Regulation (VOTG) Accuracy

| VBAT

= 4V, Fsw = 1.5 MHz with L1 = 1.0 µH, PFM

disabled |

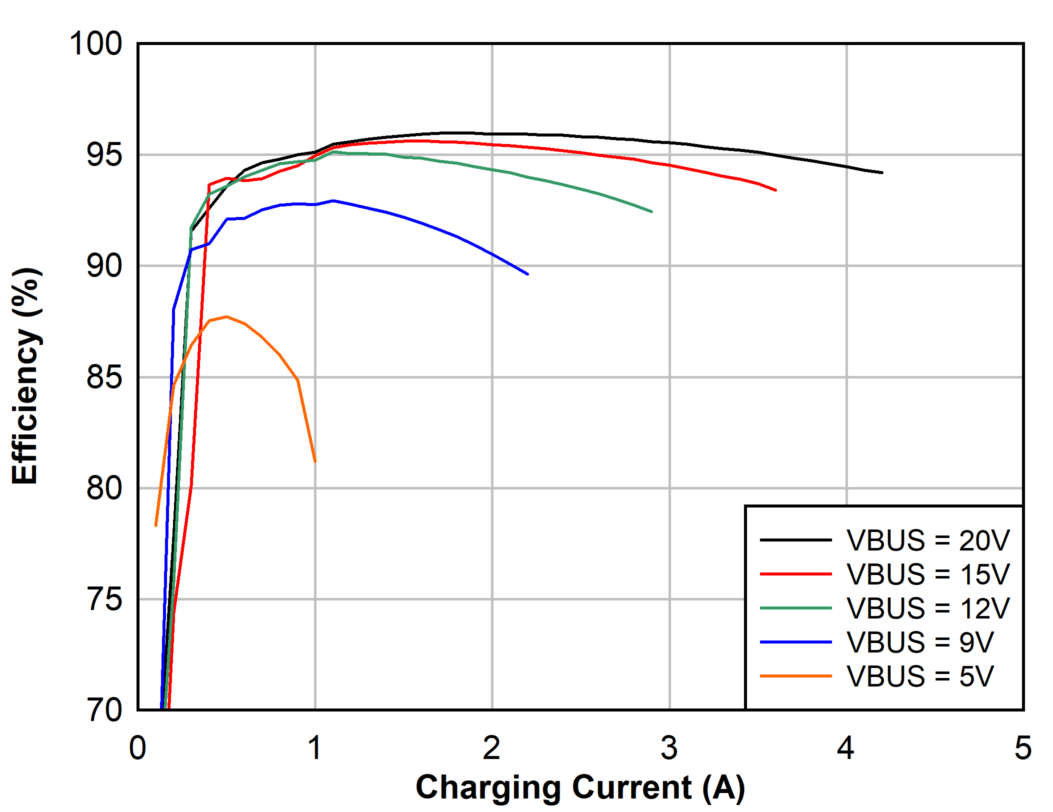

Figure 8-2 1s

Battery Charge Efficiency, 1.5 MHz

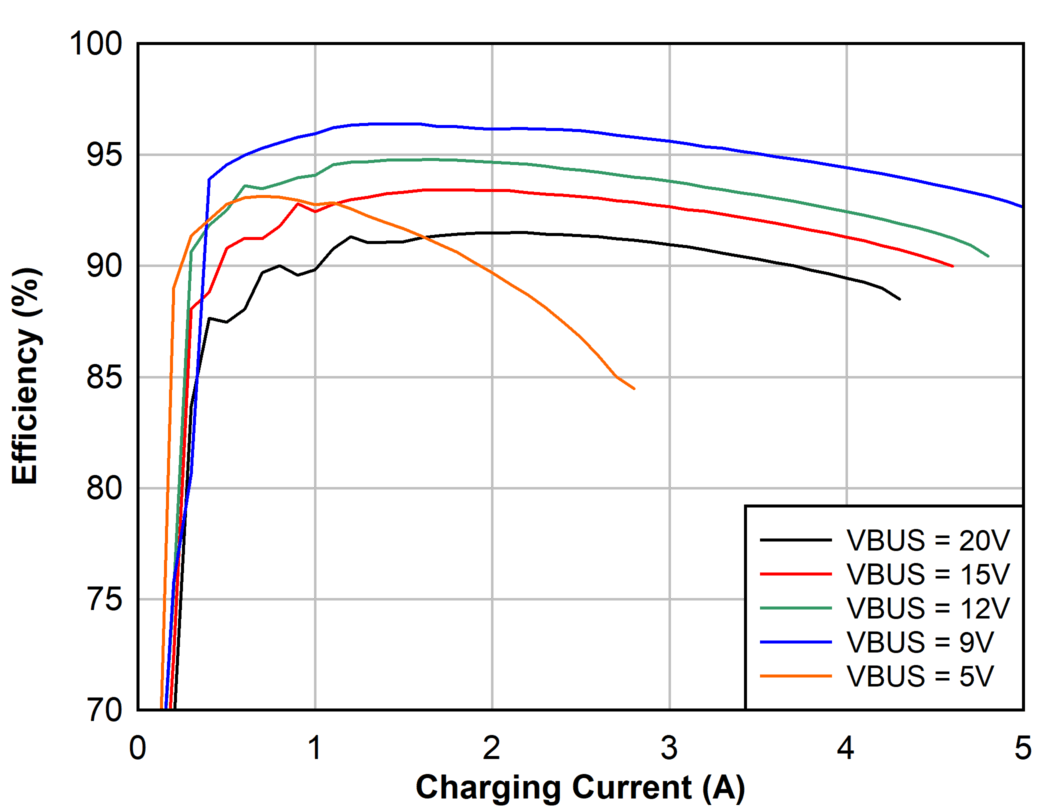

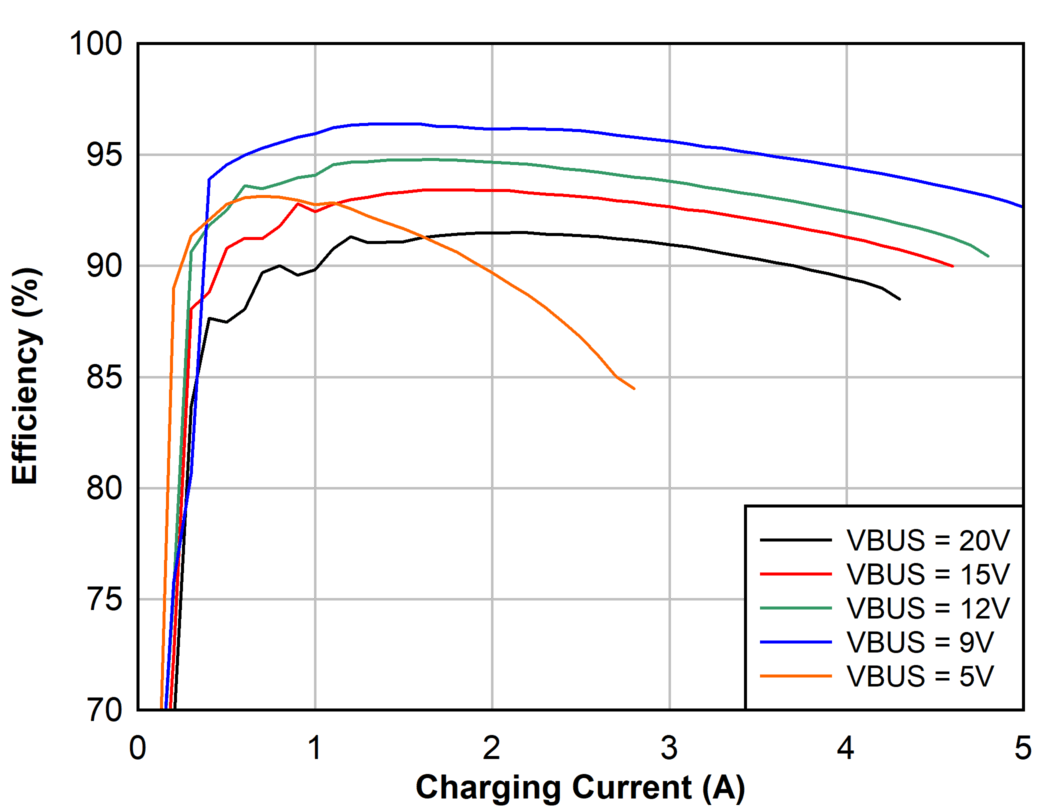

| VBAT

= 8V, Fsw = 1.5 MHz with L1 = 1µH, PFM disabled |

Figure 8-4 2s

Battery Charge Efficiency, 1.5 MHz

| VBAT

= 12V, Fsw = 1.5 MHz with L1 = 1µH, PFM disabled |

Figure 8-6 3s

Battery Charge Efficiency, 1.5 MHz

| VBAT

= 16V, Fsw = 1.5 MHz with L1 = 1µH, PFM disabled |

Figure 8-8 4s

Battery Charge Efficiency, 1.5 MHz

| VBAT

= 4.2V, Fsw = 1.5 MHz with L1 = 1µH, PFM

disabled |

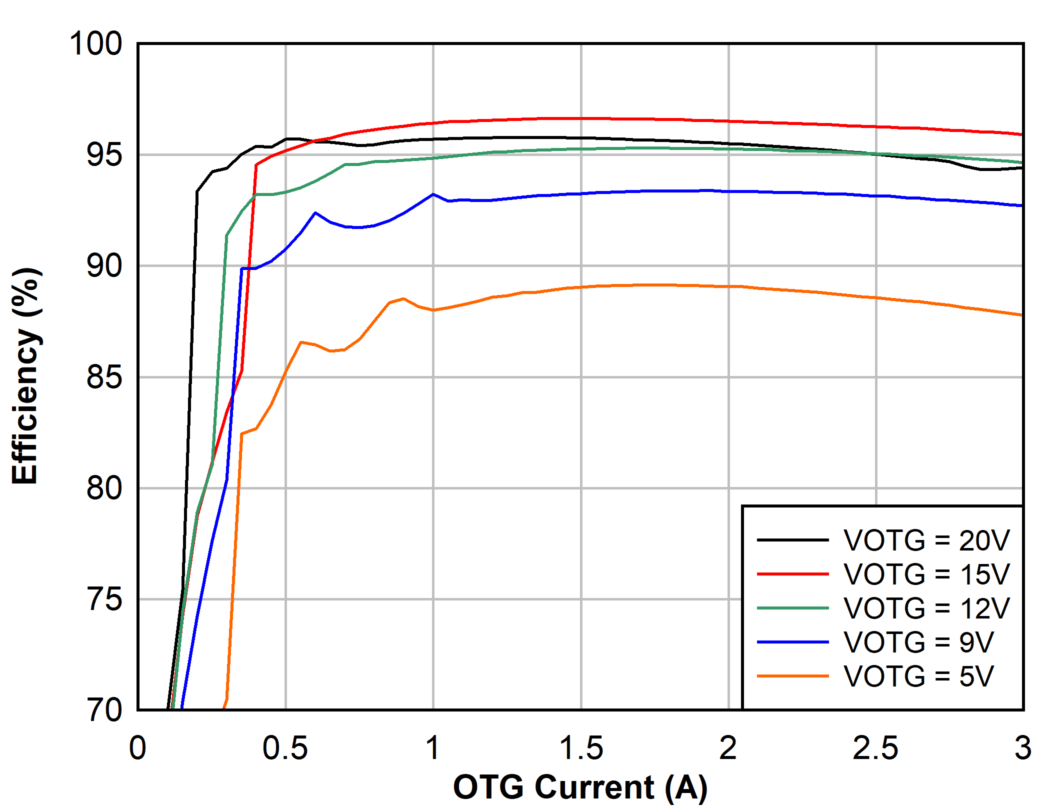

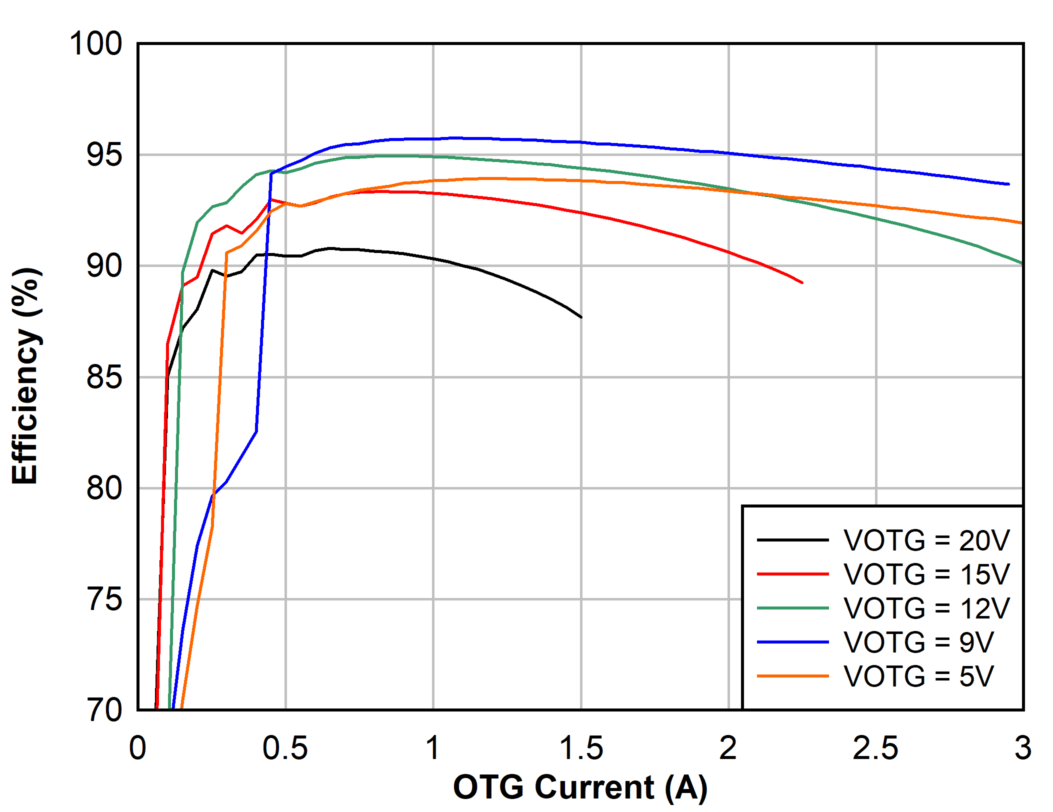

Figure 8-10 1s

Battery OTG Efficiency, 1.5 MHz

| VBAT

= 8.4V, Fsw = 1.5MHz with L1 = 1µH, PFM disabled |

Figure 8-12 2s

Battery OTG Efficiency, 1.5 MHz

| VBAT

= 12.6V, Fsw = 1.5 MHz with L1 = 1µH, PFM

disabled |

Figure 8-14 3s

Battery OTG Efficiency, 1.5 MHz

| VBAT

= 16.8V, Fsw = 1.5 MHz with L1 = 1µH, PFM

disabled |

Figure 8-16 4s

Battery OTG Efficiency, 1.5 MHz

| VBAT

= 8V, Fsw = 1.5MHz with L1 = 1µH |

Figure 8-18 Input

Voltage Regulation (VINDPM) Accuracy

| VBUS

= 9V, Fsw = 1.5MHz with L1 = 1µH, ISYS = 0A, Charge

Disabled |

Figure 8-20 Offset Voltage of SYS Regulation above VBAT