SLVUCO6 june 2023 TPSI2072-Q1

4.1 Waveforms

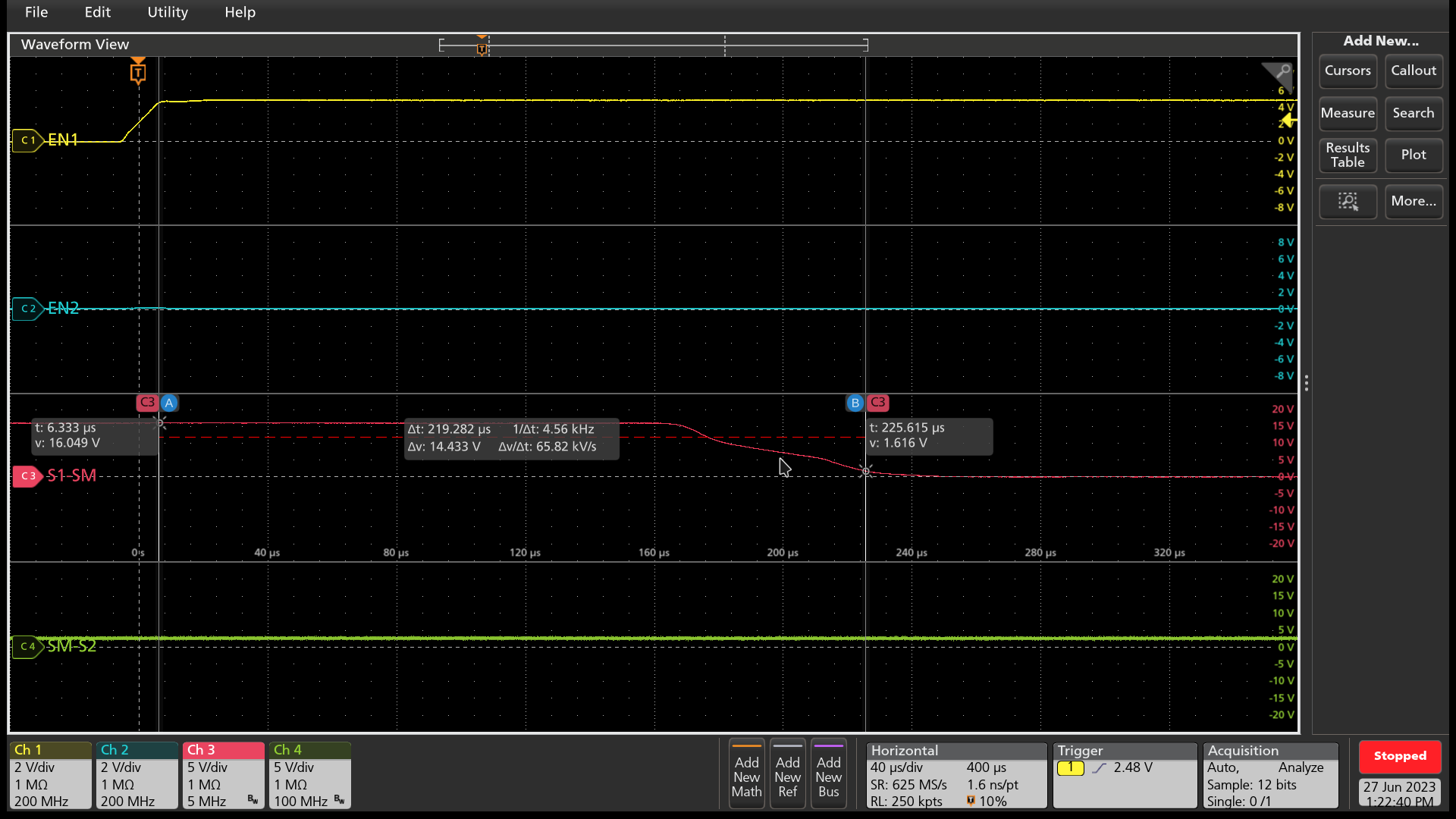

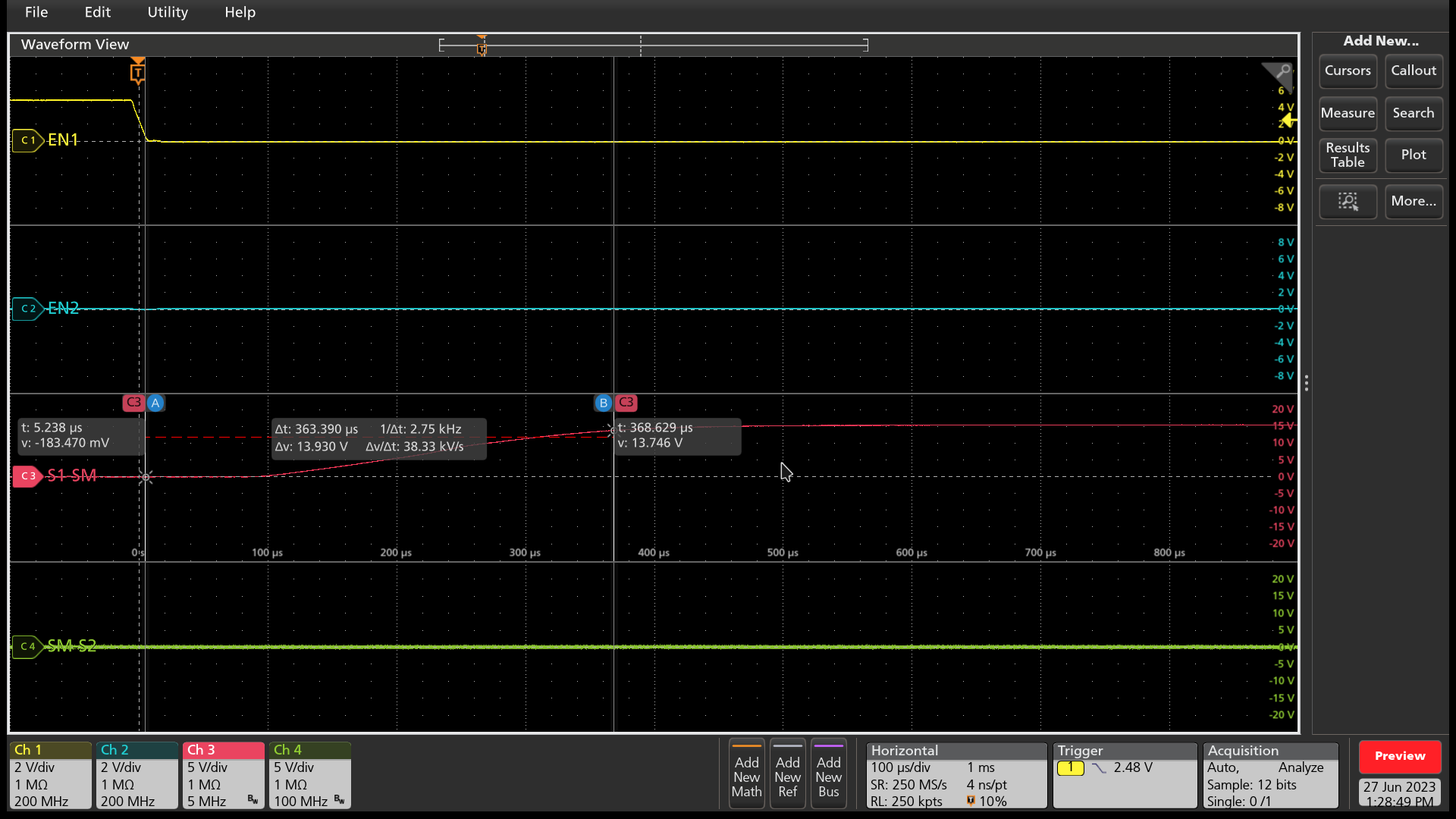

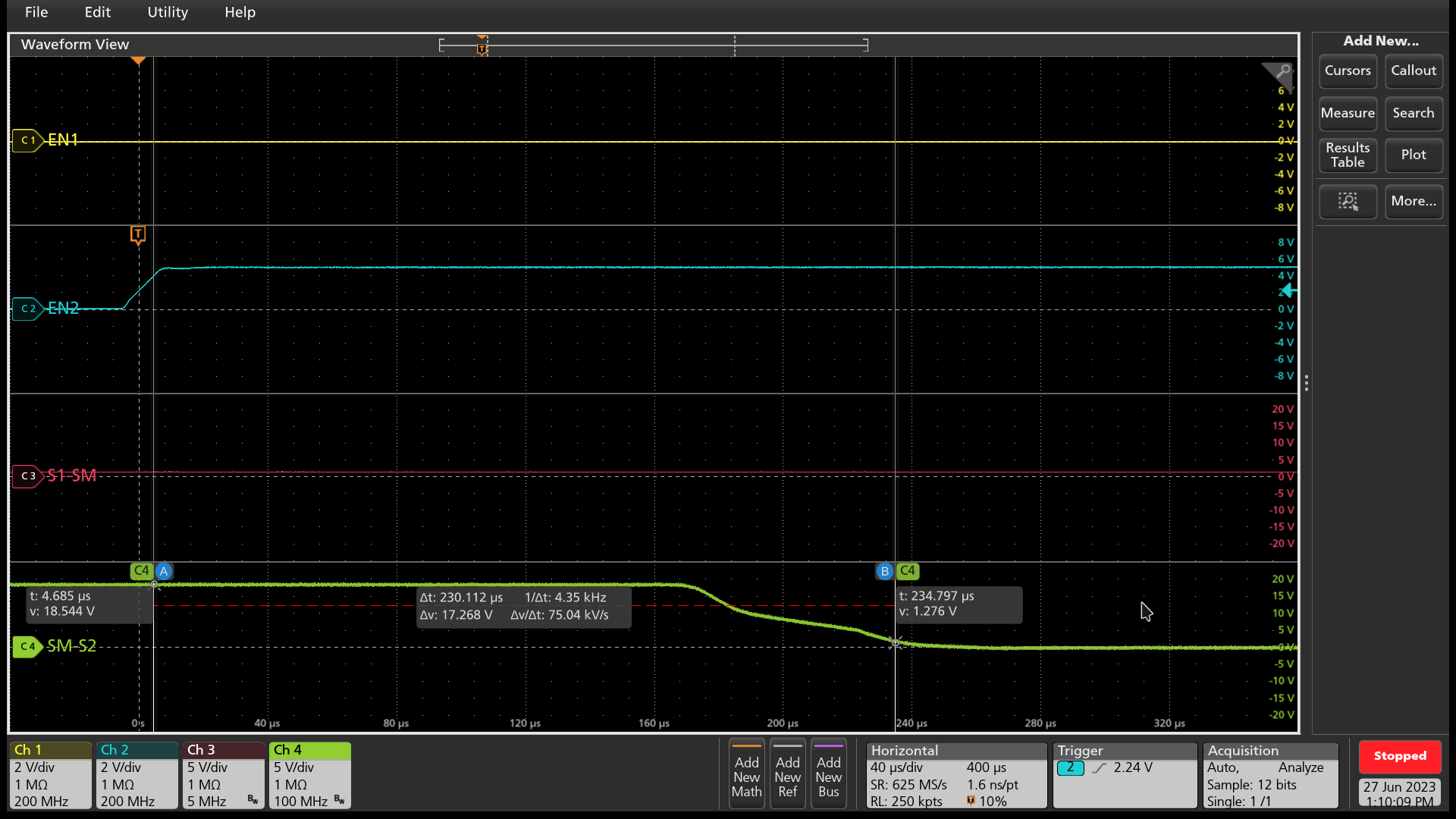

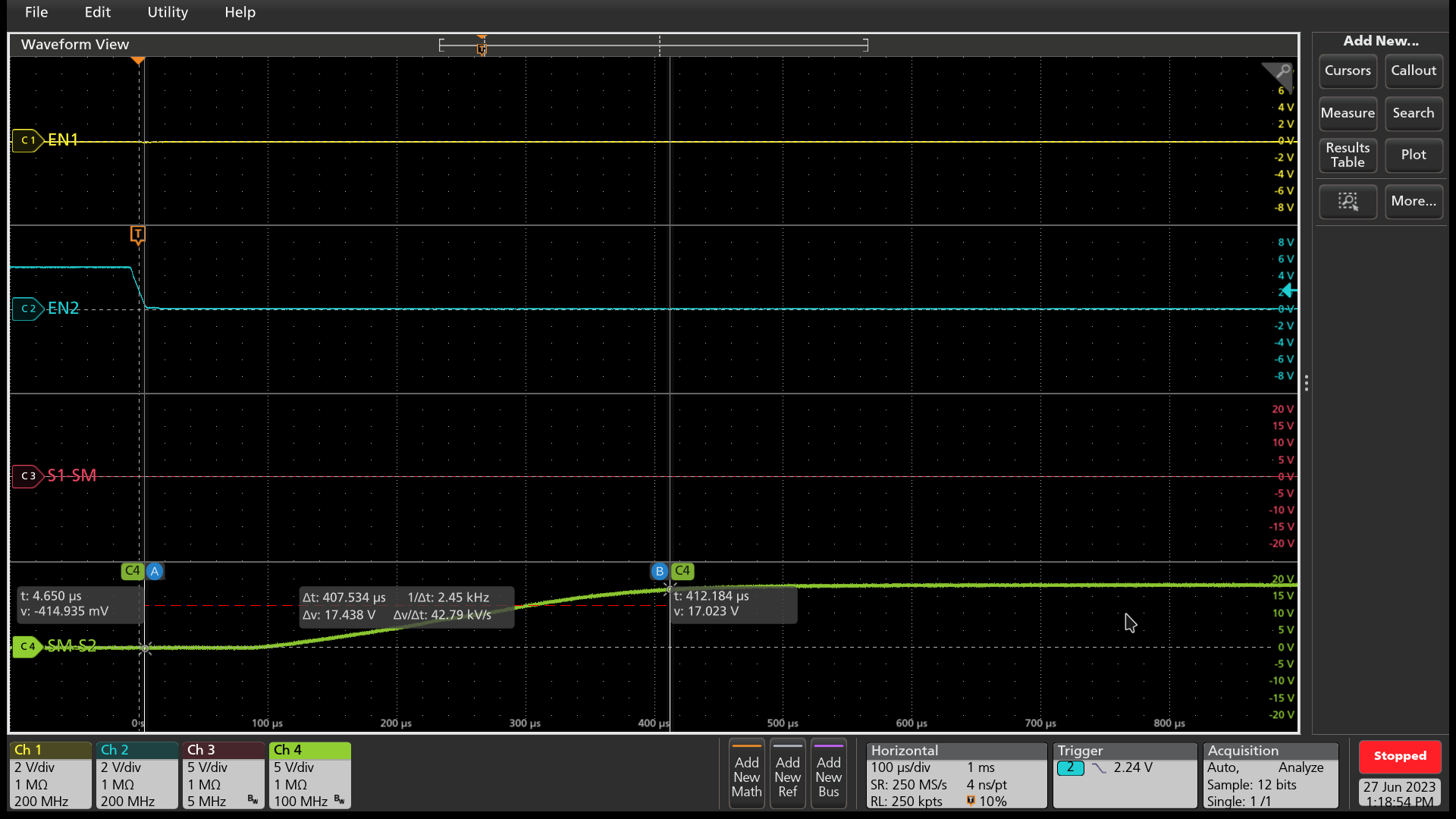

If connected as described above, the following channels must be displayed in the waveforms below:

CH 1 = EN1

CH 2 = EN2

CH 3 = S1-SM

CH 4 = SM-S2

Figure 4-2 RN1 Rise Time

Figure 4-2 RN1 Rise Time Figure 4-3 EN1 Fall Time

Figure 4-3 EN1 Fall Time Figure 4-4 EN2 Rise Time

Figure 4-4 EN2 Rise Time Figure 4-5 EN2 Fall Time

Figure 4-5 EN2 Fall Time