SNVU543A November 2016 – December 2016

-

LM5170-Q1 EVM User Guide

- Trademarks

- 1 Features and Electrical Performance

- 2 Setup

- 3 Test Procedure

- 4

Test Data

- 4.1 Efficiency

- 4.2 Current Regulation and Monitoring

- 4.3 Typical Master Enable Power Up and Shutdown

- 4.4 Channel Enable and Disable

- 4.5 Dual-Channel Interleaving Operation

- 4.6 ISETA Tracking

- 4.7 Diode Emulation Preventing Negative Currents

- 4.8 Dynamic DIR Change

- 4.9 Step Load Response

- 4.10 OVP

- 4.11 Output Short Circuit

- 5 Design Files

- Revision History

2.1 EVM Configurations

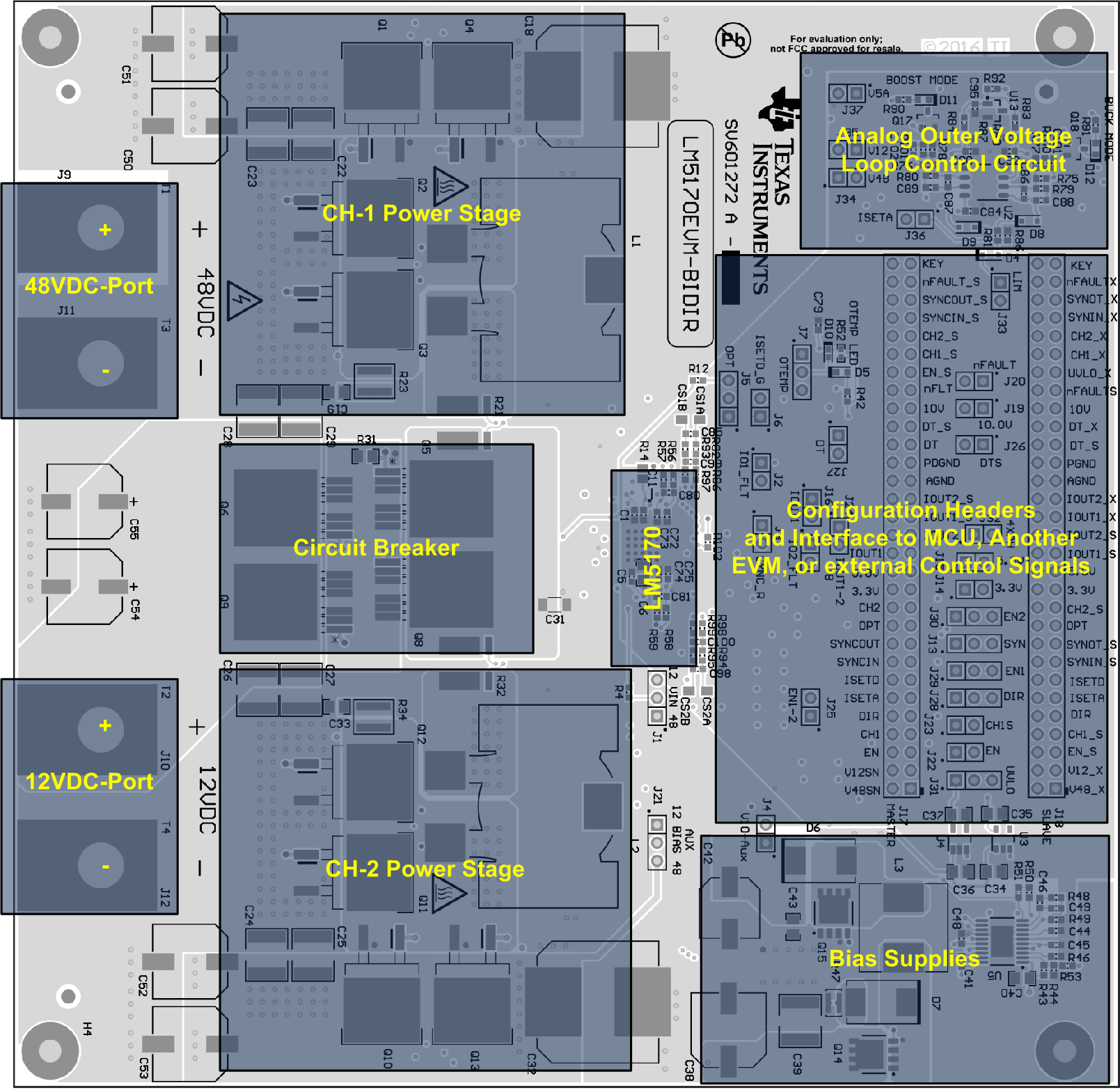

Figure 2 shows the EVM board top view and circuit layout partitions. The EVM has the following ports:

- 48VDC-Port: Connected to 48-V battery rail

- 12VDC-Port: Connected to 12-V battery rail

- J17 (60-Pin Header): Interfacing the external control commands or MCU

- J18 (60-Pin Header): Interfacing the slave EVM’s J17 in a 4-phase system consisting of two EVMs

- Master Enable Using J17-pin 5: Providing a voltage of 2.5 V to 6 V to operate the EVM.

- Channel Current Setting: Analog programming at J17-pin 11, and digital programming at J17-pin 13.

Table 2 through Table 5 list the functions of the EVM jumpers and headers. They offer flexible configurability and programmability of the EVM for various use cases including but not limited to the following:

- A unidirectional or bidirectional current source

- A unidirectional or bidirectional voltage source

- Dynamic phase adding and shedding in a 4-phase system consisting of two EVMs

- Dynamic MOSFETs dead time adjustment

- Individual channel current monitoring or total current monitoring

- Programmable undervoltage lockout (unpopulated)

- Synchronization to external clock

- External shutdown command through nFAULT pin (J17-pin45)

Figure 1. Simplified EVM Schematic

Figure 1. Simplified EVM Schematic  Figure 2. EVM Board Top View and Layout Partitions

Figure 2. EVM Board Top View and Layout Partitions Table 2. Three-Pin Header Settings

| HEADER | SIGNAL | PINS | FUNCTION DESCRIPTION | DEFAULT |

|---|---|---|---|---|

| J1 | — | --(1) | No UVLO Programming | Y |

| (1,2)(2) | 48VDC-Port UVLO Control | |||

| (2,3)(3) | 12VDC-Port UVLO Control | |||

| J5 | OPT | -- | External interleaving control through J17 | |

| (1,2) | CH-2 240 degree delay from CH-1 | |||

| (2,3) | CH-2 180 degree delay from CH-1 | Y | ||

| J7 | OTEMP | -- | Onboard Overtemperature protection disabled | Y |

| (1,2) | Overtemperature protection in hiccup mode | |||

| (2,3) | Overtemperature protection in latched shutdown | |||

| J13 | SYNC | -- | Slave EVM not sync to master EVM | Y |

| (1,2) | Slave EVM sync to master via J18 | |||

| (2,3) | Slave EVM sync to external Clock | |||

| J21 | BIAS | -- | Use external 10V supply | |

| (1,2) | Onboard +10V produced from the 12VDC-Port | |||

| (2,3) | Onboard +10V produced from the 48VDC-Port | Y | ||

| J28 | DIR | -- | External DIR control through J17 | |

| (1,2) | Onboard DIR command for buck operation | Y | ||

| (2,3) | Onboard DIR command for boost operation | |||

| J29 | EN1 | -- | External CH-1 enable control through J17 | |

| (1,2) | Onboard CH-1 enable | Y | ||

| (2,3) | Onboard CH-1 disable | |||

| J30 | EN2 | -- | External CH-1 enable control through J17, overridden by J25. | Y |

| (1,2) | Onboard CH-2 enable | |||

| (2,3) | Onboard CH-2 disable | |||

| J31 | UVLO | -- | External EVM enable through J17 | Y |

| (1,2) | Onboard EVM enable, if external 3.3V is supplied to J17-pin23. | |||

| (2,3) | EVM disable |

(1) – = All jumper pins open.

(2) (1,2) = Pins 1 and 2 closed.

(3) (2,3) = Pins 2 and 3 closed.

Table 3. Two-Pin Header Settings

| HEADER | SIGNAL | PINS | FUNCTION DESCRIPTION | DEFAULT |

|---|---|---|---|---|

| J2 | IOUT1 | O(1) | External IOUT1 termination | |

| C(2) | Onboard IOUT1 termination | Y | ||

| J3 | SYNCOUT | O | Enable the fault detection | Y |

| C | Disable the fault detection disabled | |||

| J4 | VCC | O | An external 10-V supply as VCC supply | Y |

| C | The onboard 10-V regulator as VCC supply | |||

| J6 | ISETD | O | ISETD input disabled | |

| C | ISETD input is enabled | Y | ||

| J8 | IOUT2 | O | External IOUT2 signal termination | |

| C | Onboard IOUT2 signal termination | Y | ||

| J14 | 3.3 V | O | Onboard 3.3-V bias voltage disconnected from the slave EVM | Y |

| C | Onboard 3.3-V bias voltage feeding the slave EVM | |||

| J15 | 5 V | O | Onboard 5-V bias voltage disconnected from the slave EVM | Y |

| C | Onboard 5-V bias voltage feeding the slave EVM | |||

| J16 | IOUT_All | O | Independent channel monitor | Y |

| C | Combined total monitor in master/slave configuration. Requiring J25 to be closed too. | |||

| J19 | 10 V | O | 10-V bias voltage disconnected from the slave EVM | Y |

| C | 10-V bias voltage feeding the slave EVM | |||

| J20 | nFAULT | O | Independent master/slave nFAULT signal | Y |

| C | Combined master/slave nFAULT signal | |||

| J22 | EN | O | Independent enable control of the master and slave EVMs | Y |

| C | Combined enable control of the master and slave EVMs | |||

| J23 | CH1S | O | Independent slave EVM CH-1 enable | Y |

| C | Combined master/slave channel enable | |||

| J24 | IOUT1-2 | O | Independent channel current monitors | Y |

| C | Combined dual-channel current monitor | |||

| J25 | EN1-2 | O | Independent channel enable | Y |

| C | Combined dual-channel enable | |||

| J26 | DTS | O | Independent DT adjustment input for the slave EVM | Y |

| C | Combined DT adjustment for both the master and slave EVMs | |||

| J27 | DT | O | External programmable DT adjustment input | Y |

| C | Onboard DT setting | |||

| J32 | OPT/ EN2_slave | O | 3- and 4-phase transition disabled | Y |

| C | 3- and 4-phases transition enabled | |||

| J33 | ILIM | O | External current limit control input | Y |

| — | Do not close | |||

| J34 | 48VDC Sense | O | Boost analog outer voltage loop control disabled | Y |

| C | Boost analog outer voltage loop control enabled | |||

| J35 | 12VDC Sense | O | Buck analog outer voltage loop control disabled | Y |

| C | Buck analog outer voltage loop control enabled | |||

| J36 | ISETA | O | Analog outer voltage loop control disabled | Y |

| C | Analog outer voltage loop control enabled | |||

| J37 | 5 V | O | Analog outer voltage loop control disabled | Y |

| C | Analog outer voltage loop control enabled |

(1) Jumper pins open.

(2) Jumper pins closed.

Table 4. J17 60-Pin Header Description(1)

| PIN | SIGNAL | I/O | DESCRIPTION |

|---|---|---|---|

| 1 | V48SN | O(2) | 48V-port voltage sense during operation |

| 3 | V12SN | O | 12V-port voltage sense during operation |

| 5 | EN (MASTER ENABLE) | I(3) | Master EVM enable (connect to the UVLO pin of the IC) |

| 7 | CH1 | I | CH-1 control (connect to the EN1 pin of the IC) |

| 9 | DIR | I | Direction command |

| 11 | ISETA | I | Channel current setting (analog voltage) |

| 13 | ISETD | I | Channel current setting (PWM signal) |

| 15 | SYNCIN | I | Input of the external clock to be synchronized to |

| 17 | SYNCOUT | O | Clock output signal |

| 19 | OPT | I | Interleave angle setting |

| 21 | CH2 | I | CH-2 control (connect to the EN2 pin of the IC) |

| 23 | +3.3 V | O | Output of onboard +3.3-V voltage |

| 25 | +5 V | O | Output of onboard +5-V voltage |

| 27 | IOUT1 | O | CH-1 monitor |

| 29 | IOUT2 | O | CH-2 current monitor |

| 31 | IOUT1_S | O | Slave EVM CH-1 monitor in 3 or 4 phases |

| 33 | IOUT2_S | O | Slave EVM CH-2 current monitor in 3 or 4 phases |

| 35 | AGND | I/O | Reference GND for control signals |

| 37 | PGND | O | Power ground of the DC-DC converter |

| 39 | DT | I | Dead time adjustment pin |

| 41 | DT_S | I | Slave dead time adjustment pin |

| 43 | +10 V | I/O | Input of +10-V bias supply, or output of onboard +10-V bias supply |

| 45 | nFAULT | I/O | Fault report flag, or external shutdown command pin |

| 47 | ENABLE_S | I | Slave EVM enable (connect to the UVLO pin of the slave IC) |

| 49 | CH1_S | I | Slave EVM CH-1 control (connect to the EN1 pin of the slave IC) |

| 51 | CH2_S | I | Slave EVM CH-2 control (connect to the EN2 pin of the slave IC) |

| 53 | SYNCIN_S | I | Input of the external clock for the slave to be synchronized to |

| 55 | SYNCOUT_S | O | Slave EVM clock output signal |

| 57 | nFAULT_S | I/O | Slave EVM fault report flag, or external shut down command input pin |

| 59 | KEY | — | No Connect |

| All even number pins | AGND | I/O | All signals’ return |

(1) J17 is the interface connector to MCU, or external digital controller, or to the master EVM’s J18 if the host EVM serves as a slave in the multiphase configuration.

(2) I = input pin

(3) O = output pin

Table 5. J18 60-Pin Header Description(1)

| PIN | SIGNAL | I/O | DESCRIPTION |

|---|---|---|---|

| 1 | V48_X | — | No Connect |

| 3 | V12_X | — | No Connect |

| 5 | ENABLE_S | I(2) | Slave EVM enable (connect to the UVLO pin of the slave IC) |

| 7 | CH1_S | I | Slave EVM CH-1 control (connect to the EN1 pin of the IC) |

| 9 | DIR | I | Direction command |

| 11 | ISETA | I | Channel current setting (analog voltage) |

| 13 | ISETD | I | Channel current setting (PWM signal) |

| 15 | SYNCIN_S | I | The external clock input for the slave |

| 17 | SYNCOUT_S | O(3) | Slave EVM clock output signal |

| 19 | OPT | I | Interleave angle setting |

| 21 | CH2_S | I | Slave EVM CH-2 control (connect to the EN1 pin of the IC) |

| 23 | +3.3 V | I | Output of onboard +3.3-V voltage |

| 25 | +5 V | I | Output of onboard +5-V voltage |

| 27 | IOUT1_S | O | Slave EVM CH-1 monitor in 3 or 4 phases |

| 29 | IOUT2_S | O | Slave EVM CH-2 current monitor in 3 or 4 phases |

| 31 | IOUT1_X | — | Not used |

| 33 | IOUT2_X | — | Not used |

| 35 | AGND | I/O | Reference GND for control signals |

| 37 | PGND | O | Power ground of the DC-DC converter |

| 39 | DT_S | I | Slave EVM dead time adjustment pin |

| 41 | DT_X | — | No Connect |

| 43 | +10 V | I | Input of +10-V bias supply, or output of onboard +10-V bias supply |

| 45 | nFAULT_X | I/O | Slave EVM fault report flag, or external shutdown command pin |

| 47 | UVLO_X | — | No Connect |

| 49 | CH1_X | — | No Connect |

| 51 | CH2_X | — | No Connect |

| 53 | SYNCIN_X | — | No Connect |

| 55 | SYNCOUT_X | — | No Connect |

| 57 | nFAULT_X | — | No Connect |

| 59 | KEY | — | No Connect |

| All even number pins | AGND | I/O | All signals’ return |

(1) J18 is the interface connector to the slave EVM in the multiphase configuration if the host EVM serves as the master. All control commands and control signals are sent through J18 to the slave EVM’s J17.

(2) I = input pin

(3) O = output pin