SPRADC5 January 2024

2.2 Manual Audit of the Pinmux

- Check the schematics for the exact Ball number. For example, J721E/TDA4VM(SoC) à gpio0_0(Signal_name). Do a search in the corresponding Data Manual for TDA4VM/J721E:

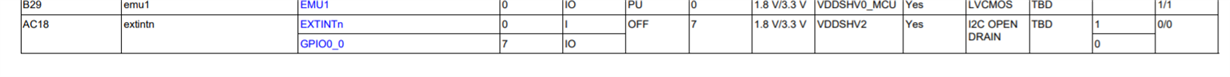

- The first instance of search lands in the table that provides the Ball number and name, which is what you need to check in board schematics to see on which Ball the gpio0_0 is brought out on the board. For example: AC18 maps to for GPIO0_0. Page: 18 of the document link shared in #1 above.

- Search for AC18 that maps on to a padconfig register as shown below. In the PADCONFIG0 register in the device-specific data manual search for AC18 and that is the mode that needs to be programmed. For example, gpio0_0 is mode7 and hence the pinmux files should have mode7 to bring out gpio0_0 signal out of ball AC18.Page: 138 of the document link pointed in #1 above.

You can tally the devicetree.dtsi generated by the pinmux tool and manually audited register, and the bit fields and cross verify. For example, J721E_IOPAD(0x0, PIN_INPUT, 7) 0x0 corresponds to register offset 0x0 for PADCONFIG0 register and 7 corresponds to mux mode7.