Merkmale von LMK04826BEVM

- JEDEC JESD204B-Unterstützung

- Extrem niedrige RMS-Jitter-Leistung

- Doppelschleifen-Architektur

- 3 redundante Eingangstakte mit LOS

- Digitale Präzisionsverzögerung, fest oder dynamisch einstellbar

- Das Evaluierungskit enthält ein USB2ANY-Modul für den USB-Anschluss an die Evaluierungsplatine.

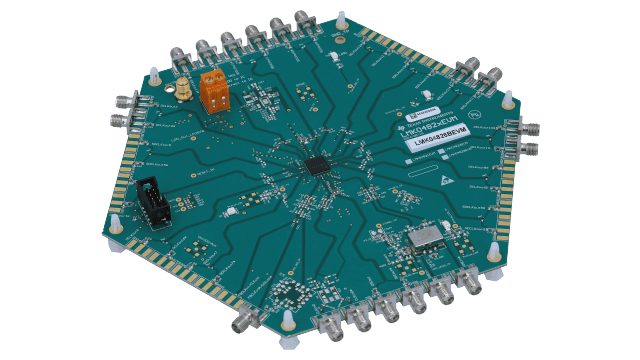

Beschreibung von LMK04826BEVM

Das LMK04826BEVM und das LMK04828BEVM sind für die LMK04820-Produktfamilie ausgelegt, die branchenweit leistungsstärksten Bausteine zur Taktaufbereitung mit JEDEC JESD204B-Unterstützung. Die Doppelschleifen-PLLatinum™ -Architektur ermöglicht Jitter unter 100 fs (12 kHz bis 20 MHz) mit einem rauscharmen VCXO-Modul. Die Doppelschleifen-Architektur besteht aus zwei phasenverriegelten Hochleistungsschleifen (PLL), einer rauscharmen Quarzoszillatorschaltung und einem spannungsgesteuerten Hochleistungs-Oszillator (VCO).

Die erste PLL (PLL1) bietet eine rauscharme Jitter-Reiniger-Funktion, während die zweite PLL (PLL2) die Takt und SYSREF-Erzeugung übernimmt. PLL1 kann entweder für den Betrieb mit einem externen VCXO-Modul oder mit dem integrierten Quarzoszillator mit einer externen abstimmbaren Quarz- und Varaktordiode konfiguriert werden. Bei Verwendung mit einer sehr engen Schleifenbandbreite verwendet PLL1 das überlegene Phasenrauschen (Offsets unter 50 kHz) des VCXO-Moduls oder der abstimmbaren Quarzdiode, um den Eingangstakt zu bereinigen. Der Ausgang von PLL1 wird als saubere Eingangsreferenz auf PLL2 verwendet, wo er den integrierten VCO sperrt.

Die Schleifenbandbreite von PLL2 kann optimiert werden, um das weit entfernte Phasenrauschen (Offsets über 50 kHz) zu entfernen, bei dem der integrierte VCO das im PLL1 verwendete VCXO-Modul oder den abstimmbaren Quarz übertrifft.