Merkmale von TSW40RF80EVM

- HF-Abtasttransceiver unter Verwendung der JESD204B-Schnittstelle

- DAC38RF80 Dual-HF-DAC mit unsymmetrischem Ausgang

- ADC32RF45 Dual-RF-ADC mit Bypass-Option

- LDO-lose Power-Management-Lösung

- Auf der Platine integrierte Taktlösung; vier verschiedene ADC-Taktungsoptionen, einschließlich TX-PLL-Taktausgang

- Schnittstellen zum TSW14J56- oder FPGA-Entwicklungskit mit FMC-Steckverbinder

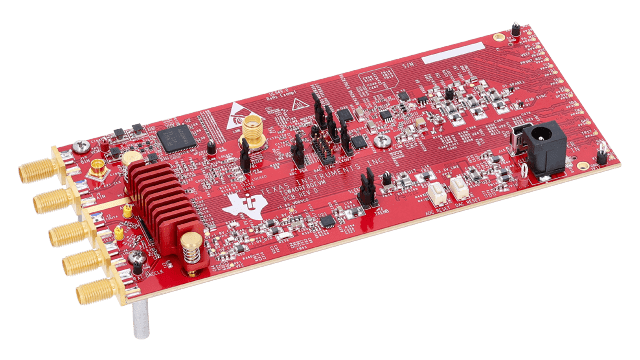

Beschreibung von TSW40RF80EVM

Das Evaluierungsmodul (EVM) TSW40RF80 ist ein RF-Sampling-Transceiver mit zwei Sende- und zwei Empfangsketten (2T2R) – Referenzdesign. Das Modul enthält den zweikanaligen Digital-Analog-Wandler (DAC) DAC38RF80 mit HF-Abtastung und den zweikanaligen Analog-Digital-Wandler (ADC) ADC32RF45 mit HF-Abtastung.

Die DAC38RF80-Abtastrate arbeitet mit bis zu 9 GSPS und enthält einen integrierten PLL/VCO zur Hochfrequenz-Takterzeugung. Der Ausgang ist einseitig geerdet, um eine einfache Schnittstelle zu 50-Ω-Schaltungen zu ermöglichen. Die ADC32RF45-Abtastrate arbeitet mit bis zu 3 GSPS. Es besteht die Möglichkeit, in jedem Kanal einen dualen digitalen Abwärtswandler zu verwenden oder diesen zu umgehen, um auf die volle Nyquist-Bandbreite zuzugreifen.

Das TSW40RF80EVM enthält den LMK04828-Takt-Generator zum Bereitstellen eines Referenzsignals an die DAC PLL und zum Erzeugen der erforderlichen SYSREF-Signale für das JESD204B-Protokoll. Ebenfalls enthalten ist der HF-Synthesizer LMX2582 zur Bereitstellung einer Taktlösung mit extrem geringem Phasenrauschen für den ADC.

Das TSW40RF80EVM setzt eine effiziente Low-Dropout LDO-lose Power-Management-Lösung mit nur DC-DC-Wandlern für die erforderlichen Stromschienen um. Das Design passt in eine FMC-konforme Standardbreite und ist mit der Muster-/Erfassungskartenlösung von TI (TSW14J56) sowie mit vielen FPGA-Entwicklungskits verwendbar.