ADC31JB68EVM の特徴

- トランス結合型の信号入力回路により、シングルエンド型信号源に対応

- 高速シリアル・インターフェイス用の FPGA リファレンス・クロックを生成する LMK4828 システム・クロック・ジェネレータ

- 非常にノイズの小さいクロックで ADC の性能をテストすることを目的とした、デフォルトのトランス結合型クロック入力回路

- 標準的な FMC コネクタを介した高速シリアル・データ出力

- USB コネクタと FTDI USB/SPI バス・トランスレータを介したデバイス・レジスタのプログラミング

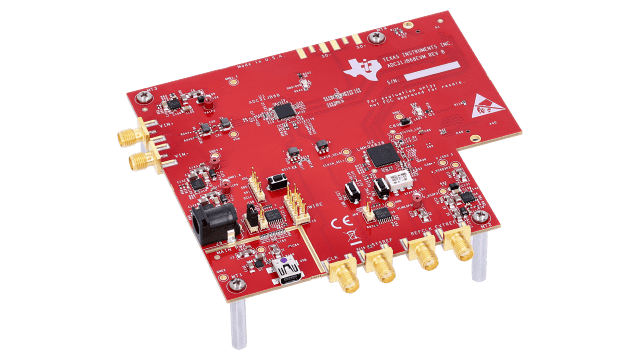

ADC31JB68EVM に関する概要

ADC31JB68EVM は、TI の ADC31JB68 A/D コンバータ (ADC) の評価に使用できる評価ボードです。ADC31JB68 は、最大 500MSPS (毎秒メガ・サンプル) のサンプリング・レート動作に対応したシングルチャネルの 16 ビット ADC で、標準的な JESD204B 高速シリアル・インターフェイス出力を採用しています。

ADC31JB68EVM は、TI の JESD204B データ・キャプチャ・カードである TSW14J56EVM、および高速データ・コンバータ評価用の高速データ・コンバータ Pro (HSDCPro) ソフトウェア・ツールとシームレスに連携する設計を採用しています。また、ADC31JB68EVM は、有力 FPGA ベンダの多数の FMC コネクタ搭載開発キットとの組み合わせが可能です。