SBAS619A March 2014 – June 2017 AFE5401-Q1

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 ESD Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Thermal Information

- 6.5 Electrical Characteristics

- 6.6 Digital Characteristics

- 6.7 Timing Requirements: Output Interface

- 6.8 Timing Requirements: RESET

- 6.9 Timing Requirements: Serial Interface Operation

- 6.10 Typical Characteristics

- 7 Parameter Measurement Information

- 8 Timing Requirements: Across Output Serialization Modes

-

9 Detailed Description

- 9.1 Overview

- 9.2 Functional Block Diagram

- 9.3 Feature Description

- 9.4 Device Functional Modes

- 9.5 Programming

- 9.6 Register Maps

- 10Application and Implementation

- 11Power Supply Recommendations

- 12Layout

- 13Device and Documentation Support

- 14Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- RGC|64

Thermal pad, mechanical data (Package|Pins)

- RGC|64

Orderable Information

12 Layout

12.1 Layout Guidelines

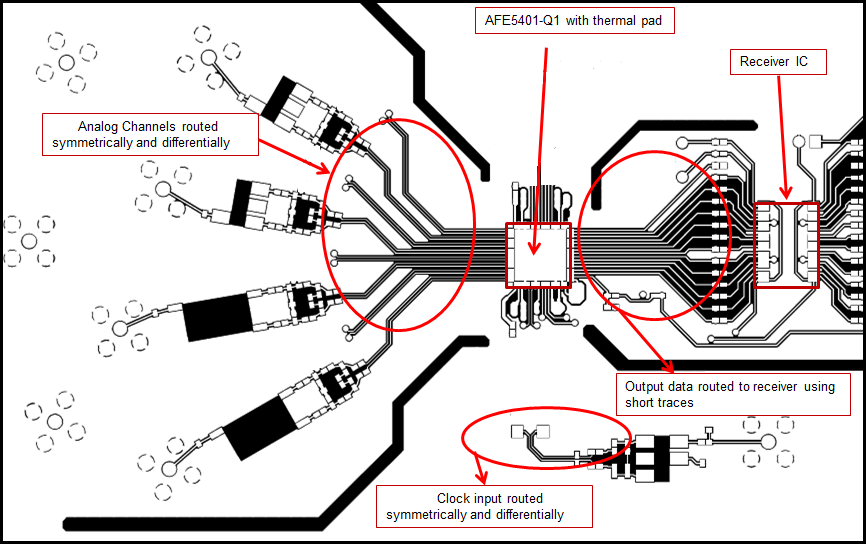

All analog inputs must be differentially and symmetrically routed to the differential input pins of the device for best performance. CMOS outputs traces should be kept as short as possible to reduce the trace capacitance that loads the CMOS output buffers. Multiple ground vias can be added around the CMOS output data traces, especially when the traces are routed on more than one layer. TI recommends matching the lengths of the output data traces (D[11:0]) to reduce the skew across data bits.

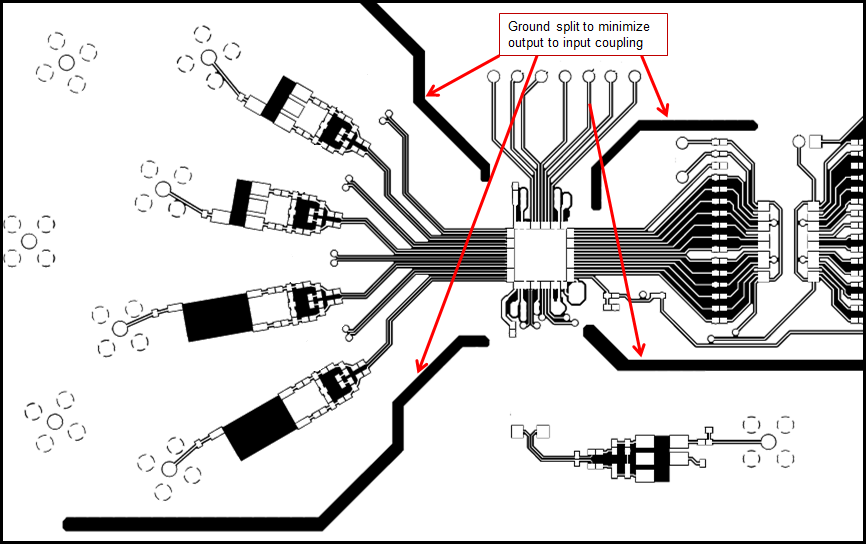

Switching noise (caused by CMOS output data transitions) can couple into the analog inputs and degrade SNR. This condition is particularly of concern because of the high gain present in the analog input channel. Digital outputs coupling back to analog inputs can be minimized by proper separation of analog and digital areas in the board layout. Figure 131 illustrates an example layout where the analog and digital portions are routed separately. This example also uses splits in the ground plane to minimize digital currents from looping into analog areas. At the same time, note that the analog and digital grounds are shorted below the device. A single ground plane is sufficient to give good performance, provided the analog, digital, and clock sections of the board are cleanly partitioned.

The device package consists of an exposed pad. In addition to providing a path for heat dissipation, the pad is also internally connected to the analog ground. Therefore, the exposed pad must be soldered to the ground plane for best thermal and electrical performance. For detailed information, see application notes QFN Layout Guidelines and QFN/SON PCB Attachment. Figure 131 and Figure 132 illustrate the layout diagrams taken from the AFE5401-Q1 EVM User's Guide.

12.2 Layout Example

Figure 131. Layout Diagram: Signal Routing

Figure 131. Layout Diagram: Signal Routing

Figure 132. Layout Diagram: Ground Split

Figure 132. Layout Diagram: Ground Split