DLPS029F April 2013 – May 2019 DLPC350

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 ESD Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Thermal Information

- 6.5 I/O Electrical Characteristics

- 6.6 I2C0 and I2C1 Interface Timing Requirements

- 6.7 Port 1 Input Pixel Interface Timing Requirements

- 6.8 Port 2 Input Pixel Interface (FPD-Link Compatible LVDS Input) Timing Requirements

- 6.9 System Oscillator Timing Requirements

- 6.10 Reset Timing Requirements

- 6.11 Video Timing Input Blanking Specification

- 6.12 Programmable Output Clocks Switching Characteristics

- 6.13 DMD Interface Switching Characteristics

- 6.14 JTAG Interface: I/O Boundary Scan Application Switching Characteristics

- 7 Parameter Measurement Information

- 8 Detailed Description

- 9 Application and Implementation

- 10Power Supply Recommendations

-

11Layout

- 11.1 Layout Guidelines

- 11.2 Layout Example

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- ZFF|419

Thermal pad, mechanical data (Package|Pins)

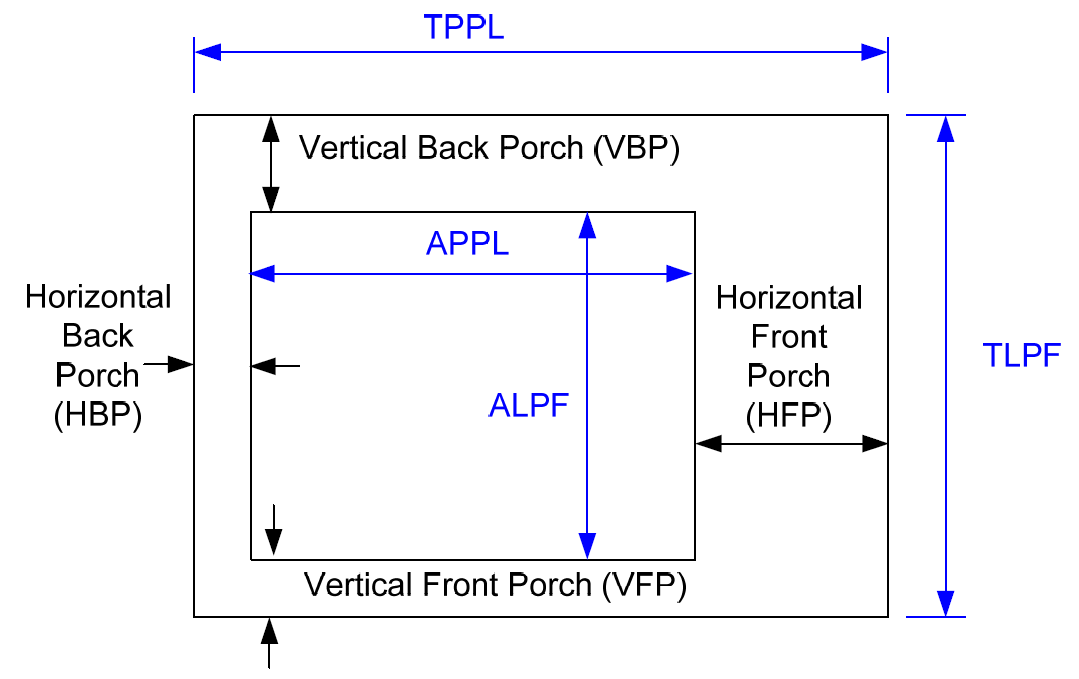

6.11.1 Source Input Blanking

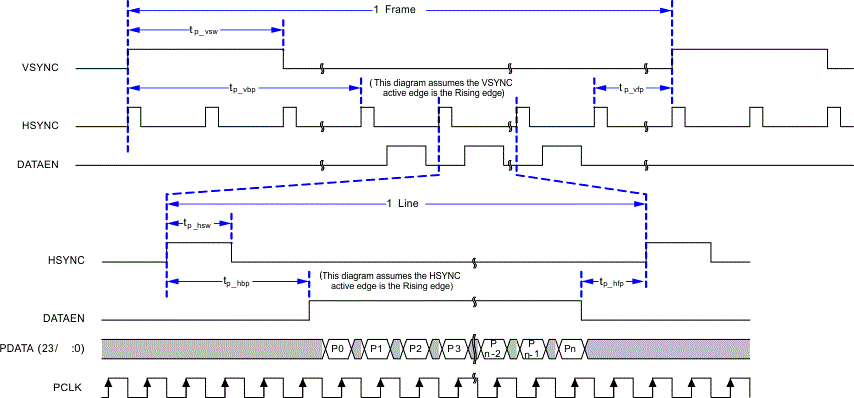

The vertical and horizontal blanking requirements for both input ports are defined in Table 3, except when using a 120 Hz source. In this case, please use the source input blanking timing found in Table 4. Refer to the video timing parameter definitions listed inVideo Timing Parameter Definitions. Also, see Figure 7 for Parallel I/F Frame Timing.

Table 3. Source Input Blanking Requirements

Table 4. 120 Hz Source Input Blanking Timings on Port 1

Figure 6. Horizontal and Vertical Blanking Diagram

Figure 6. Horizontal and Vertical Blanking Diagram  Figure 7. Parallel I/F Frame Timing

Figure 7. Parallel I/F Frame Timing