SNLS542C October 2016 – December 2020 DS280MB810

PRODUCTION DATA

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Description (continued)

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Detailed Description

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- ZBL|135

Thermal pad, mechanical data (Package|Pins)

Orderable Information

9.2.3.1 Pattern Generator Characteristics

All of the example application results in the sections which follow were tested using a pattern generator with the following characteristics.

Figure 9-10 Pattern Generator test setup

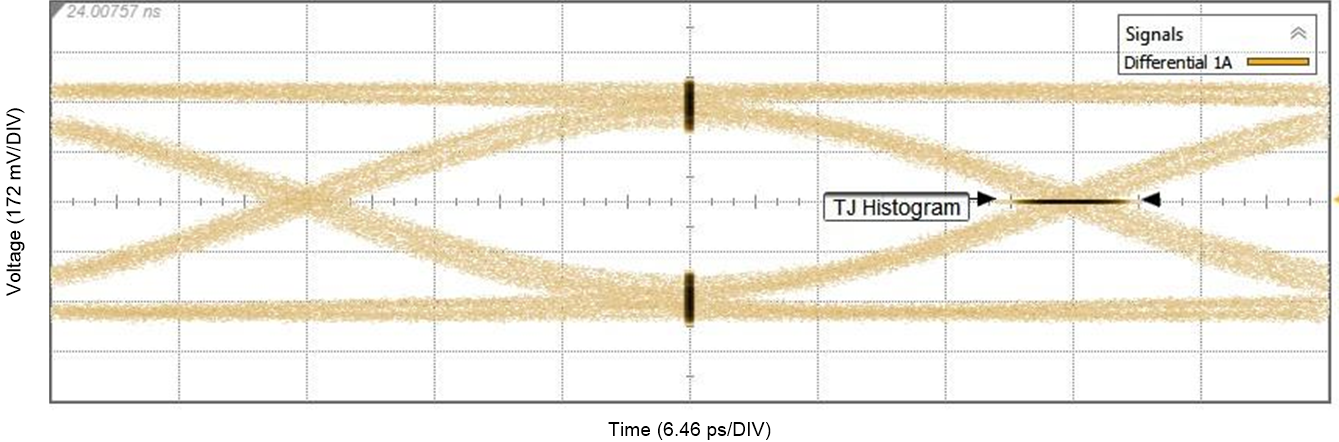

Figure 9-10 Pattern Generator test setup Figure 9-11 Pattern Generator output at 25.78125 Gbps, 800m Vppd, PRBS9

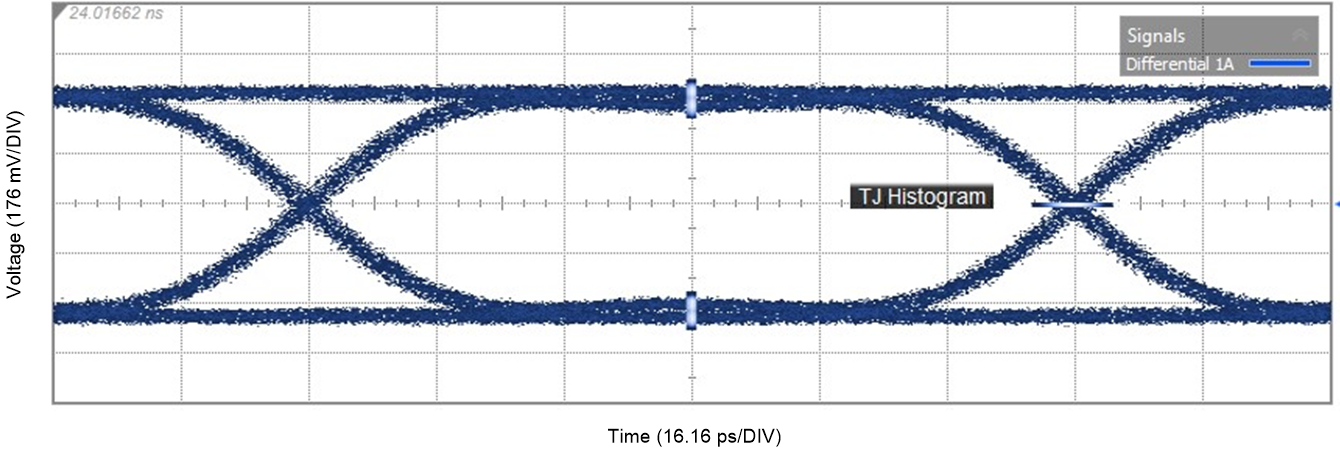

Figure 9-11 Pattern Generator output at 25.78125 Gbps, 800m Vppd, PRBS9 Figure 9-12 Pattern Generator output at 10.31250 Gbps, 800 mVppd, PRBS9

Figure 9-12 Pattern Generator output at 10.31250 Gbps, 800 mVppd, PRBS9Table 9-1 Pattern Generator Characteristics

| 25.78125 Gbps | 10.3125 Gbps | |

|---|---|---|

| Differential peak-to-peak voltage (VOD) | ~800 mVppd | ~800 mVppd |

| Channel loss between Pattern Generator and Scope | 2 dB @ 12.9 GHz | 1 dB @ 5.2 GHz |

| Total Jitter @ 1E-15 | 8.0 psP-P | 13.4 psP-P |

| Differential Eye Height @ 1E-15 | 448 mVP-P | 596 mVP-P |