SNLS201B September 2005 – January 2019 DS90LV028AH

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Parameter Measurement Information

- 8 Detailed Description

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- D|8

Thermal pad, mechanical data (Package|Pins)

Orderable Information

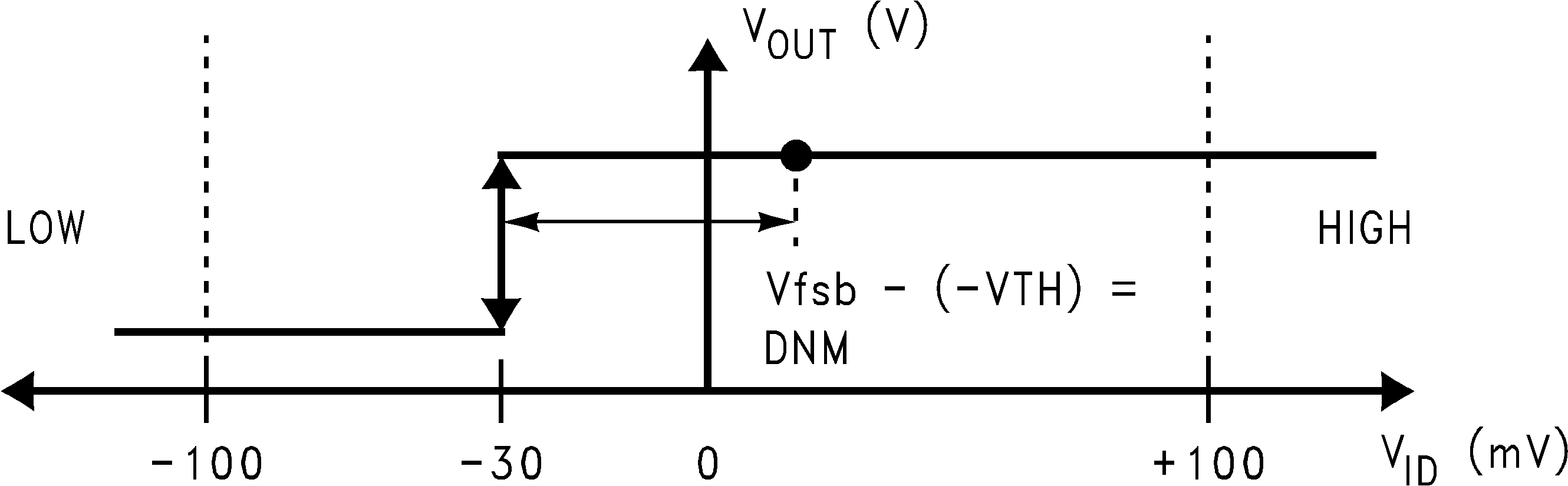

8.3.2 Threshold

The LVDS Standard (ANSI/TIA/EIA-644-A) specifies a maximum threshold of ±100 mV for the LVDS receiver. The DS90LV028AH supports an enhanced threshold region of −100 mV to 0 V. This is useful for fail-safe biasing. The threshold region is shown in the Voltage Transfer Curve (VTC) in Figure 16. The typical DS90LV028AH LVDS receiver switches at about −30 mV. Note that with VID = 0 V, the output will be in a HIGH state. With an external fail-safe bias of +25 mV applied, the typical differential noise margin is now the difference from the switch point to the bias point. In the example shown in Figure 16, this would be 55 mV of Differential Noise Margin (DNM) (+25 mV − (−30 mV)). With the enhanced threshold region of −100 mV to 0 V, this small external fail-safe biasing of +25 mV (with respect to 0 V) gives a DNM of a comfortable 55 mV. With the standard threshold region of ±100 mV, the external fail-safe biasing must be +25 mV with respect to +100 mV or +125 mV, giving a DNM of 155 mV that is a stronger fail-safe biasing than necessary for the DS90LV028AH. If more DNM is required, then a stronger fail-safe bias point can be set by changing resistor values.

Figure 16. VTC of the DS90LV028AH LVDS Receiver

Figure 16. VTC of the DS90LV028AH LVDS Receiver