SBOS014A September 2000 – January 2024 INA114

PRODUCTION DATA

- 1

- 1 Features

- 2 Applications

- 3 Description

- 4 Pin Configuration and Functions

- 5 Specifications

- 6 Application and Implementation

- 7 Typical Applications

- 8 Device and Documentation Support

- 9 Revision History

- 10Mechanical, Packaging, and Orderable Information

Package Options

Refer to the PDF data sheet for device specific package drawings

Mechanical Data (Package|Pins)

- P|8

- DW|16

Thermal pad, mechanical data (Package|Pins)

- DW|16

Orderable Information

6.1.3 Offset Trimming

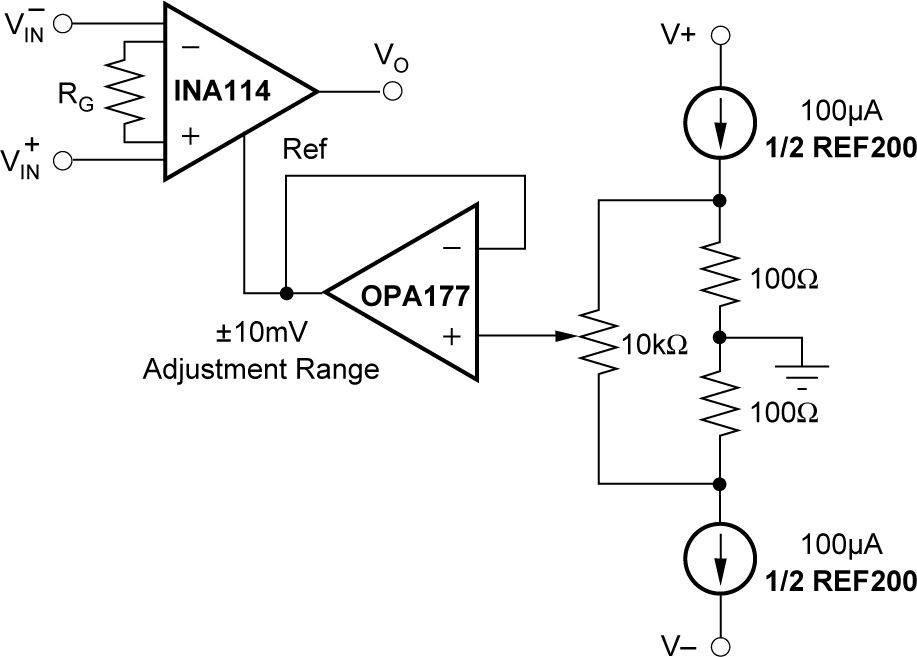

The INA114 is laser trimmed for very low offset voltage and drift. Most applications require no external offset adjustment. Figure 6-2 shows an optional circuit for trimming the output offset voltage. The voltage applied to the Ref pin is summed at the output. Maintain low impedance at this node to maintain good common-mode rejection by buffering trim voltage with an op amp as shown.

Figure 6-2 Optional Trimming of Output Offset Voltage.

Figure 6-2 Optional Trimming of Output Offset Voltage.