SNOSBI3C July 2000 – October 2018 LF198-N , LF298 , LF398-N

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 Recommended Operating Conditions

- 6.3 Thermal Information

- 6.4 Electrical Characteristics, LF198-N and LF298

- 6.5 Electrical Characteristics, LF198A-N

- 6.6 Electrical Characteristics, LF398-N

- 6.7 Electrical Characteristics, LF398A-N (OBSOLETE)

- 6.8 Typical Characteristics

- 7 Parameter Measurement Information

- 8 Detailed Description

-

9 Application and Implementation

- 9.1 Application Information

- 9.2

Typical Applications

- 9.2.1 X1000 Sample and Hold

- 9.2.2 Sample and Difference Circuit

- 9.2.3 Ramp Generator With Variable Reset Level

- 9.2.4 Integrator With Programmable Reset Level

- 9.2.5 Output Holds at Average of Sampled Input

- 9.2.6 Increased Slew Current

- 9.2.7 Reset Stabilized Amplifier

- 9.2.8 Fast Acquisition, Low Droop Sample and Hold

- 9.2.9 Synchronous Correlator for Recovering Signals Below Noise Level

- 9.2.10 2-Channel Switch

- 9.2.11 DC and AC Zeroing

- 9.2.12 Staircase Generator

- 9.2.13 Differential Hold

- 9.2.14 Capacitor Hysteresis Compensation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- LMC|8

Thermal pad, mechanical data (Package|Pins)

Orderable Information

9.1.5 Digital Feedthrough

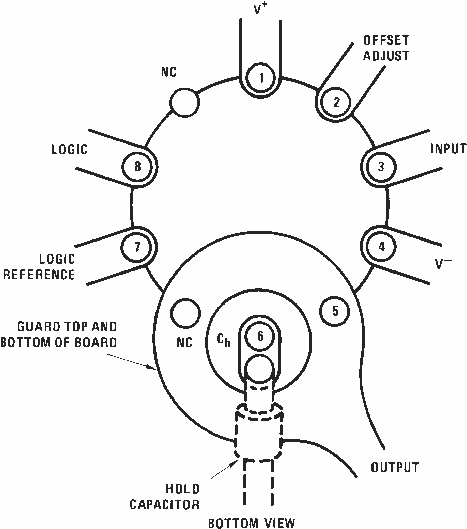

Fast rise time logic signals can cause hold errors by feeding externally into the analog input at the same time the amplifier is put into the hold mode. To minimize this problem, board layout should keep logic lines as far as possible from the analog input and the Ch pin. Grounded guarding traces may also be used around the input line, especially if it is driven from a high impedance source. Reducing high amplitude logic signals to 2.5 V will also help.

Use 10-pin layout. Guard around CH is tied to output.

Figure 24. Guarding Technique