SNAS558N January 2000 – March 2024 LMC555

PRODUCTION DATA

- 1

- 1 Features

- 2 Applications

- 3 Description

- 4 Pin Configuration and Functions

- 5 Specifications

- 6 Parameter Measurement Information

- 7 Detailed Description

- 8 Application and Implementation

- 9 Device and Documentation Support

- 10Revision History

- 11Mechanical, Packaging, and Orderable Information

Package Options

Refer to the PDF data sheet for device specific package drawings

Mechanical Data (Package|Pins)

- D|8

- P|8

- YPB|8

- DGK|8

Thermal pad, mechanical data (Package|Pins)

Orderable Information

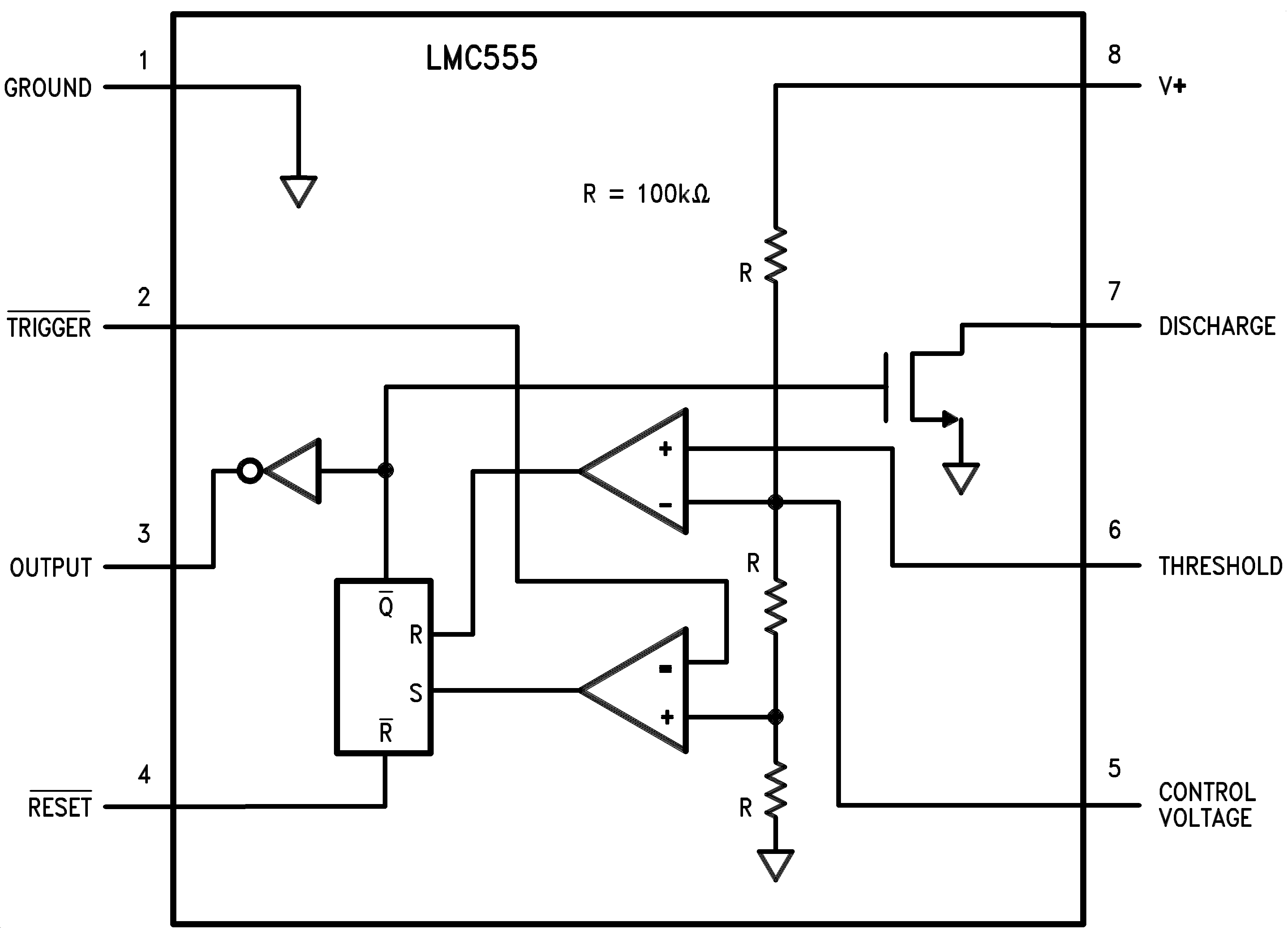

4 Pin Configuration and Functions

Figure 4-1 D Package, 8-Pin SOIC,

Figure 4-1 D Package, 8-Pin SOIC, DGK Package, 8-Pin VSSOP,

and P Package, 8-Pin PDIP (Top View)

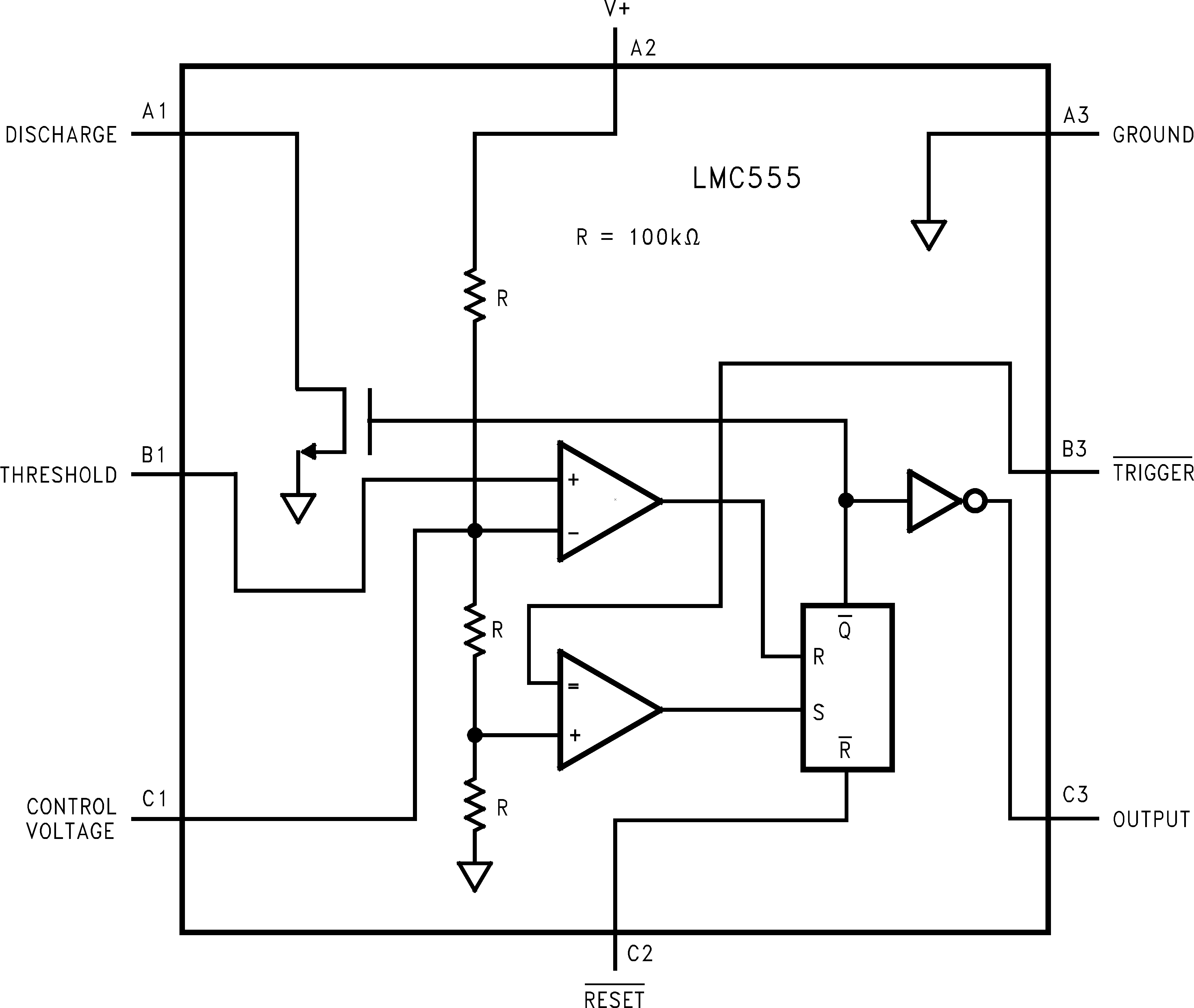

Figure 4-2 YPB Package, 8-Pin DSBGA

(Top View)

Figure 4-2 YPB Package, 8-Pin DSBGA

(Top View)Table 4-1 Pin Functions

| PIN | TYPE | DESCRIPTION | ||

|---|---|---|---|---|

| NAME | NO. | |||

| D (SOIC), DGK (VSSOP), P (PDIP) | YPB (DSBGA) | |||

| CONTROL VOLTAGE | 5 | C1 | Input | Control voltage controls the threshold and trigger levels. This pin determines the pulse duration of the output waveform. An external voltage applied to this pin can also be used to modulate the output waveform. |

| DISCHARGE | 7 | A1 | Input | Open collector output that discharges a capacitor between intervals (in phase with output). This pin toggles the output from high to low when voltage reaches 2/3 of the supply voltage (V+). |

| GROUND | 1 | A3 | Power | Ground reference voltage |

| OUTPUT | 3 | C3 | Output | Output driven waveform |

| RESET | 4 | C2 | Input | Negative pulse applied to this pin to disable or reset the timer. When not used for reset purposes, connect this pin to V+ to avoid false triggering. |

| THRESHOLD | 6 | B1 | Input | Compares the voltage applied to the pin with a reference voltage of 2/3 V+. The amplitude of voltage applied to this pin is responsible for the set state of the flip-flop. |

| TRIGGER | 2 | B3 | Input | Responsible for transition of the flip-flop from set to reset. The output of the timer depends on the amplitude of the external trigger pulse applied to this pin. |

| V+ | 8 | A2 | Power | Supply voltage with respect to ground |