SNVS083O February 2005 – March 2015 LP2989

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

Thermal pad, mechanical data (Package|Pins)

Orderable Information

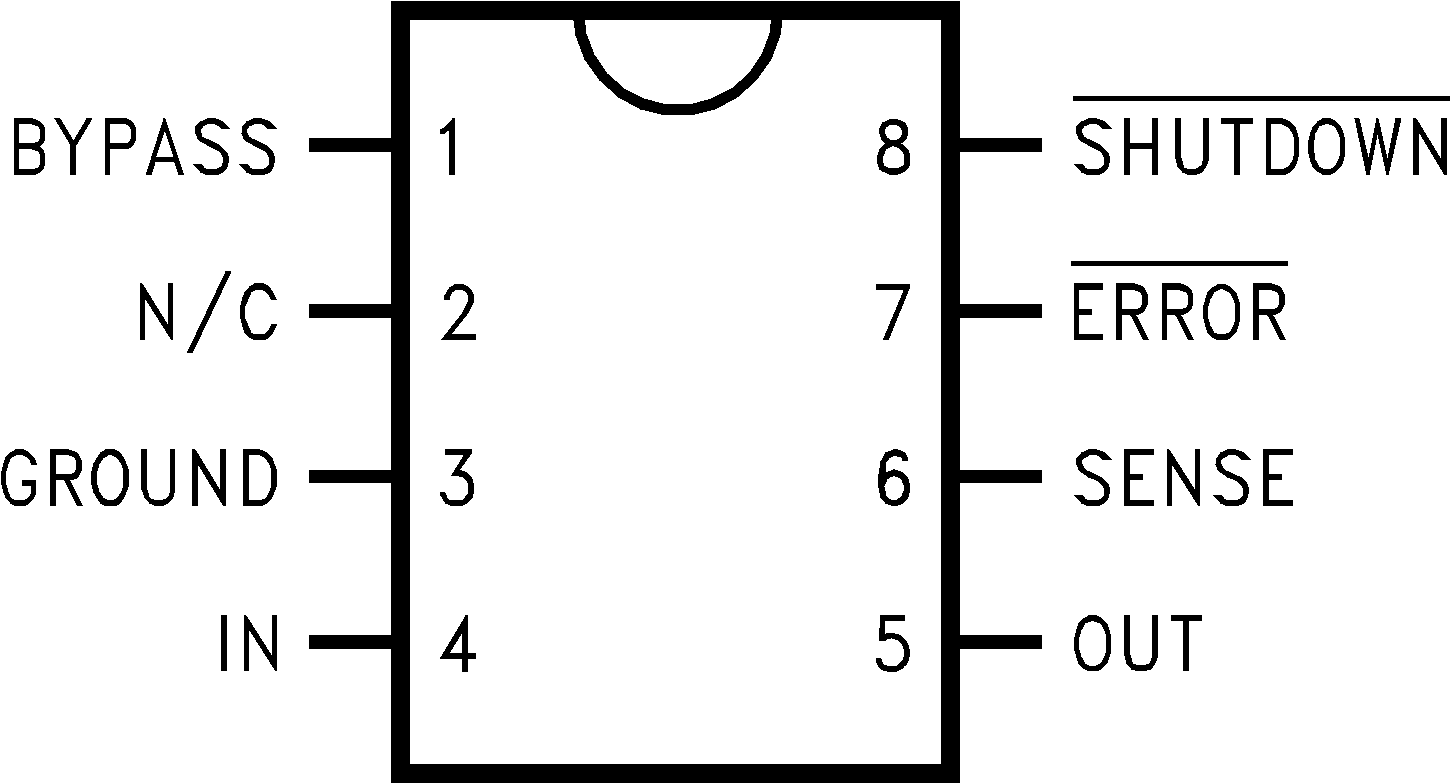

5 Pin Configuration and Functions

D/DGK Packages

8-Pin SOIC and VSSOP

Top View

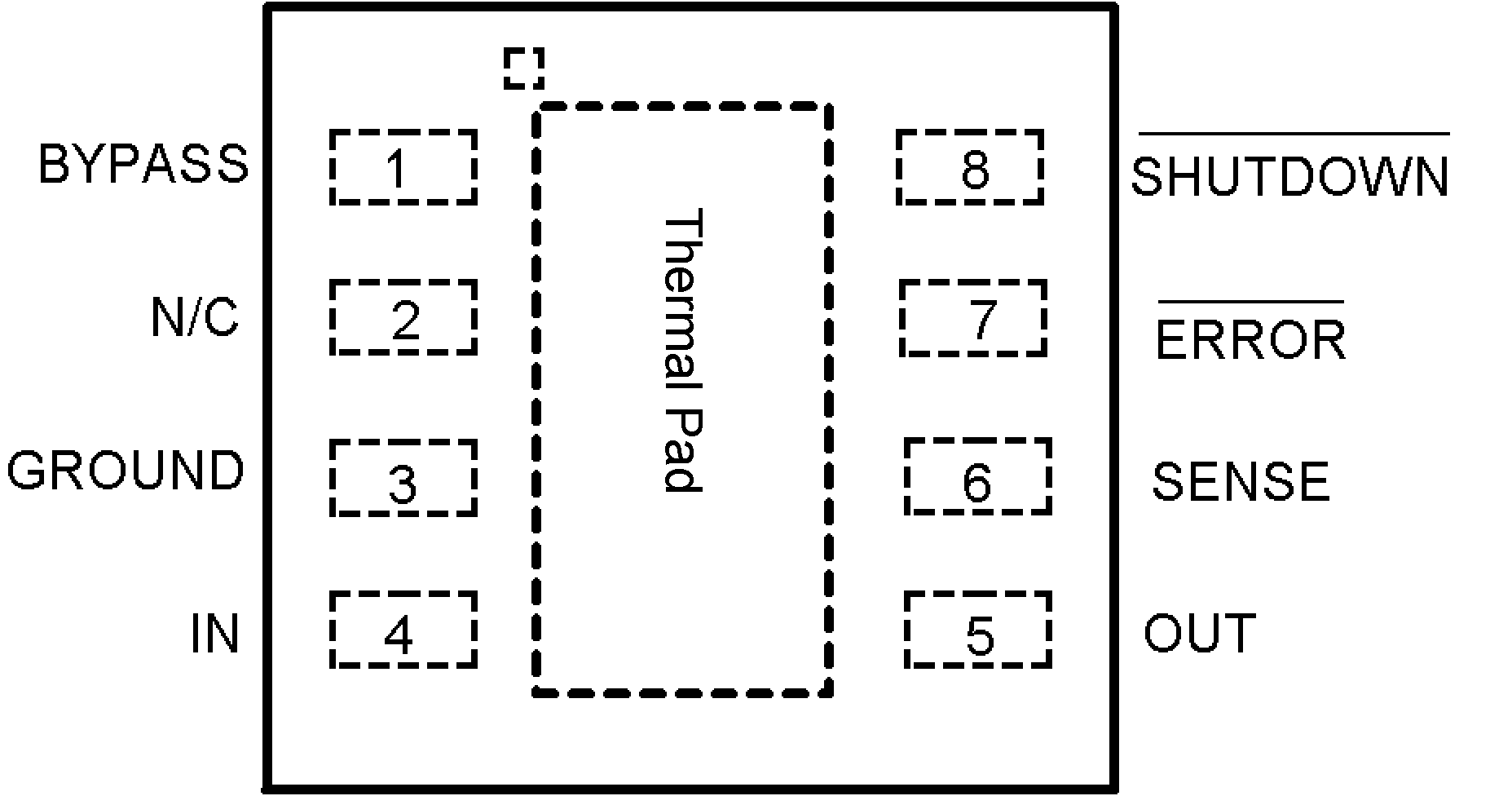

NGN Package

8-Lead WSON

Top View

Pin Functions

| PIN | I/O | DESCRIPTION | |

|---|---|---|---|

| NAME | NO. | ||

| BYPASS | 1 | I | Bypass capacitor input |

| ERROR | 7 | O | Error signal output |

| GROUND | 3 | — | GND |

| INPUT | 4 | I | Regulator power input |

| N/C | 2 | — | DO NOT CONNECT. Device pin 2 is reserved for post packaging test and calibration of the LP2989 VOUT accuracy. Device pin 2 must be left floating. Do not connect to any potential. Do not connect to ground. Any attempt to do pin continuity testing on device pin 2 is discouraged. Continuity test results will be variable depending on the actions of the factory calibration. Aggressive pin continuity testing (high voltage, or high current) on device pin 2 may activate the trim circuitry forcing VOUT to move out of tolerance. |

| OUTPUT | 5 | O | Regulated output voltage |

| SENSE | 6 | I | Feedback voltage sense input |

| SHUTDOWN | 8 | I | Shutdown input |

| Thermal Pad | — | — | The exposed thermal pad on the bottom of the WSON package should be connected to a copper thermal pad on the PCB under the package. The use of thermal vias to remove heat from the package into the PCB is recommended. Connect the thermal pad to ground potential or leave floating. Do not connect the thermal pad to any potential other than the same ground potential seen at device pin 3. For additional information on using TI's Non Pull Back WSON package, see Application Note AN-1187 Leadless Leadframe Package (LLP) (SNOA401). |