SNVS337F June 2006 – September 2015 LP38859

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Specifications

- 6 Detailed Description

- 7 Application and Implementation

- 8 Power Supply Recommendations

- 9 Layout

- 10Device and Documentation Support

- 11Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

Thermal pad, mechanical data (Package|Pins)

- KTT|5

Orderable Information

5 Specifications

5.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)(2)| MIN | MAX | UNIT | ||

|---|---|---|---|---|

| VIN supply voltage (survival) | −0.3 | 6 | V | |

| VBIAS supply voltage (survival) | −0.3 | 6 | V | |

| VSS soft-start voltage (survival) | −0.3 | 6 | V | |

| VOUT voltage (survival) | −0.3 | 6 | V | |

| IOUT current (survival) | Internally limited | |||

| Power dissipation(3) | Internally limited | |||

| Junction temperature | 40 | 150 | °C | |

| Storage temperature, Tstg | −65 | 150 | °C | |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) If Military/Aerospace specified devices are required, contact the TI Sales Office/ Distributors for availability and specifications.

(3) Device power dissipation must be de-rated based on device power dissipation (PD), ambient temperature (TA), and package junction to ambient thermal resistance (RθJA). Additional heat-sinking may be required to ensure that the device junction temperature (TJ) does not exceed the maximum operating rating. See the Application and Implementation section for details.

5.2 ESD Ratings

| VALUE | UNIT | |||

|---|---|---|---|---|

| V(ESD) | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001(1) | ±2000 | V |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

5.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)| MIN | NOM | MAX | UNIT | ||

|---|---|---|---|---|---|

| VIN supply voltage | (VOUT + VDO) | VBIAS | V | ||

| VBIAS supply voltage | 3 | 5.5 | V | ||

| IOUT | 0 | 3 | A | ||

| Junction temperature(1) | −40 | 125 | °C | ||

(1) Device power dissipation must be de-rated based on device power dissipation (PD), ambient temperature (TA), and package junction to ambient thermal resistance (RθJA). Additional heat-sinking may be required to ensure that the device junction temperature (TJ) does not exceed the maximum operating rating. See the Application and Implementation section for details.

5.4 Thermal Information

| THERMAL METRIC(1) | LP38859 | UNIT | ||

|---|---|---|---|---|

| KTT (DDPAK/TO-263 | NDH (TO-220) | |||

| 5 PINS | 5 PINS | |||

| RθJA | Junction-to-ambient thermal resistance | 43.2 | 70.7(2) | °C/W |

| RθJC(top) | Junction-to-case (top) thermal resistance | 43.5 | 43.0 | °C/W |

| RθJB | Junction-to-board thermal resistance | 23.1 | n/a(2) | °C/W |

| ψJT | Junction-to-top characterization parameter | 11.6 | 23.6(2) | °C/W |

| ψJB | Junction-to-board characterization parameter | 22.0 | 52.2(2) | °C/W |

| RθJC(bot) | Junction-to-case (bottom) thermal resistance | 1.1 | 1.3 | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

(2) The NDH (TO-220) package is vertically mounted in center of JEDEC High-K test board (JESD 51-7) with no additional heat sink. This is a through-hole package; this is NOT a surface mount package.

5.5 Electrical Characteristics

Unless otherwise specified: VIN = VOUT(NOM) + 1 V, VBIAS = 3 V, IOUT = 10 mA, CIN = COUT = 10 µF, CBIAS = 1 µF, CSS = open. Typical limits apply for TJ = 25°C; minimum and maximum limits apply over the junction temperature (TJ) range of -40°C to +125°C, unless otherwise specified. Minimum and maximum limits are specified through test, design, or statistical correlation. Typical values represent the most likely parametric norm at TJ = 25°C, and are provided for reference purposes only.| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| VOUT | VOUT accuracy | VOUT(NOM) + 1 V ≤ VIN ≤ VBIAS

3 V ≤ VBIAS ≤ 5.5 V 10 mA ≤ IOUT ≤ 3 A, TJ = 25°C |

-1% | 1% | ||

| VOUT(NOM) + 1 V ≤ VIN ≤ VBIAS

3 V ≤ VBIAS ≤ 5.5 V 10 mA ≤ IOUT ≤ 3 A |

–3% | 3% | ||||

| VOUT(NOM) + 1 V ≤ VIN ≤ VBIAS

3 V ≤ VBIAS ≤ 5.5 V 10 mA ≤ IOUT ≤ 3 A 0°C ≤ TJ ≤ +125°C |

–2% | 2% | ||||

| ΔVOUT/ΔVIN | Line regulation, VIN(1) | VOUT(NOM) + 1 V ≤ VIN ≤ VBIAS | 0.04 | %/V | ||

| ΔVOUT/ΔVBIAS | Line regulation, VBIAS(1) | 3 V ≤ VBIAS ≤ 5.5 V | 0.10 | %/V | ||

| ΔVOUT/ΔIOUT | Output voltage load regulation(2) | 10 mA ≤ IOUT ≤ 3 A | 0.2 | %/A | ||

| VDO | Dropout voltage(3) | IOUT = 3 A, TJ = 25°C | 240 | 300 | mV | |

| IOUT = 3 A | 450 | |||||

| IGND(IN) | Quiescent current drawn from VIN supply |

LP38859-0.8 10 mA ≤ IOUT ≤ 3 A, TJ = 25°C |

7 | 8.5 | mA | |

| LP38859-0.8 10 mA ≤ IOUT ≤ 3 A |

9 | |||||

| LP38859-1.2 10 mA ≤ IOUT ≤ 3 A, TJ = 25°C |

11 | 12 | ||||

| LP38859-1.2 10 mA ≤ IOUT ≤ 3 A |

15 | |||||

| IGND(BIAS) | Quiescent current drawn from VBIAS supply | 10 mA ≤ IOUT ≤ 3 A, TJ = 25°C | 3 | 3.8 | mA | |

| 10 mA ≤ IOUT ≤ 3 A | 4.5 | |||||

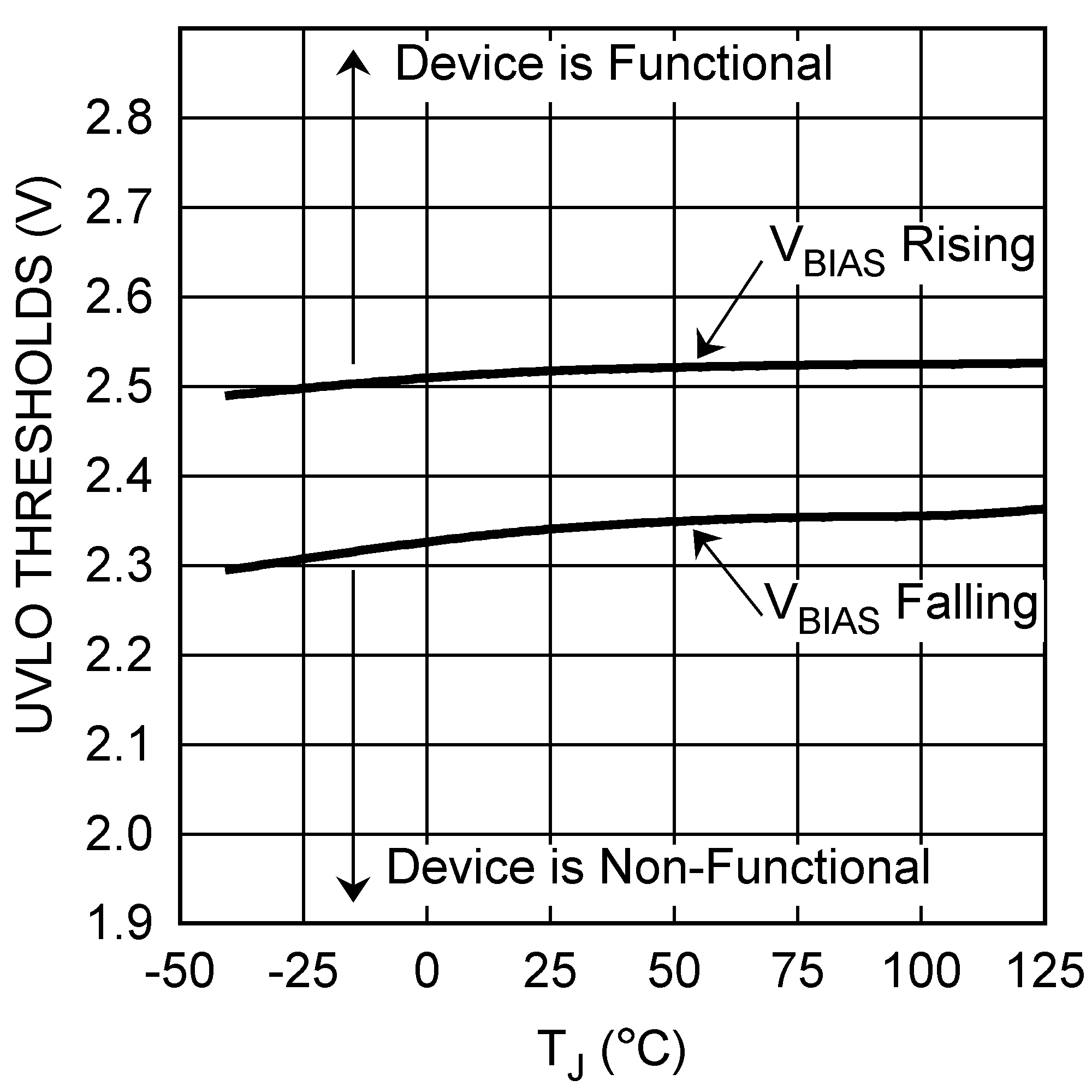

| UVLO | Undervoltage lockout threshold | VBIAS rising until device is functional TJ = 25°C |

2.2 | 2.45 | 2.7 | V |

| VBIAS rising until device is functional | 2 | 2.9 | ||||

| UVLO(HYS) | Undervoltage lockout hysteresis | VBIAS falling from UVLO threshold until device is non-functional TJ = 25°C |

60 | 150 | 300 | mV |

| VBIAS falling from UVLO threshold until device is non-functional | 50 | 350 | ||||

| ISC | Output short-circuit current | VIN = VOUT(NOM) + 1 V | 6.2 | A | ||

| VBIAS = 3 V, VOUT = 0 V | ||||||

| SOFT-START | ||||||

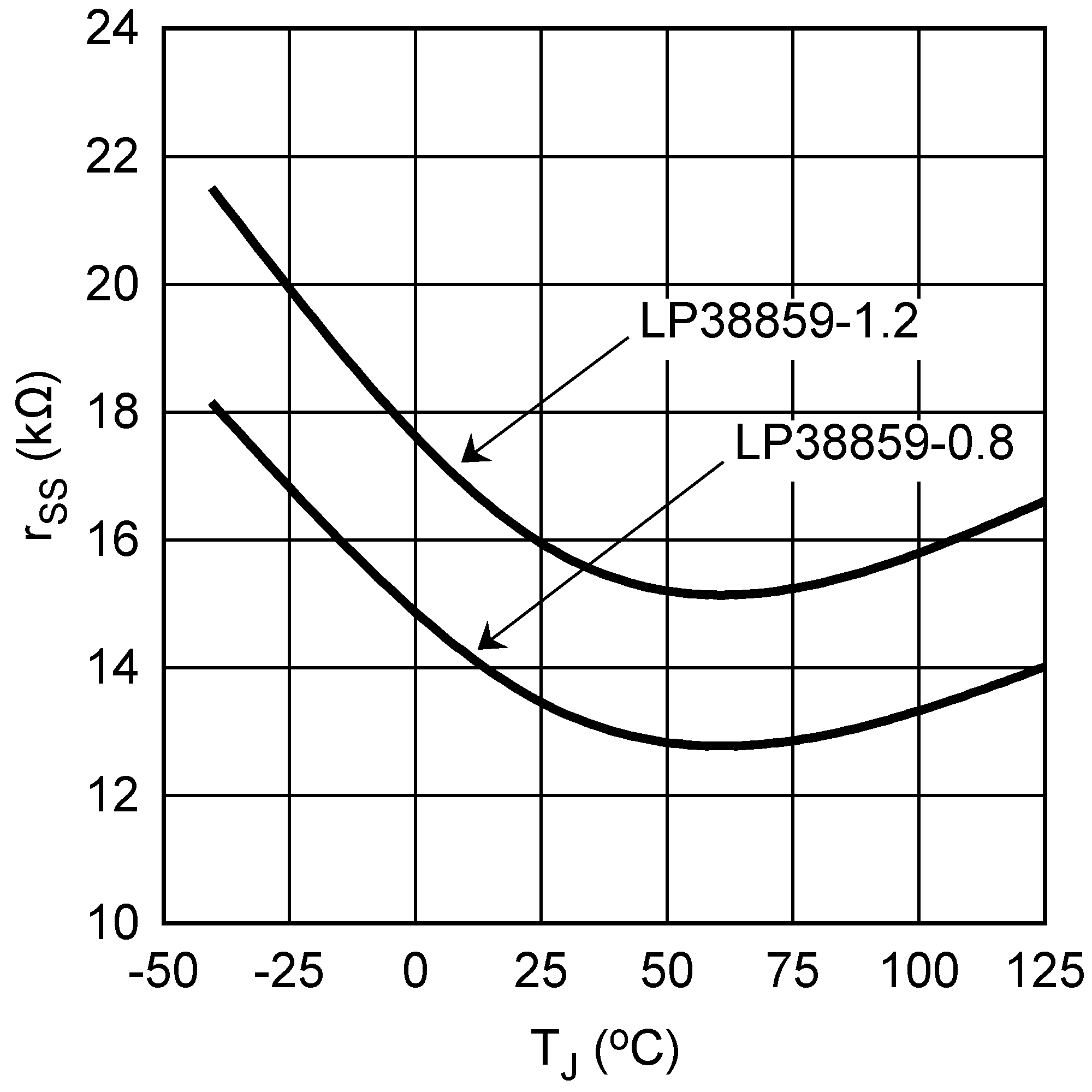

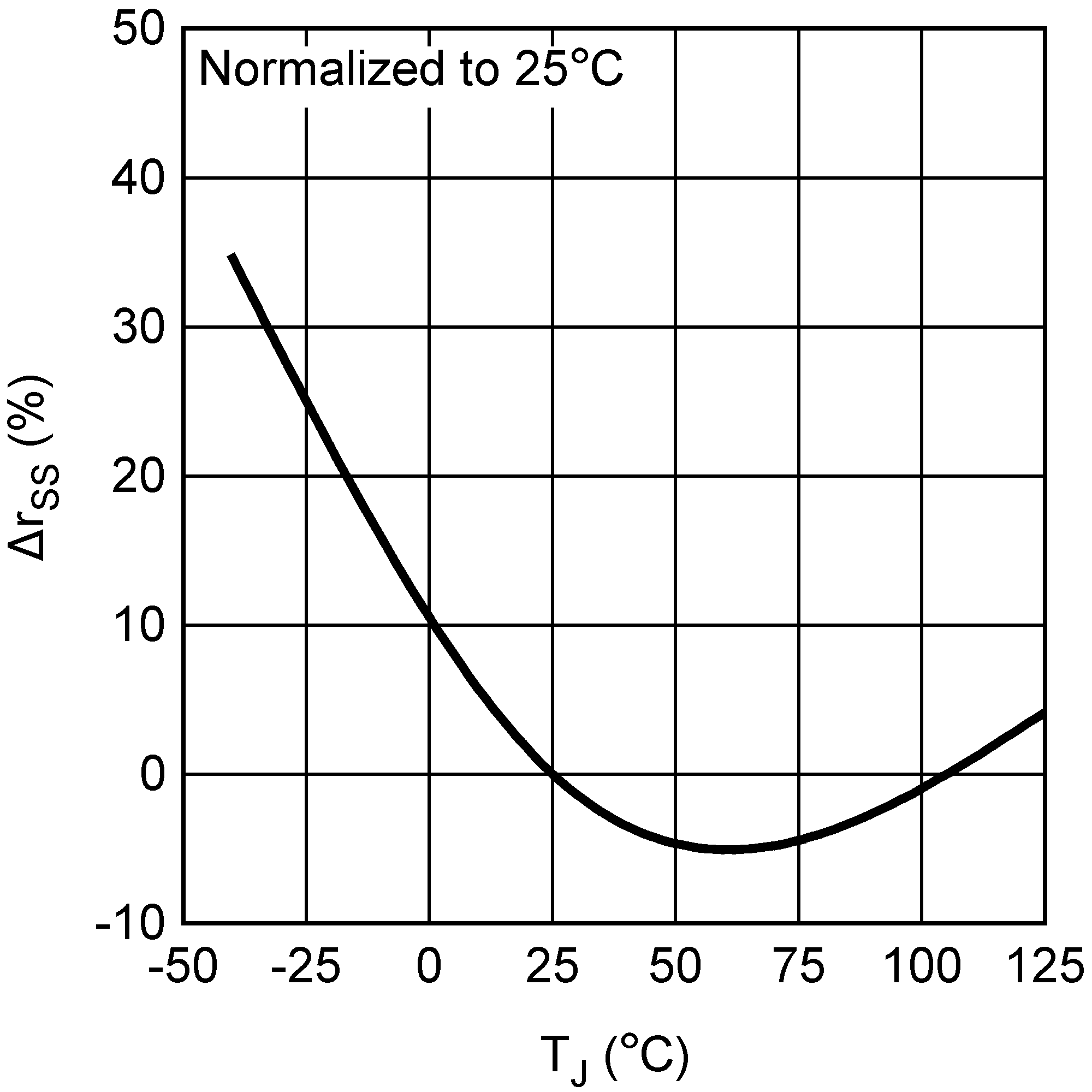

| rSS | Soft-start internal resistance | LP38859-0.8 | 11 | 13.5 | 16 | kΩ |

| LP38859-1.2 | 13.5 | 16 | 18.5 | |||

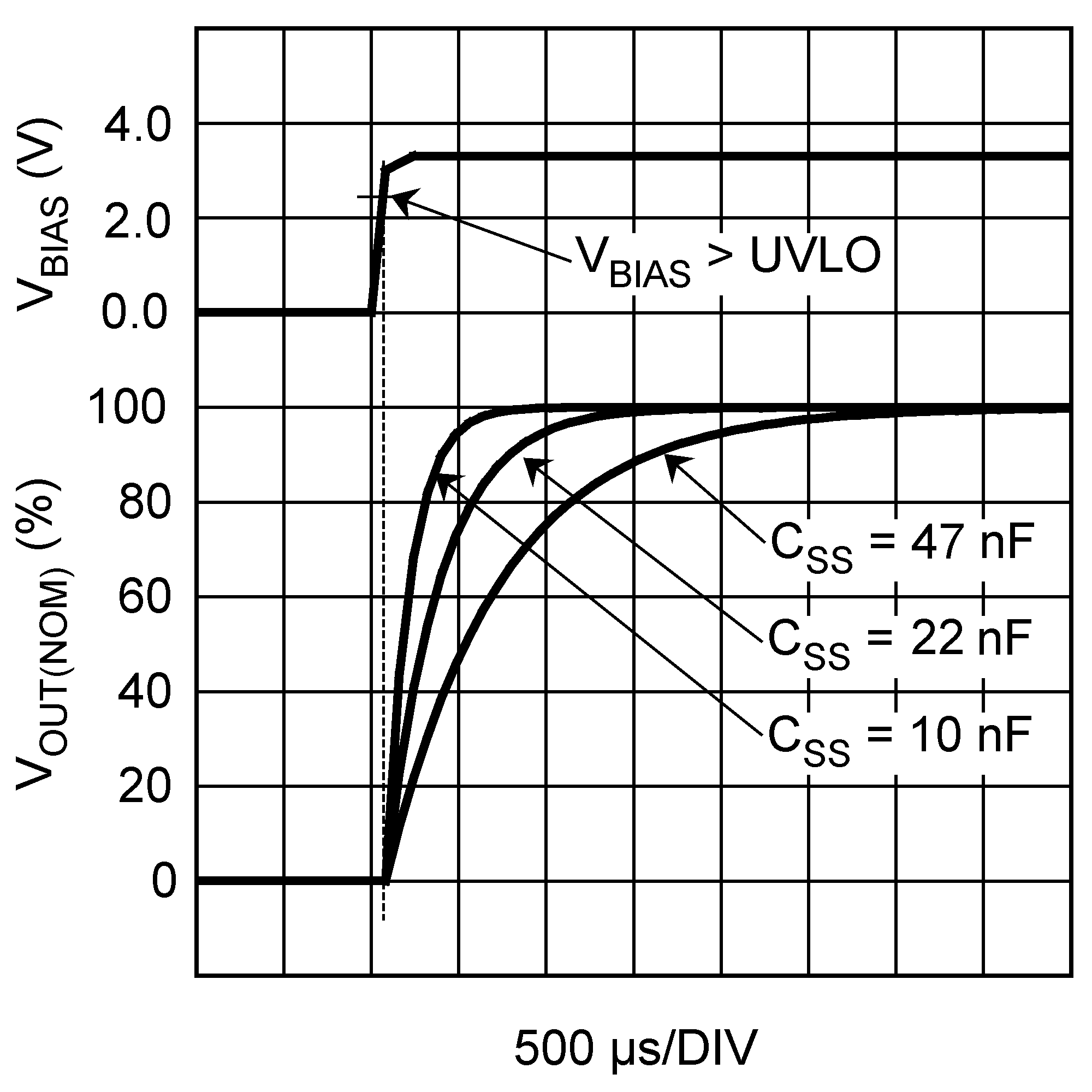

| tSS | Soft-start time tSS = CSS × rSS × 5 |

LP38859-0.8, CSS = 10 nF | 675 | μs | ||

| LP38859-1.2, CSS = 10 nF | 800 | |||||

| AC PARAMETERS | ||||||

| PSRR (VIN) |

Ripple rejection for VIN input voltage | VIN = VOUT(NOM) + 1 V ƒ = 120 Hz |

80 | dB | ||

| VIN = VOUT(NOM) + 1 V ƒ = 1 kHz |

65 | |||||

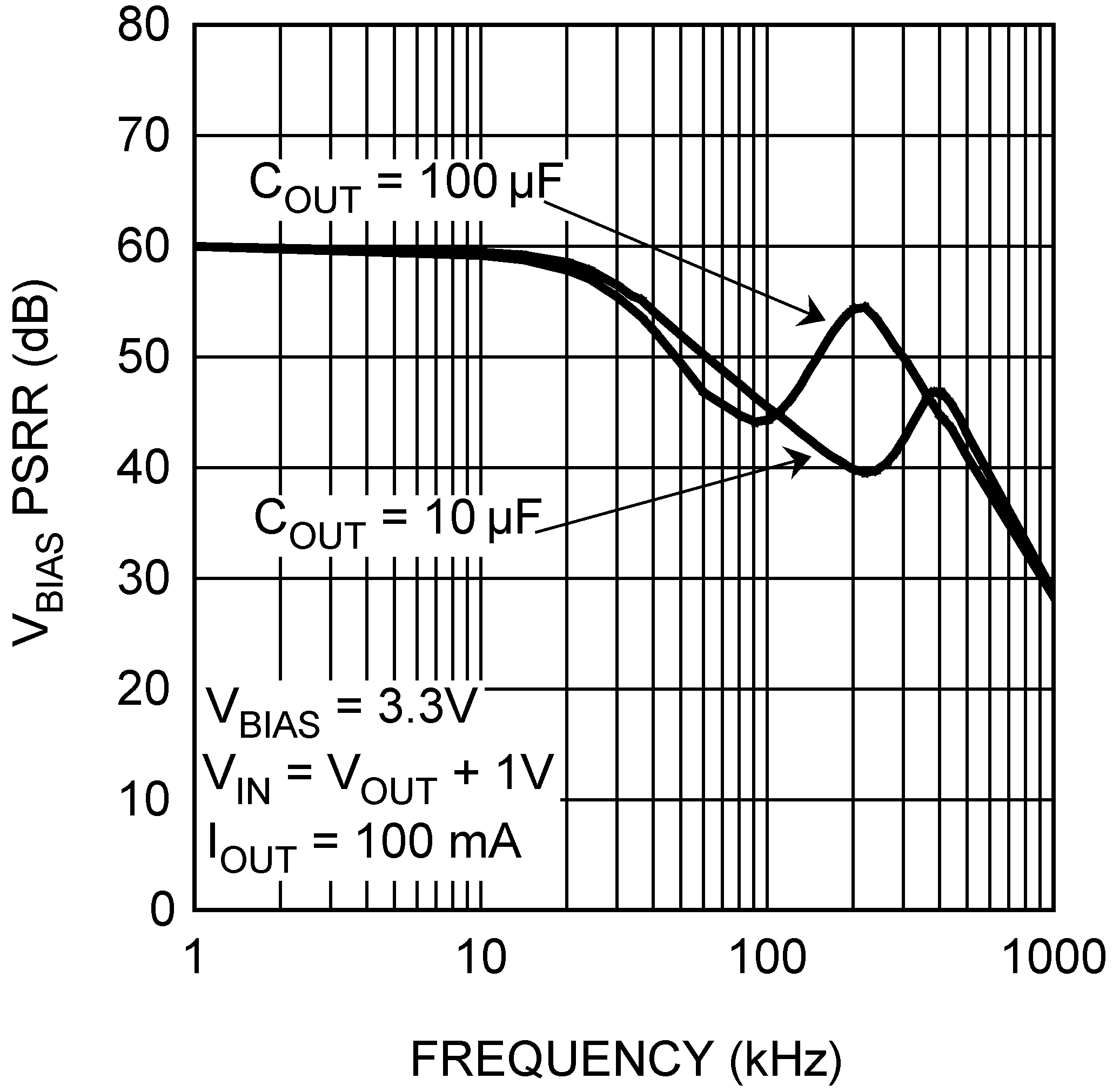

| PSRR (VBIAS) |

Ripple rejection for VBIAS voltage | VBIAS = VOUT(NOM) + 3 V f = 120 Hz |

58 | |||

| VBIAS = VOUT(NOM) + 3 V ƒ = 1 kHz |

58 | |||||

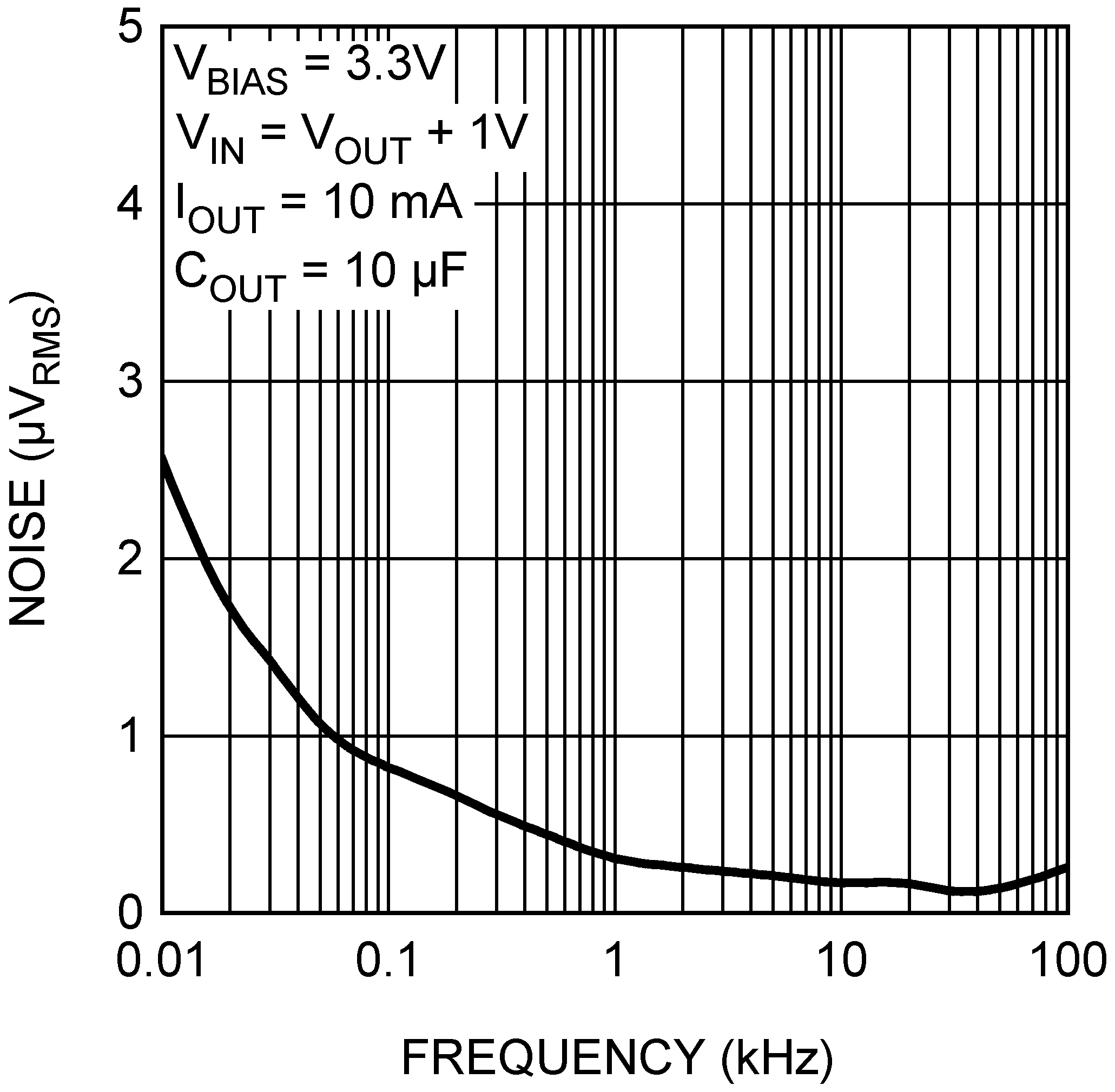

| en | Output noise density | ƒ = 120 Hz | 1 | µV/√Hz | ||

| Output noise voltage | BW = 10 Hz − 100 kHz, VOUT = 1.8 V | 150 | µVRMS | |||

| BW = 300 Hz − 300 kHz, VOUT = 1.8 V | 90 | |||||

| THERMAL PARAMETERS | ||||||

| TSD | Thermal shutdown junction temperature | 160 | °C | |||

| TSD(HYS) | Thermal shutdown hysteresis | 10 | °C | |||

(1) Output voltage line regulation is defined as the change in output voltage from nominal value resulting from a change in input voltage.

(2) Output voltage load regulation is defined as the change in output voltage from nominal value as the load current increases from no load to full load.

(3) Dropout voltage is defined the as input to output voltage differential (VIN – VOUT) where the input voltage is low enough to cause the output voltage to drop no more than 2% from the nominal value.

5.6 Typical Characteristics

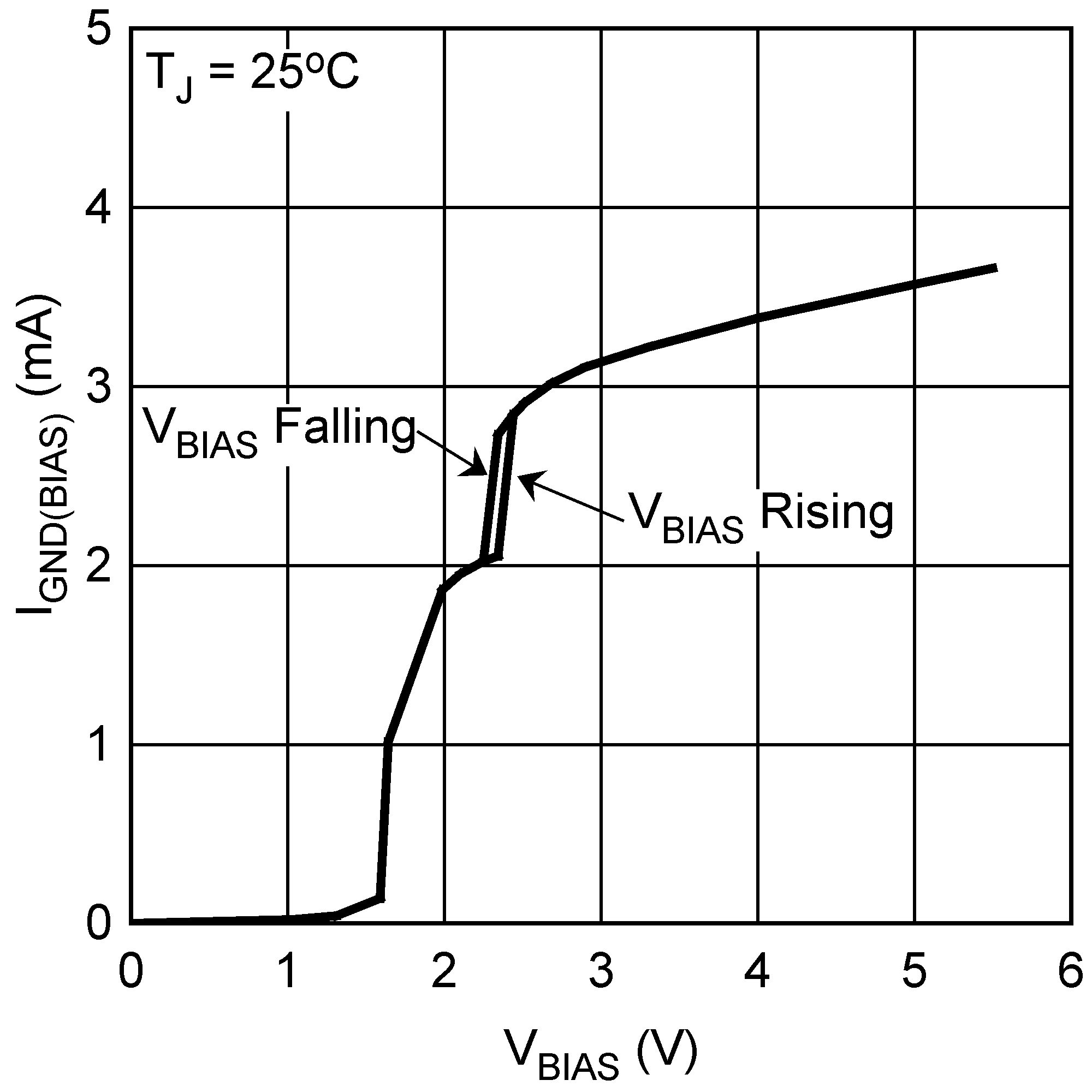

Unless otherwise specified: TJ = 25°C, VIN = VOUT(NOM) + 1 V, VBIAS = 3 V, IOUT = 10 mA, CIN = COUT = 10-µF ceramic, CBIAS = 1-µF ceramic, CSS = open. Figure 1. VBIAS Ground Pin Current (IGND(BIAS)) vs VBIAS

Figure 1. VBIAS Ground Pin Current (IGND(BIAS)) vs VBIAS

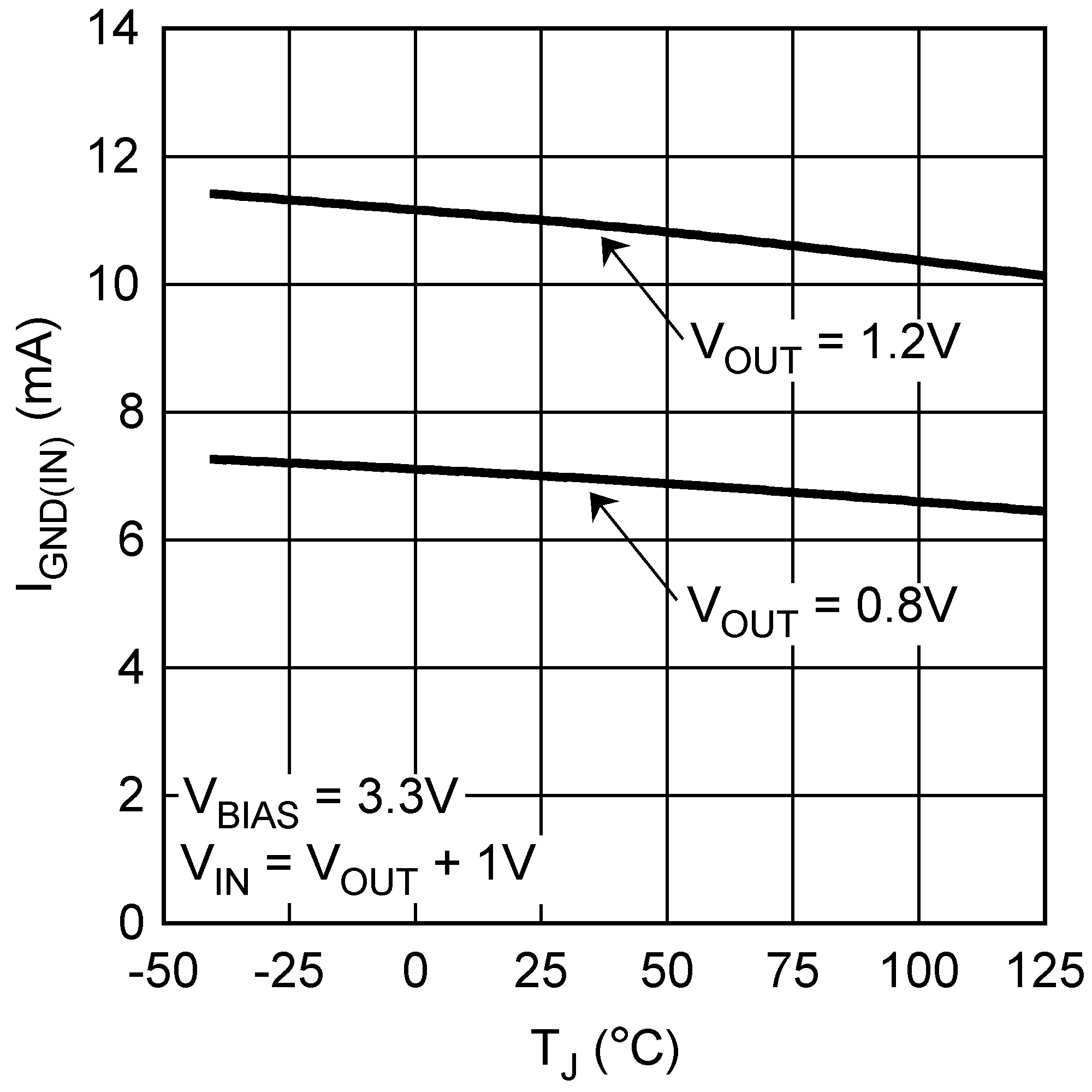

Figure 3. VIN Ground Pin Current vs Temperature

Figure 3. VIN Ground Pin Current vs Temperature

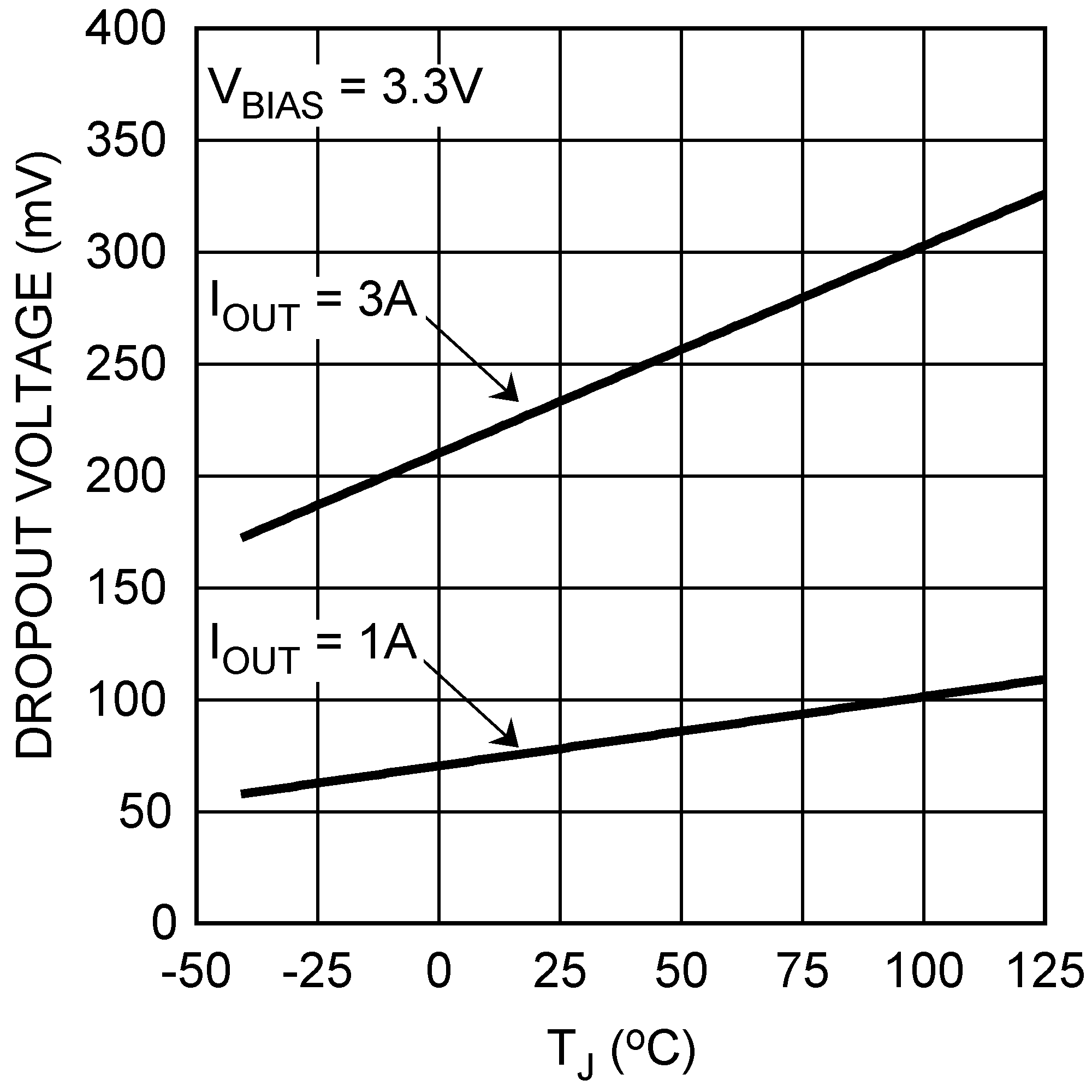

Figure 5. Dropout Voltage (VDO) vs Temperature

Figure 5. Dropout Voltage (VDO) vs Temperature

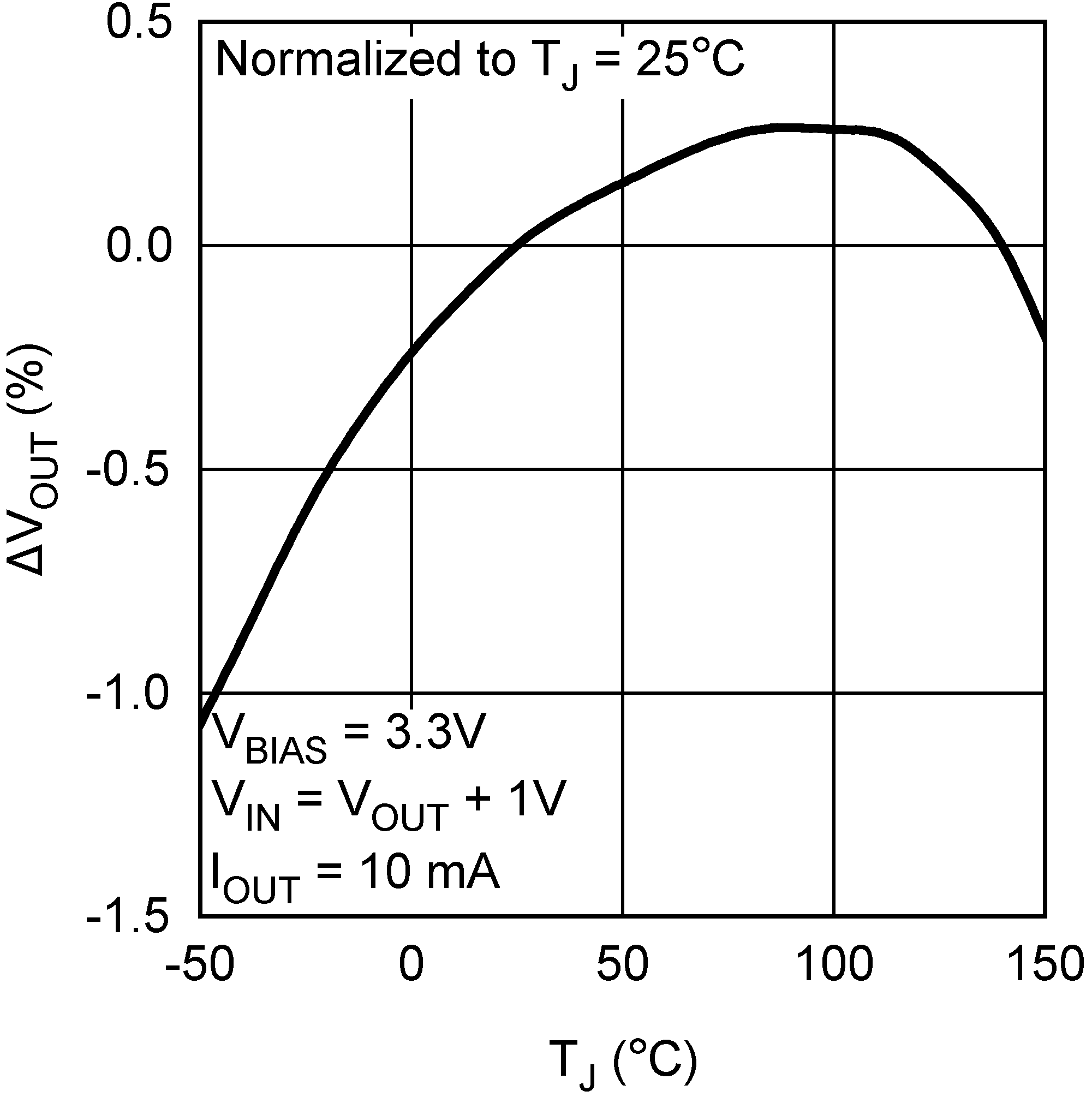

Figure 7. VOUT vs Temperature

Figure 7. VOUT vs Temperature

Figure 9. Soft-Start Resistor (RSS) vs Temperature

Figure 9. Soft-Start Resistor (RSS) vs Temperature

| 10 nF To 47 nF |

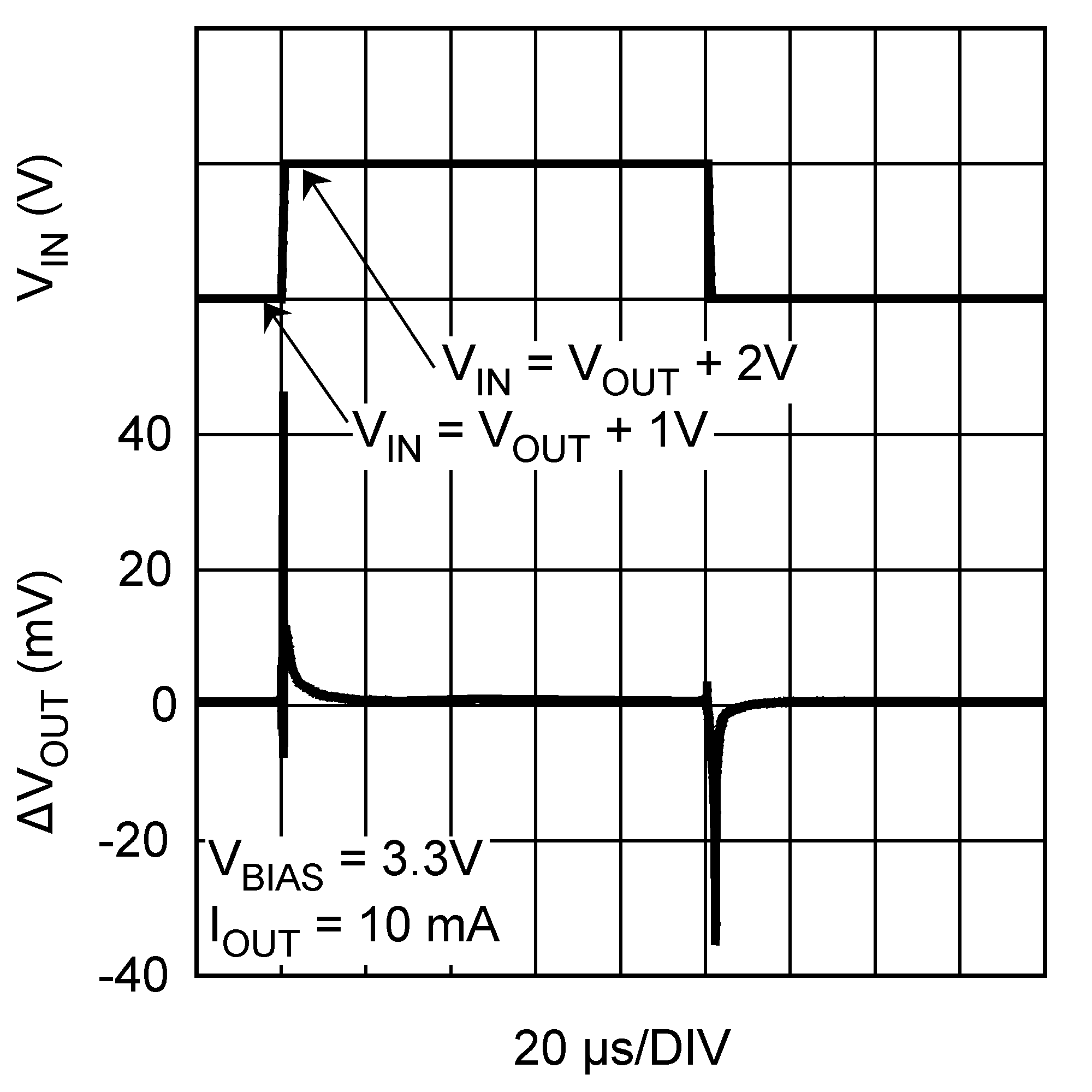

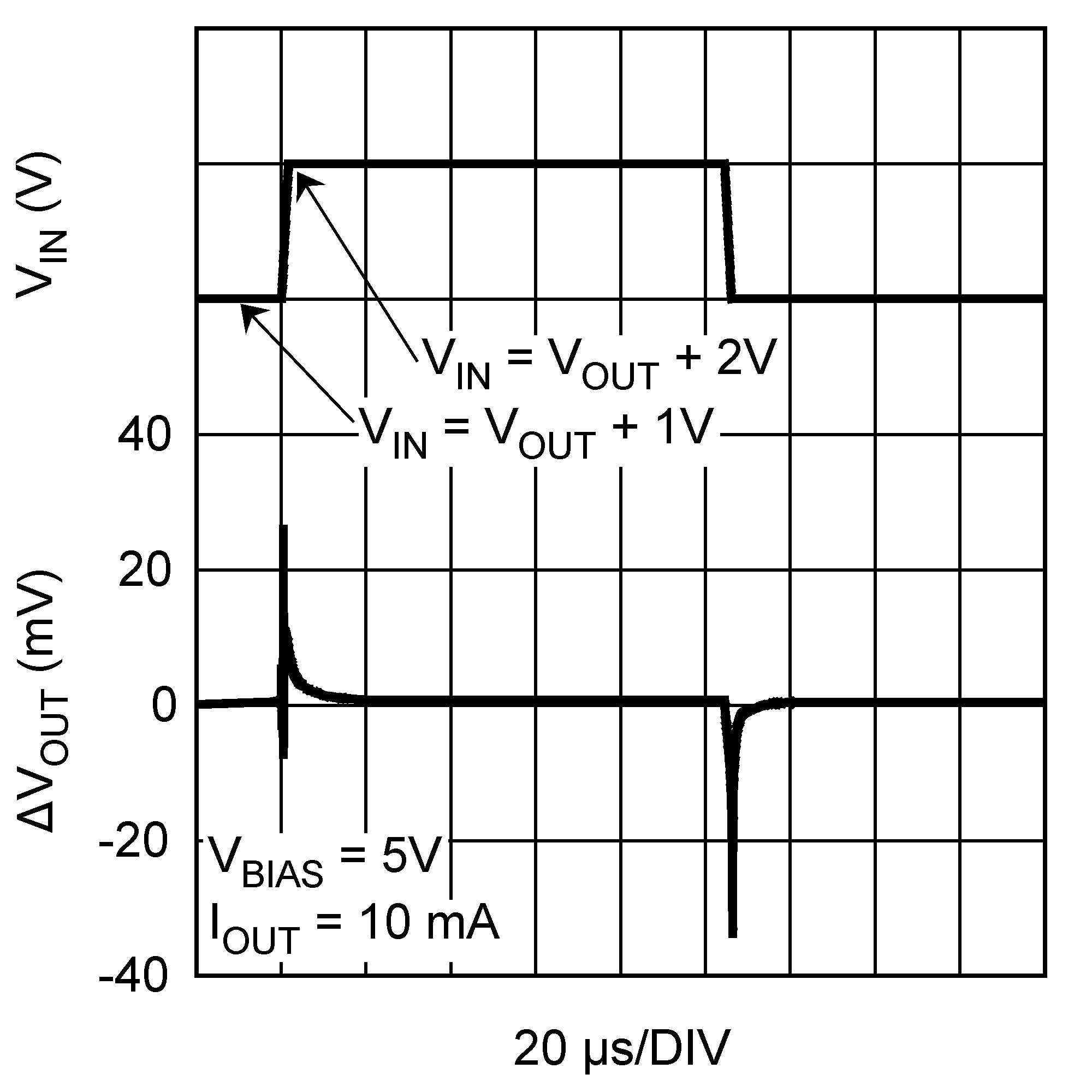

Figure 13. VIN Line Transient Response

Figure 13. VIN Line Transient Response

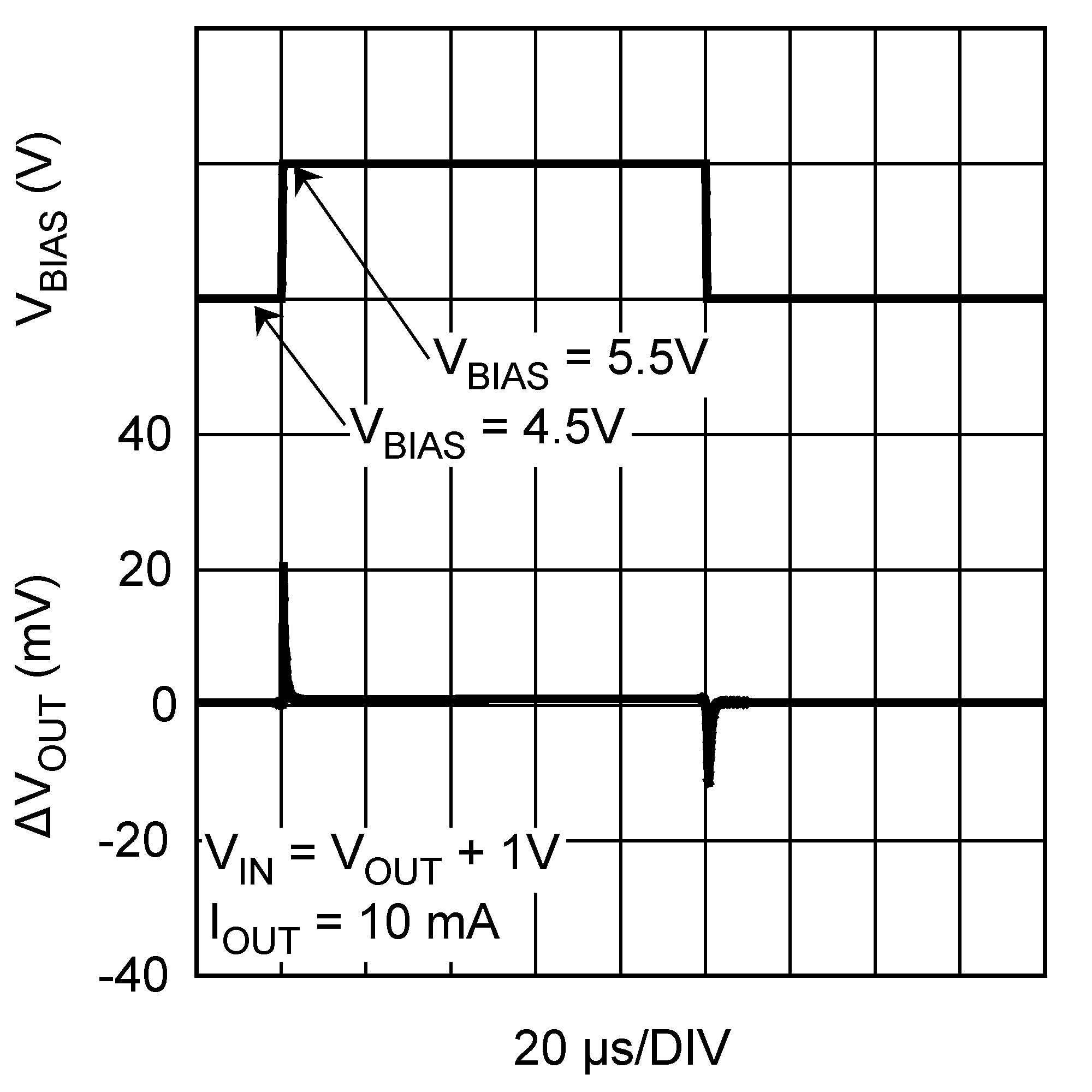

Figure 15. VBIAS Line Transient Response

Figure 15. VBIAS Line Transient Response

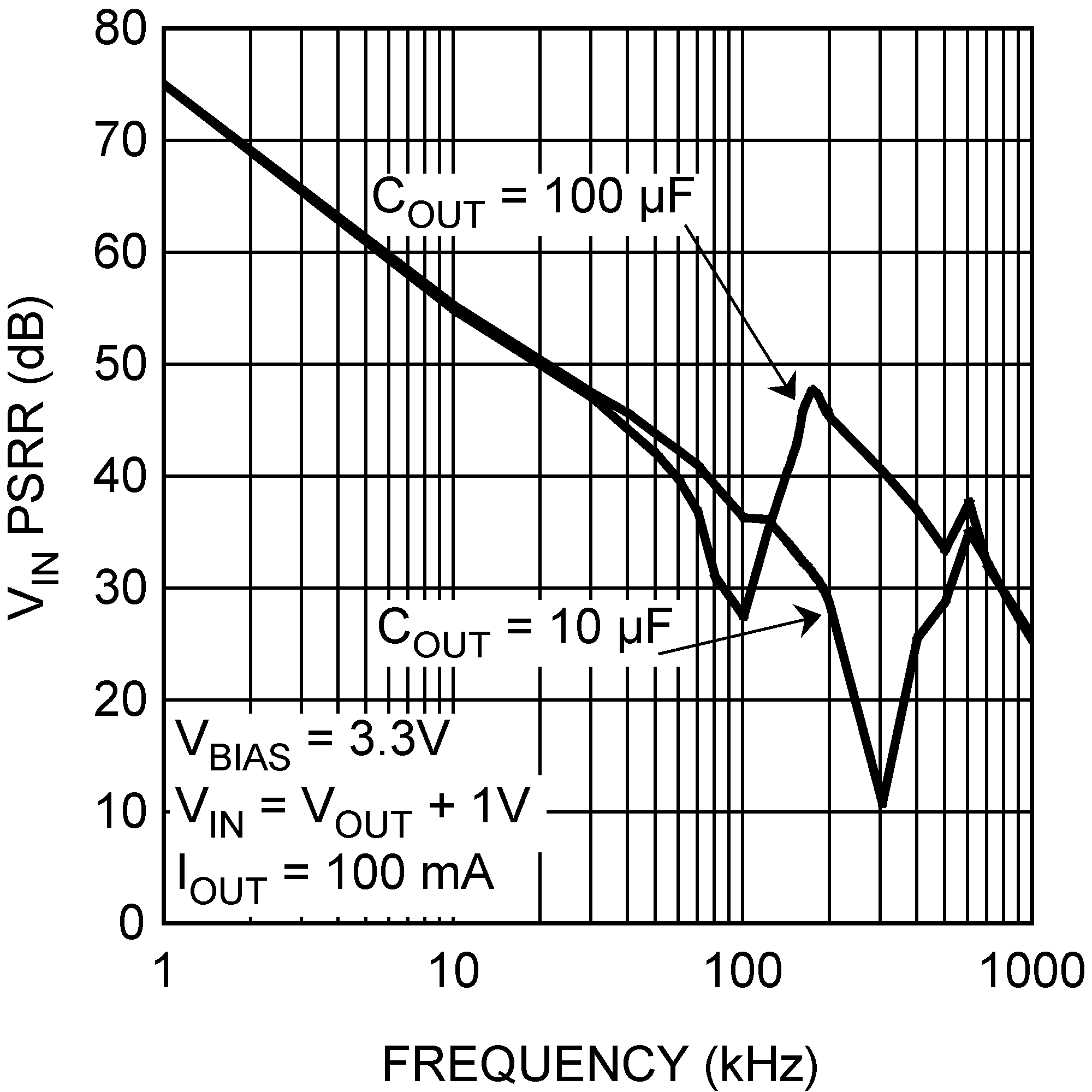

Figure 17. VIN PSRR

Figure 17. VIN PSRR

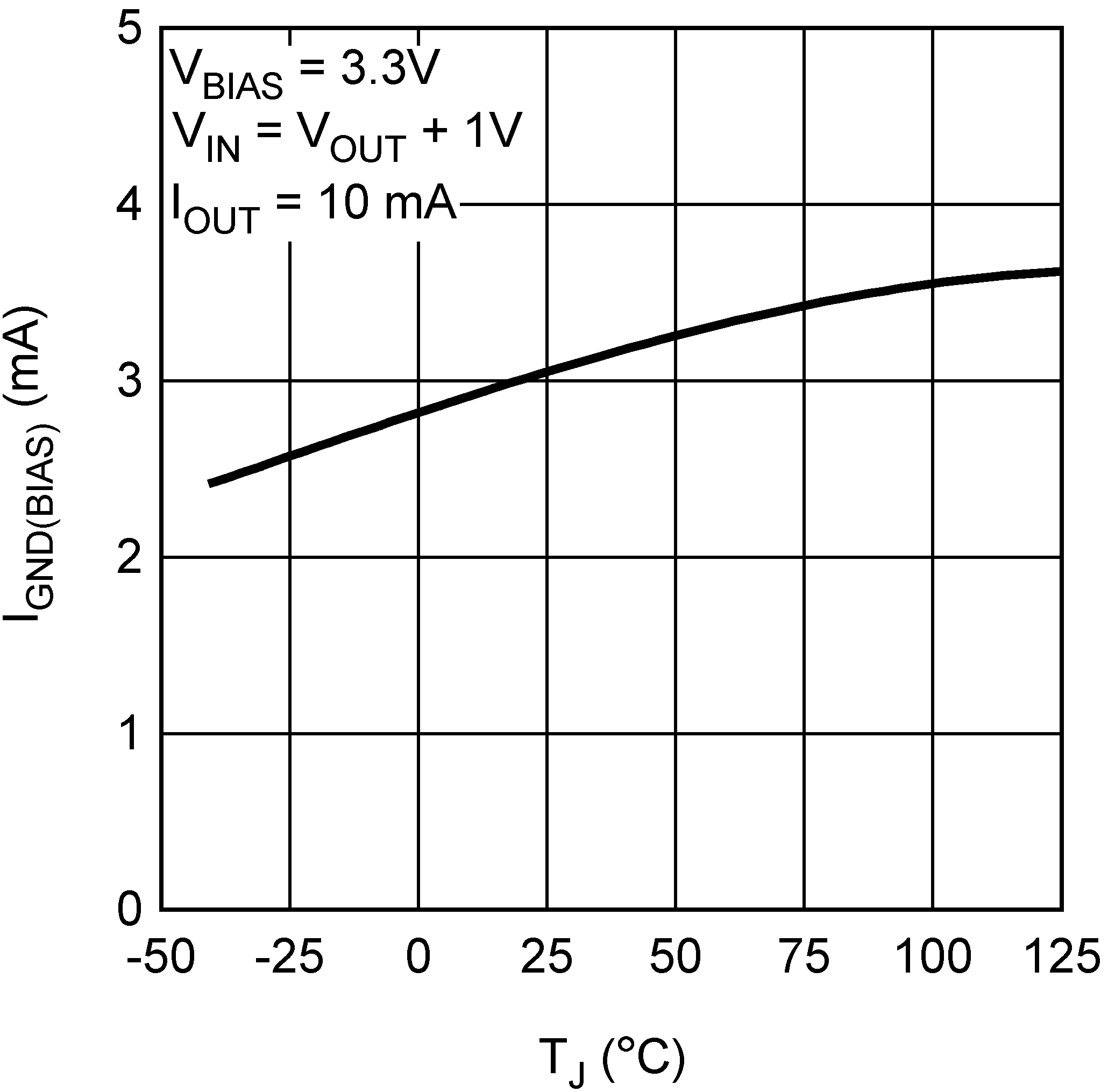

Figure 2. VBIAS Ground Pin Current (IGND(BIAS)) vs Temperature

Figure 2. VBIAS Ground Pin Current (IGND(BIAS)) vs Temperature

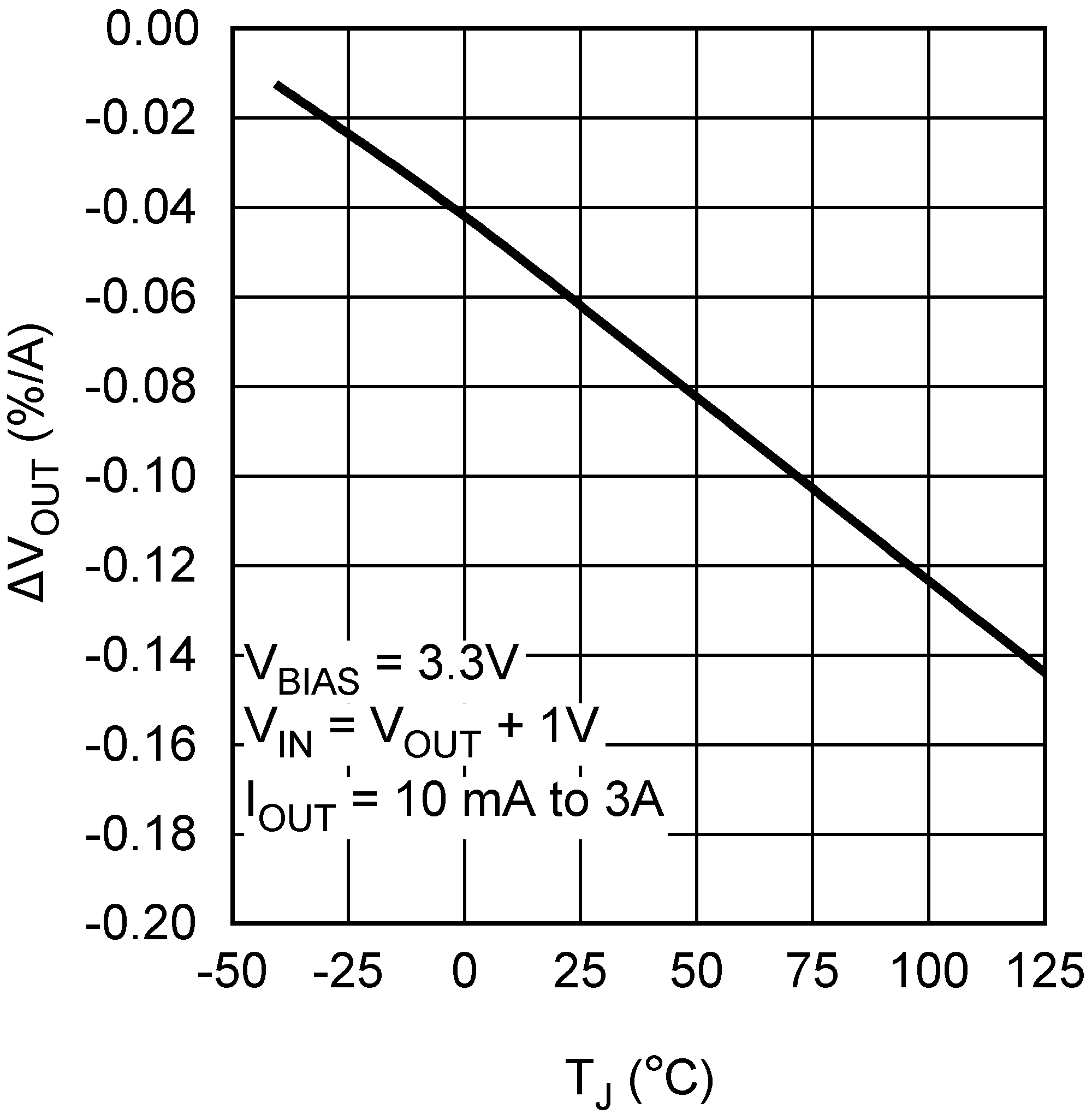

Figure 4. Load Regulation vs Temperature

Figure 4. Load Regulation vs Temperature

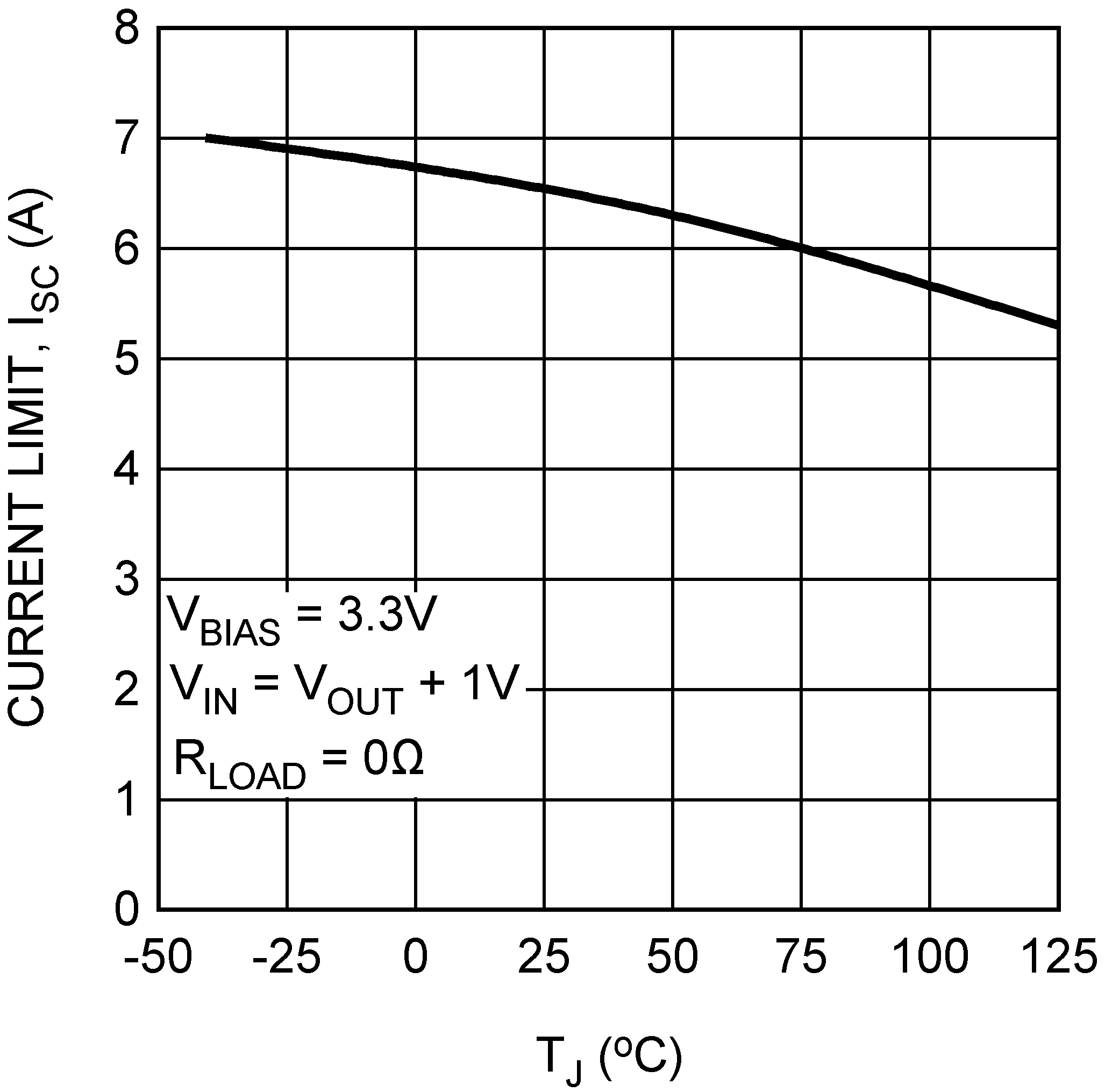

Figure 6. Output Current Limit (ISC) vs Temperature

Figure 6. Output Current Limit (ISC) vs Temperature

Figure 8. UVLO Thresholds vs Temperature

Figure 8. UVLO Thresholds vs Temperature

Figure 10. Soft-Start RSS Variation vs Temperature

Figure 10. Soft-Start RSS Variation vs Temperature

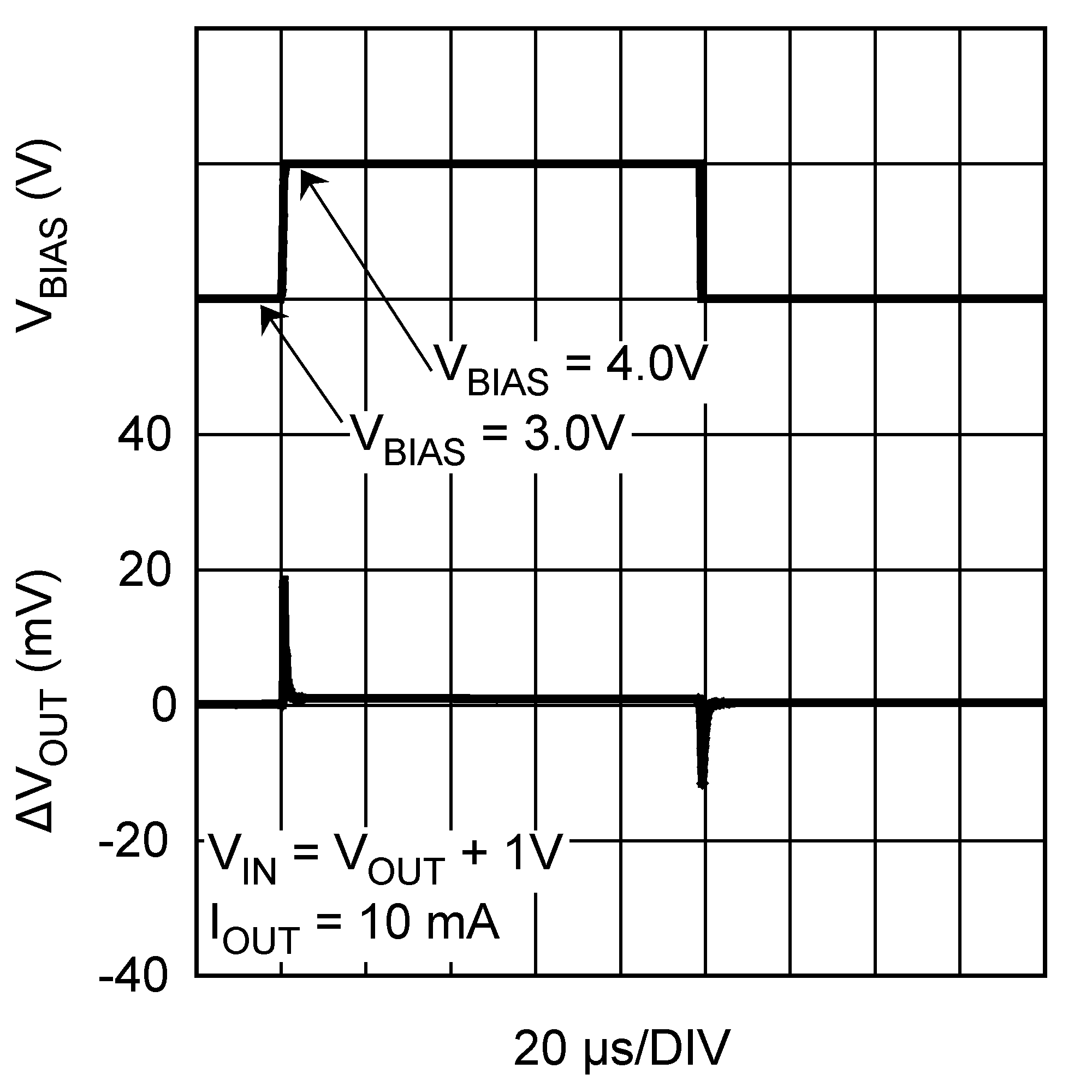

Figure 14. VBIAS Line Transient Response

Figure 14. VBIAS Line Transient Response

Figure 16. VBIAS PSRR

Figure 16. VBIAS PSRR

Figure 18. Output Noise

Figure 18. Output Noise