SNVS192C October 2002 – November 2015 LP3992

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Parameter Measurement Information

- 8 Detailed Description

- 9 Application And Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- DBV|5

Thermal pad, mechanical data (Package|Pins)

Orderable Information

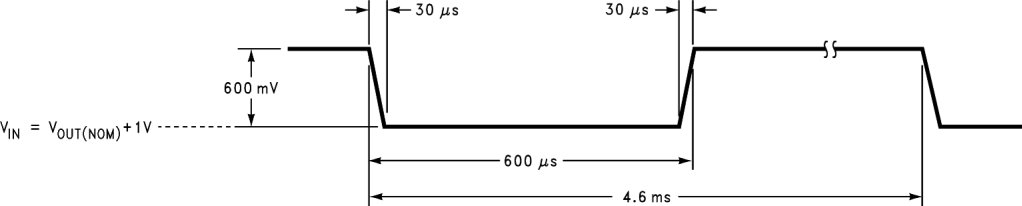

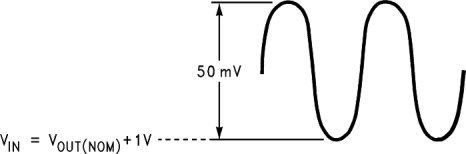

7 Parameter Measurement Information

7.1 Input Test Signals

Figure 13. Line Transient Input Test Signal

Figure 13. Line Transient Input Test Signal

Figure 14. PSRR Input Test Signal

Figure 14. PSRR Input Test Signal