SLOS670B November 2010 – December 2016 TAS5727

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Description (continued)

- 6 Device Comparison Table

- 7 Pin Configuration and Functions

-

8 Specifications

- 8.1 Absolute Maximum Ratings

- 8.2 ESD Ratings

- 8.3 Recommended Operating Conditions

- 8.4 Thermal Information

- 8.5 DC Electrical Characteristics

- 8.6 AC Electrical Characteristics (BTL, PBTL)

- 8.7 PLL Input Parameters and External Filter Components

- 8.8 Serial Audio Ports Slave Mode

- 8.9 I2C Serial Control Port Operation

- 8.10 Reset Timing (RESET)

- 8.11 Typical Characteristics

- 9 Parameter Measurement Information

-

10Detailed Description

- 10.1 Overview

- 10.2 Functional Block Diagrams

- 10.3

Feature Description

- 10.3.1 Power Supply

- 10.3.2 I2C Address Selection and Fault Output

- 10.3.3 Device Protection Systems

- 10.3.4 Clock, Auto Detection, and PLL

- 10.3.5 PWM Section

- 10.3.6 SSTIMER Functionality

- 10.3.7 Single-Filter PBTL Mode

- 10.3.8 I2C Serial Control Interface

- 10.3.9 Audio Serial Interface

- 10.3.10 Serial Interface Control and Timing

- 10.3.11 Dynamic Range Control (DRC)

- 10.3.12 PWM Level Meter

- 10.4 Device Functional Modes

- 10.5 Programming

- 10.6

Register Maps

- 10.6.1 Clock Control Register (0x00)

- 10.6.2 Device Id Register (0x01)

- 10.6.3 Error Status Register (0x02)

- 10.6.4 System Control Register 1 (0x03)

- 10.6.5 Serial Data Interface Register (0x04)

- 10.6.6 System Control Register 2 (0x05)

- 10.6.7 Soft Mute Register (0x06)

- 10.6.8 Volume Registers (0x07, 0x08, 0x09)

- 10.6.9 Volume Configuration Register (0x0E)

- 10.6.10 Modulation Limit Register (0x10)

- 10.6.11 Interchannel Delay Registers (0x11, 0x12, 0x13, and 0x14)

- 10.6.12 PWM Shutdown Group Register (0x19)

- 10.6.13 Start/Stop Period Register (0x1A)

- 10.6.14 Oscillator Trim Register (0x1B)

- 10.6.15 BKND_ERR Register (0x1C)

- 10.6.16 Input Multiplexer Register (0x20)

- 10.6.17 Channel 4 Source Select Register (0x21)

- 10.6.18 PWM Output MUX Register (0x25)

- 10.6.19 DRC Control Register (0x46)

- 10.6.20 PWM Switching Rate Control Register (0x4F)

- 10.6.21 Bank Switch and EQ Control (0x50)

-

11Application and Implementation

- 11.1 Application Information

- 11.2

Typical Applications

- 11.2.1 Stereo Stereo Bridge Tied Load Application

- 11.2.2 Mono Parallel Bridge Tied Load Application

- 12Power Supply Recommendations

- 13Layout

- 14Device and Documentation Support

- 15Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- PHP|48

Thermal pad, mechanical data (Package|Pins)

- PHP|48

Orderable Information

8 Specifications

8.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)| MIN | MAX | UNIT | ||

|---|---|---|---|---|

| Supply voltage | DVDD, AVDD | –0.3 | 3.6 | V |

| PVDD_x | –0.3 | 30 | V | |

| Input voltage | 3.3-V digital input | –0.5 | DVDD + 0.5 | V |

| 5-V tolerant(2) digital input (except MCLK) | –0.5 | DVDD + 2.5(4) | ||

| 5-V tolerant MCLK input | –0.5 | AVDD + 2.5(4) | ||

| OUT_x to PGND_x | 32(3) | V | ||

| BST_x to PGND_x | 43(3) | V | ||

| Input clamp current, IIK | ±20 | mA | ||

| Output clamp current, IOK | ±20 | mA | ||

| Operating free-air temperature | 0 | 85 | °C | |

| Operating junction temperature | 0 | 150 | °C | |

| Storage temperature, Tstg | –40 | 125 | °C | |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum conditions for extended periods may affect device reliability.

(2) 5-V tolerant inputs are PDN, RESET, SCLK, LRCLK, MCLK, SDIN, SDA, and SCL.

(3) DC voltage + peak ac waveform measured at the pin should be below the allowed limit for all conditions.

(4) Maximum pin voltage should not exceed 6 V.

8.2 ESD Ratings

| VALUE | UNIT | |||

|---|---|---|---|---|

| V(ESD) | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001(1) | ±1000 | V |

| Charged-device model (CDM), per JEDEC specification JESD22-C101(2) | ±250 | |||

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

8.3 Recommended Operating Conditions

| MIN | NOM | MAX | UNIT | |||

|---|---|---|---|---|---|---|

| Digital/analog supply voltage | DVDD, AVDD | 3 | 3.3 | 3.6 | V | |

| Half-bridge supply voltage | PVDD_x (1) | 8 | 26 | V | ||

| VIH | High-level input voltage | 5-V tolerant | 2 | V | ||

| VIL | Low-level input voltage | 5-V tolerant | 0.8 | V | ||

| TA | Operating ambient temperature | 0 | 85 | °C | ||

| TJ(2) | Operating junction temperature | 0 | 125 | °C | ||

| RL (BTL) | Load impedance | Output filter: L = 15 μH, C = 680 nF | 4 | 8 | Ω | |

| RL (PBTL) | Load impedance | Output filter: L = 15 μH, C = 680 nF | 2 | 4 | Ω | |

| LO (BTL) | Output-filter inductance | Minimum output inductance under short-circuit condition | 10 | μH | ||

| Output sample rate | 11.025/22.05/44.1-kHz data rate ±2% | 288 | kHz | |||

| 48/24/12/8/16/32-kHz data rate ±2% | 384 | |||||

(1) For operation at PVDD_x levels greater than 18 V, the modulation limit must be set to 93.8% through the control port register 0x10.

(2) Continuous operation above the recommended junction temperature may result in reduced reliability and/or lifetime of the device.

8.4 Thermal Information

| THERMAL METRIC(1) | TAS5727 | UNIT | |

|---|---|---|---|

| PHP (HTQFP) | |||

| 48 PINS | |||

| RθJA | Junction-to-ambient thermal resistance | 27.9 | °C/W |

| RθJC(top) | Junction-to-case (top) thermal resistance | 13 | °C/W |

| RθJB | Junction-to-board thermal resistance | 1.1 | °C/W |

| ψJT | Junction-to-top characterization parameter | 20.7 | °C/W |

| ψJB | Junction-to-board characterization parameter | 0.3 | °C/W |

| RθJC(bot) | Junction-to-case (bottom) thermal resistance | 6.7 | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

8.5 DC Electrical Characteristics

TA = 25°, PVCC_x = 18 V, DVDD = AVDD = 3.3 V, RL= 8 Ω, BTL AD mode, fS = 48 kHz (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | ||

|---|---|---|---|---|---|---|---|

| VOH | High-level output voltage | A_SEL_FAULT and SDA | IOH = –4 mA DVDD = 3 V |

2.4 | V | ||

| VOL | Low-level output voltage | A_SEL_FAULT and SDA | IOL = 4 mA DVDD = 3 V |

0.5 | V | ||

| IIL | Low-level input current | VI < VIL ; DVDD = AVDD = 3.6 V |

75 | μA | |||

| IIH | High-level input current | VI > VIH ; DVDD = AVDD = 3.6 V |

75(3) | μA | |||

| IDD | 3.3-V supply current | 3.3-V supply voltage (DVDD, AVDD) | Normal mode | 49 | 68 | mA | |

| Reset (RESET = low, PDN = high) | 23 | 38 | |||||

| IPVDD | Supply current | No load (PVDD_x) | Normal mode | 32 | 50 | mA | |

| Reset (RESET = low, PDN = high) | 3 | 8 | |||||

| rDS(on) (2) | Drain-to-source resistance, LS | TJ = 25°C, includes metallization resistance | 75 | mΩ | |||

| Drain-to-source resistance, HS | TJ = 25°C, includes metallization resistance | 75 | |||||

| I/O Protection | |||||||

| Vuvp | Undervoltage protection limit | PVDD falling | 7.2 | V | |||

| Vuvp,hyst | Undervoltage protection limit | PVDD rising | 7.6 | V | |||

| OTE(1) | Overtemperature error | 150 | °C | ||||

| OTEHYST (1) | Extra temperature drop required to recover from error | 30 | °C | ||||

| IOC | Overcurrent limit protection | 4.5 | A | ||||

| IOCT | Overcurrent response time | 150 | ns | ||||

| RPD | Internal pulldown resistor at the output of each half-bridge | Connected when drivers are in the high-impedance state to provide bootstrap capacitor charge. | 3 | kΩ | |||

(1) Specified by design

(2) This does not include bond-wire or pin resistance.

(3) IIH for the PBTL pin has a maximum limit of 200 µA due to an internal pulldown on the pin.

8.6 AC Electrical Characteristics (BTL, PBTL)

PVDD_x = 18 V, BTL AD mode, fS = 48 KHz, RL = 8 Ω, ROCP = 22 kΩ, CBST = 33 nF, audio frequency = 1 kHz, AES17 filter,fPWM = 384 kHz, TA = 25°C (unless otherwise specified). All performance is in accordance with recommended operating conditions (unless otherwise specified).

| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| PO | Power output per channel | PVDD = 18 V,10% THD, 1-kHz input signal | 21.5 | W | ||

| PVDD = 18 V, 7% THD, 1-kHz input signal | 20.3 | |||||

| PVDD = 12 V, 10% THD, 1-kHz input signal | 9.6 | |||||

| PVDD = 12 V, 7% THD, 1-kHz input signal | 9.1 | |||||

| PVDD = 8 V, 10% THD, 1-kHz input signal | 4.2 | |||||

| PVDD = 8 V, 7% THD, 1-kHz input signal | 4 | |||||

| PBTL mode, PVDD = 12 V, RL = 4 Ω, 10% THD, 1-kHz input signal |

18.7 | |||||

| PBTL mode, PVDD = 12 V, RL = 4 Ω, 7% THD, 1-kHz input signal |

17.7 | |||||

| PBTL mode, PVDD = 18 V, RL = 4 Ω, 10% THD, 1-kHz input signal |

41.5 | |||||

| PBTL mode, PVDD = 18 V, RL = 4 Ω, 7% THD, 1-kHz input signal |

39 | |||||

| THD+N | Total harmonic distortion + noise | PVDD = 18 V, PO = 1 W | 0.07% | |||

| PVDD = 12 V, PO = 1 W | 0.03% | |||||

| PVDD = 8 V, PO = 1 W | 0.1% | |||||

| Vn | Output integrated noise (rms) | A-weighted | 56 | μV | ||

| Crosstalk | PO = 0.25 W, f = 1 kHz (BD Mode) | –82 | dB | |||

| PO = 0.25 W, f = 1 kHz (AD Mode) | –69 | dB | ||||

| SNR | Signal-to-noise ratio(1) | A-weighted, f = 1 kHz, maximum power at THD < 1% | 106 | dB | ||

(1) SNR is calculated relative to 0-dBFS input level.

8.7 PLL Input Parameters and External Filter Components

| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| fMCLKI | MCLK frequency | 2.8224 | 24.576 | MHz | ||

| MCLK duty cycle | 40% | 50% | 60% | |||

| tr / tf(MCLK) | Rise/fall time for MCLK | 5 | ns | |||

| LRCLK allowable drift before LRCLK reset | 4 | MCLKs | ||||

| External PLL filter capacitor C1 | SMD 0603 X7R | 47 | nF | |||

| External PLL filter capacitor C2 | SMD 0603 X7R | 4.7 | nF | |||

| External PLL filter resistor R | SMD 0603, metal film | 470 | Ω | |||

8.8 Serial Audio Ports Slave Mode

over recommended operating conditions (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | NOM | MAX | UNIT | |

|---|---|---|---|---|---|---|

| fSCLKIN | Frequency, SCLK 32 × fS, 48 × fS, 64 × fS | CL = 30 pF | 1.024 | 12.288 | MHz | |

| tsu1 | Setup time, LRCLK to SCLK rising edge | 10 | ns | |||

| th1 | Hold time, LRCLK from SCLK rising edge | 10 | ns | |||

| tsu2 | Setup time, SDIN to SCLK rising edge | 10 | ns | |||

| th2 | Hold time, SDIN from SCLK rising edge | 10 | ns | |||

| LRCLK frequency | 8 | 48 | 48 | kHz | ||

| SCLK duty cycle | 40% | 50% | 60% | |||

| LRCLK duty cycle | 40% | 50% | 60% | |||

| SCLK rising edges between LRCLK rising edges | 32 | 64 | SCLK edges | |||

| t(edge) | LRCLK clock edge with respect to the falling edge of SCLK | –1/4 | 1/4 | SCLK period | ||

| tr/tf | Rise/fall time for SCLK/LRCLK | 8 | ns | |||

8.9 I2C Serial Control Port Operation

Timing characteristics for I2C Interface signals over recommended operating conditions (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | MAX | UNIT | |

|---|---|---|---|---|---|

| fSCL | Frequency, SCL | No wait states | 400 | kHz | |

| tw(H) | Pulse duration, SCL high | 0.6 | μs | ||

| tw(L) | Pulse duration, SCL low | 1.3 | μs | ||

| tr | Rise time, SCL and SDA | 300 | ns | ||

| tf | Fall time, SCL and SDA | 300 | ns | ||

| tsu1 | Setup time, SDA to SCL | 100 | ns | ||

| th1 | Hold time, SCL to SDA | 0 | ns | ||

| t(buf) | Bus free time between stop and start conditions | 1.3 | μs | ||

| tsu2 | Setup time, SCL to start condition | 0.6 | μs | ||

| th2 | Hold time, start condition to SCL | 0.6 | μs | ||

| tsu3 | Setup time, SCL to stop condition | 0.6 | μs | ||

| CL | Load capacitance for each bus line | 400 | pF | ||

8.10 Reset Timing (RESET)

Control signal parameters over recommended operating conditions (unless otherwise noted). Please refer to Recommended Use Model section on usage of all terminals.| PARAMETER | MIN | NOM | MAX | UNIT | |

|---|---|---|---|---|---|

| tw(RESET) | Pulse duration, RESET active | 100 | μs | ||

| td(I2C_ready) | Time to enable I2C | 12 | ms | ||

Figure 1. Slave-Mode Serial Data-Interface Timing

Figure 1. Slave-Mode Serial Data-Interface Timing

Figure 2. SCL and SDA Timing

Figure 2. SCL and SDA Timing

Figure 3. Start and Stop Conditions Timing

Figure 3. Start and Stop Conditions Timing

NOTES:

On power up, TI recommends that the TAS5727 RESET be held LOW for at least 100 μs after DVDD has reached 3 V.If RESET is asserted LOW while PDN is LOW, then RESET must continue to be held LOW for at least 100 μs after PDN is deasserted (HIGH).

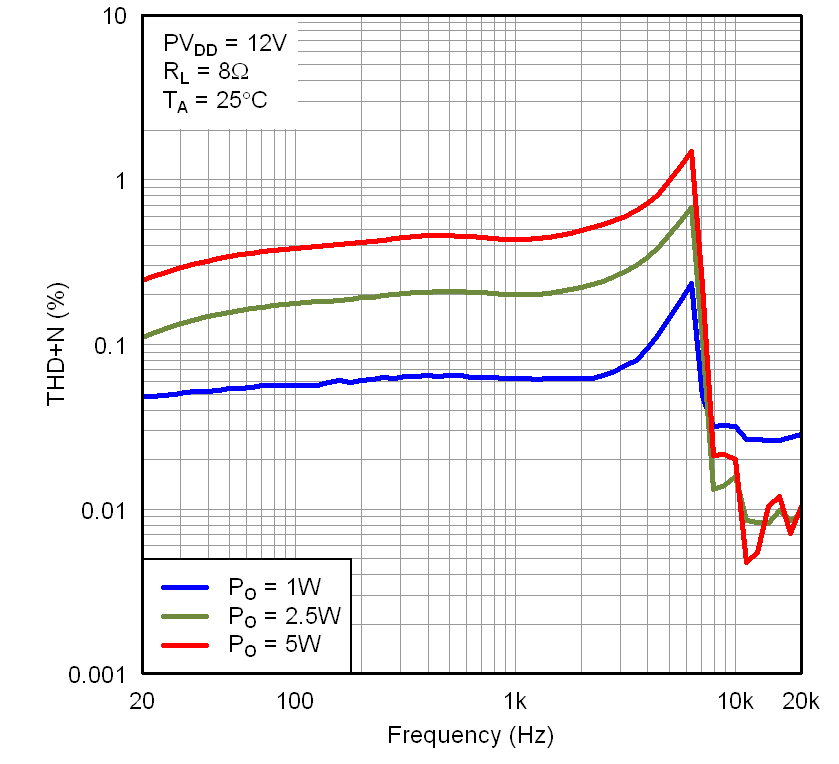

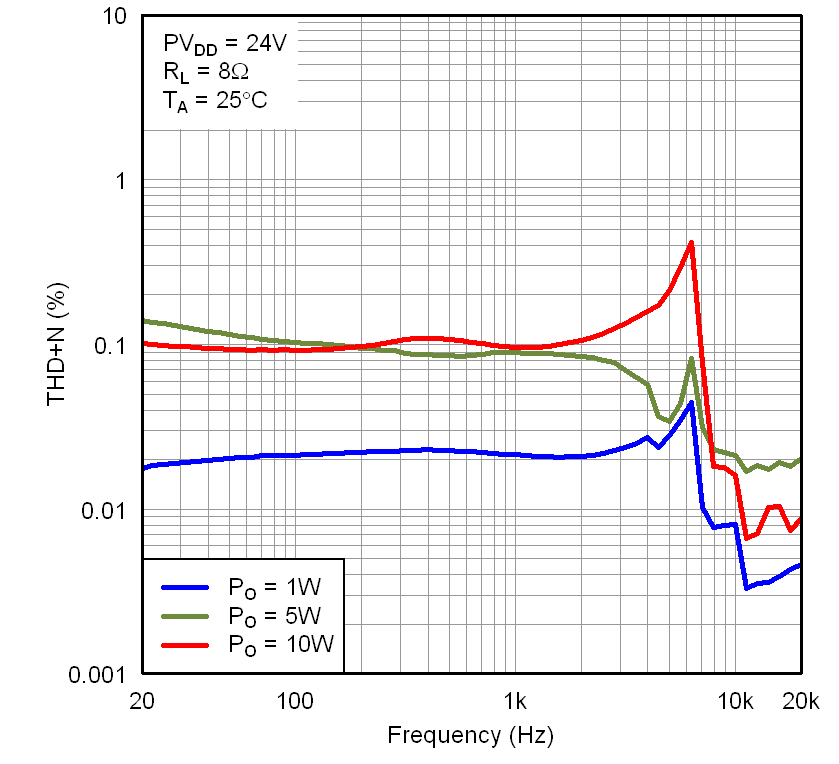

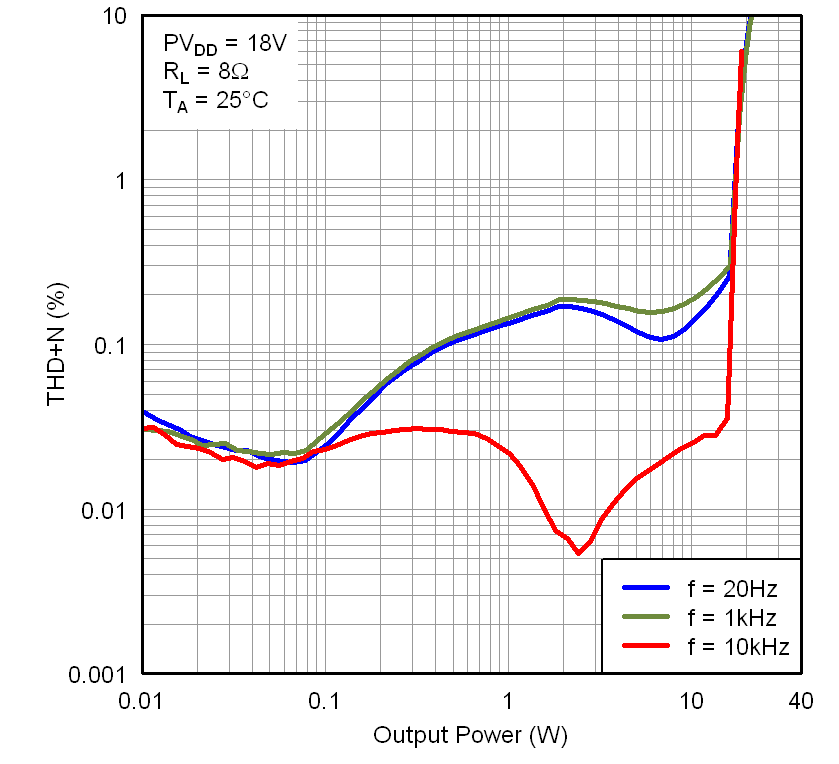

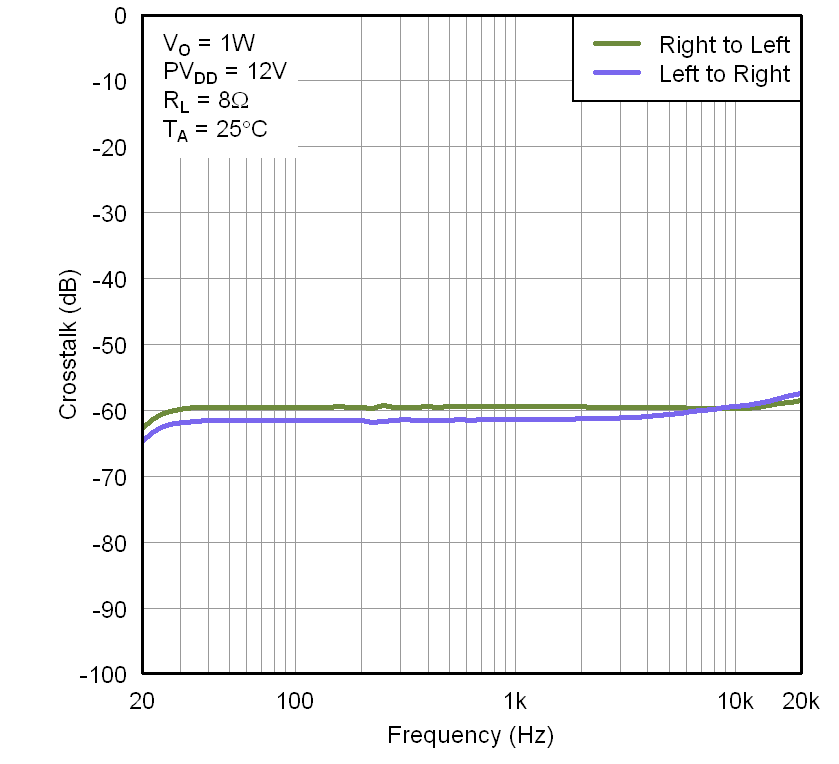

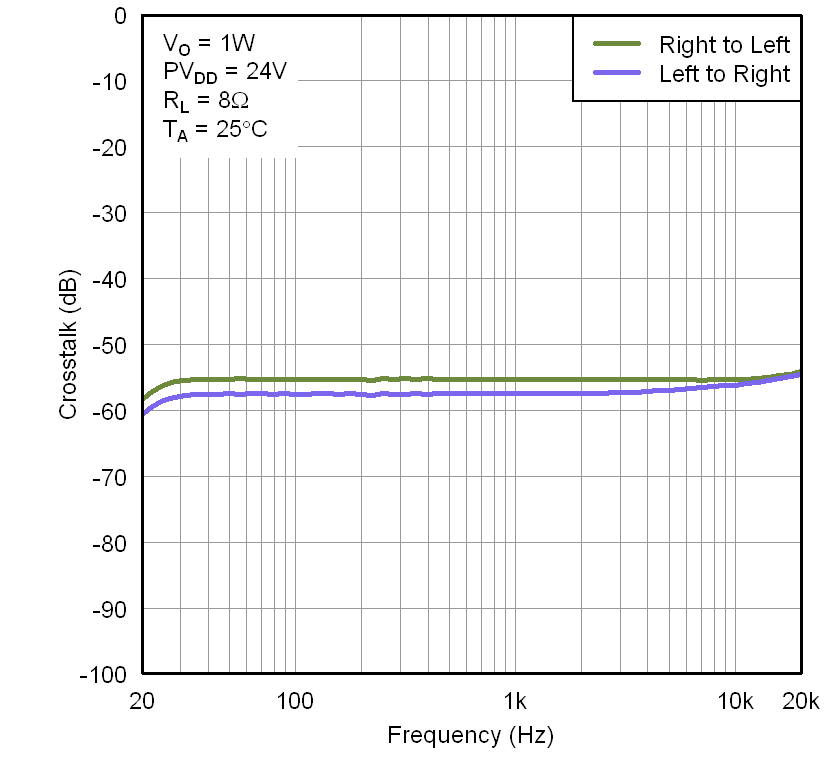

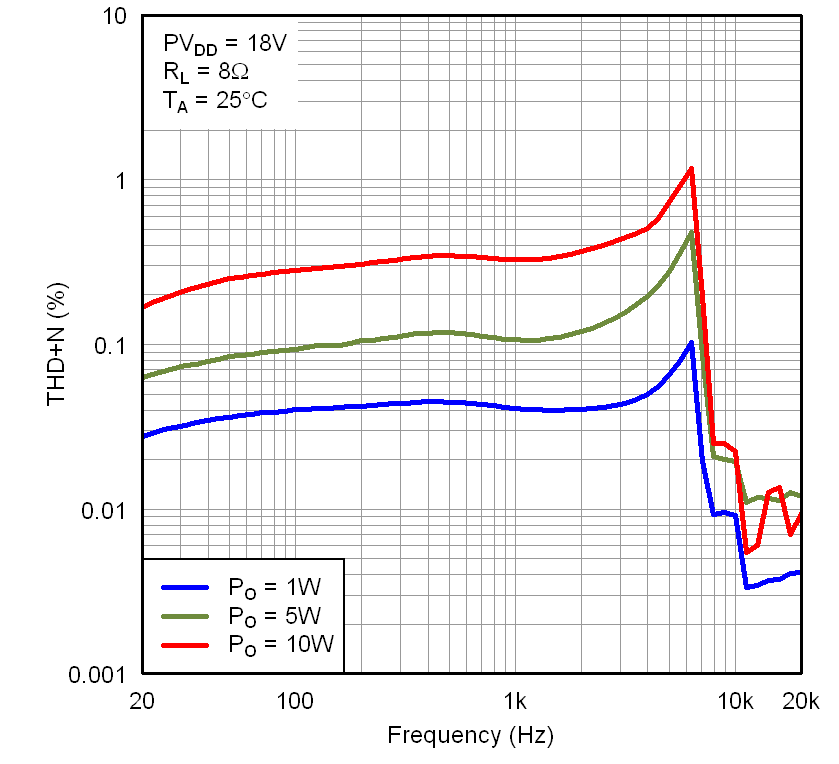

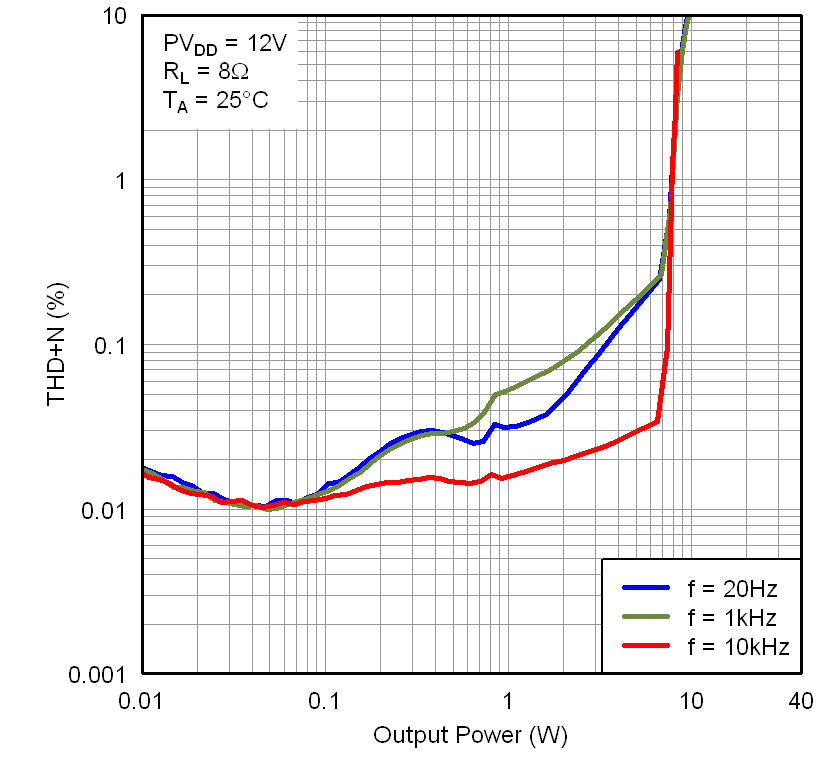

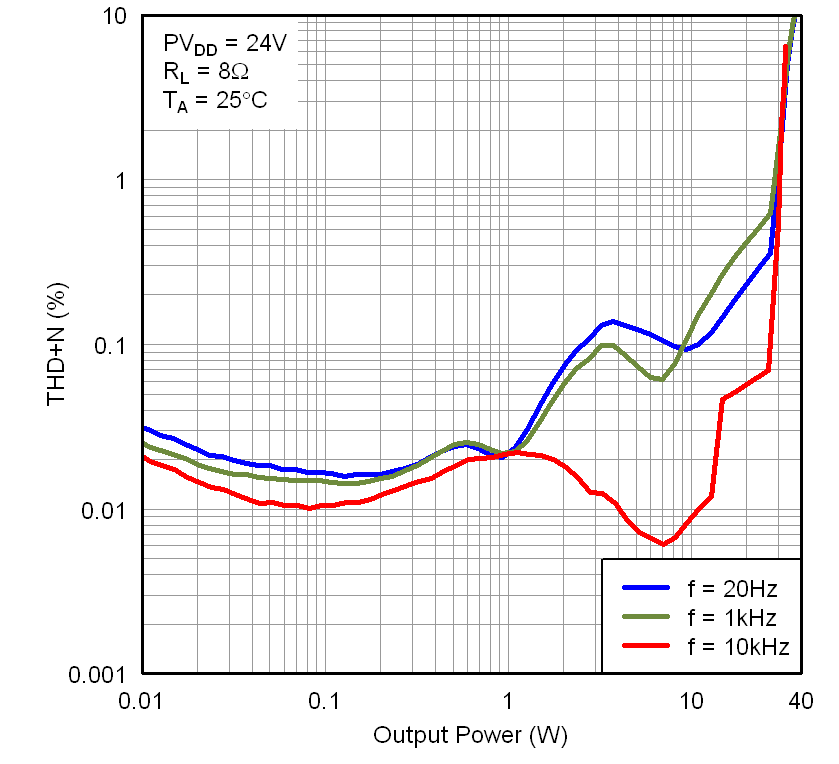

8.11 Typical Characteristics

BTL Configuration, 8 Ω Figure 5. Total Harmonic Distortion + Noise vs Frequency

Figure 5. Total Harmonic Distortion + Noise vs Frequency

Figure 7. Total Harmonic Distortion + Noise vs Frequency

Figure 7. Total Harmonic Distortion + Noise vs Frequency

Figure 9. Total Harmonic Distortion + Noise vs Output Power

Figure 9. Total Harmonic Distortion + Noise vs Output Power

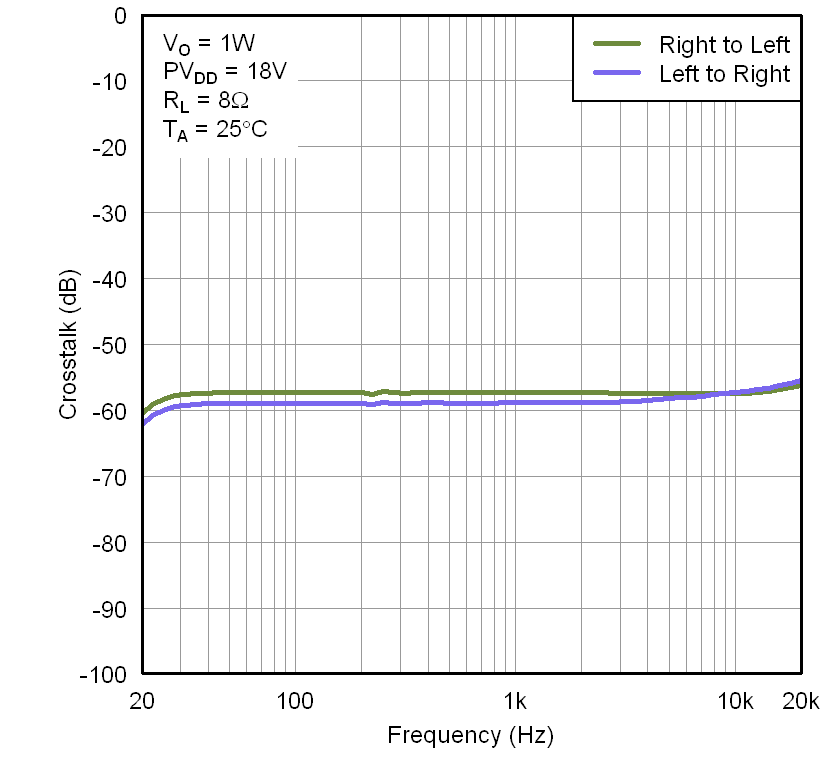

Figure 11. Crosstalk vs Frequency

Figure 11. Crosstalk vs Frequency

Figure 13. Crosstalk vs Frequency

Figure 13. Crosstalk vs Frequency

Figure 6. Total Harmonic Distortion + Noise vs Frequency

Figure 6. Total Harmonic Distortion + Noise vs Frequency

Figure 8. Total Harmonic Distortion + Noise vs Output Power

Figure 8. Total Harmonic Distortion + Noise vs Output Power

Figure 10. Total Harmonic Distortion + Noise vs Output Power

Figure 10. Total Harmonic Distortion + Noise vs Output Power

Figure 12. Crosstalk vs Frequency

Figure 12. Crosstalk vs Frequency

Dashed lines represent thermally limited region.

Figure 14. Efficiency vs Total Output Power