JAJSGP9G October 2011 – August 2023 BQ25504

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Revision History

- 5 概要 (続き)

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Detailed Description

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

- RGT|16

サーマルパッド・メカニカル・データ

- RGT|16

発注情報

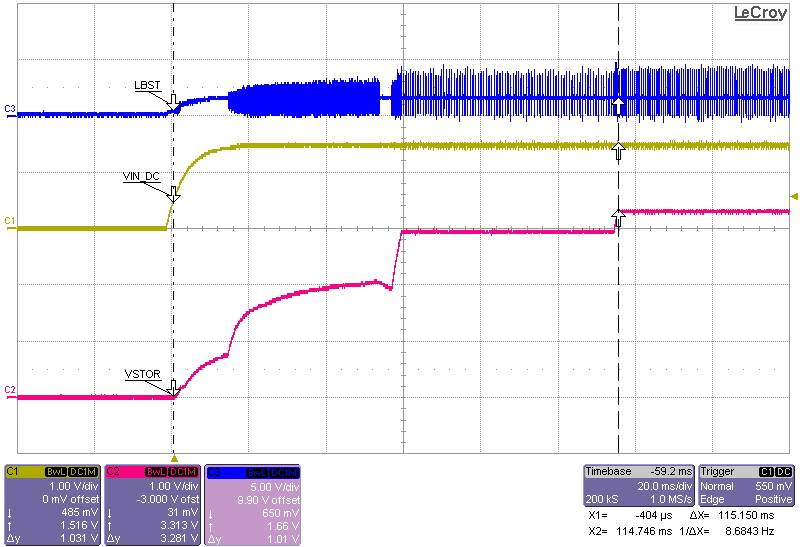

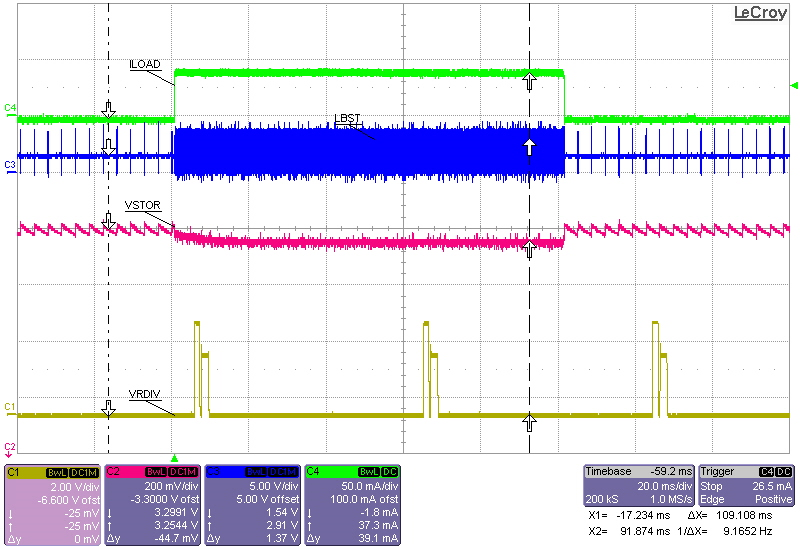

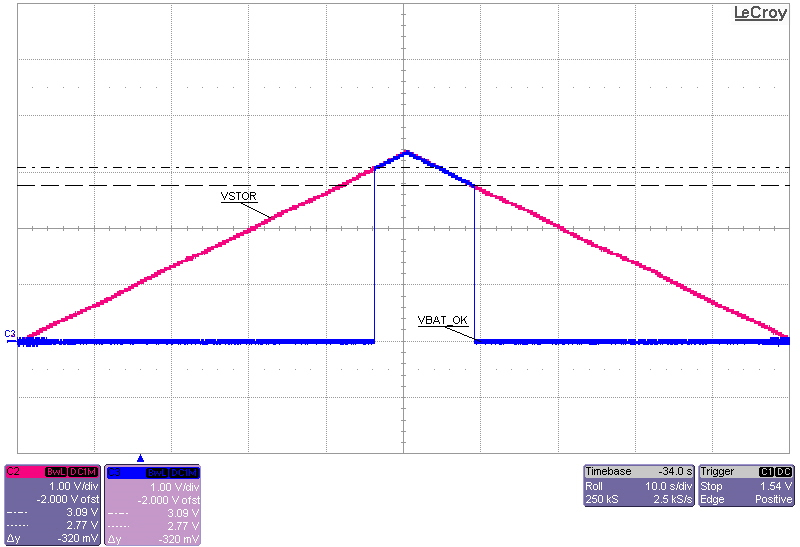

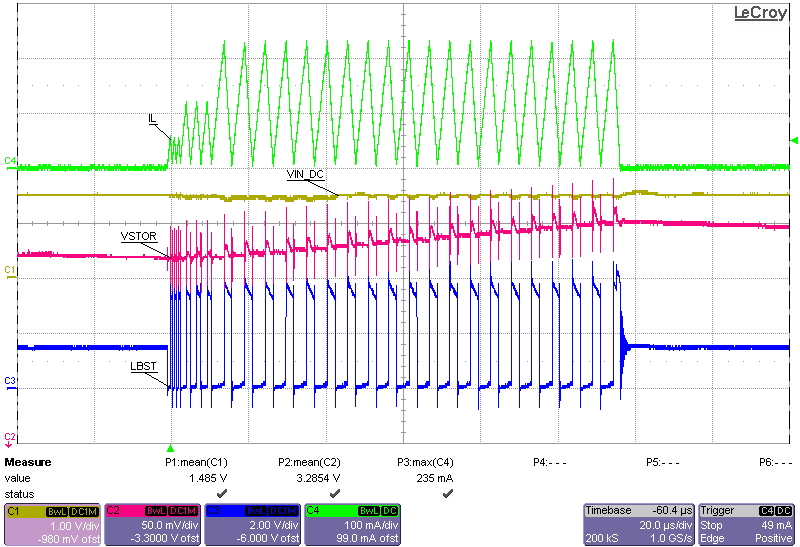

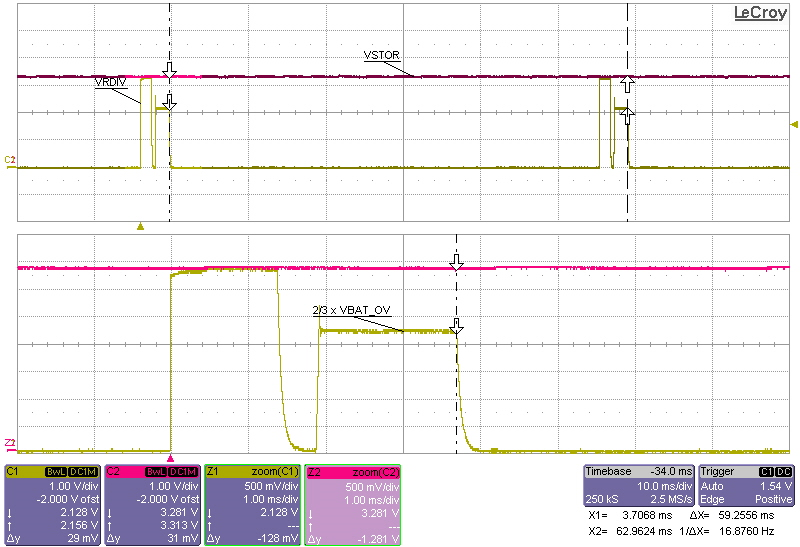

9.2.3.3 Application Curves

| VIN_DC = low impedance voltage source = 1.5 V | ||

| VBAT = VSTOR = 100 µF | ||

| VSTOR = 500 Ω resistor |

| VIN_DC = low impedance voltage source = 1.5 V ) | ||

| VBAT = VSTOR = 100 µF | ||

| VSTOR = open to 75 Ω to open resistive load (IL = load current on VSTOR |

| VIN_DC = low impedance voltage source = 1.5 V | ||

| VBAT = VSTOR = 100 µF | ||

| VSTOR artificially ramped from 0 V to 3.3 V to 0 V using a power amp driven by a function generator |

| VIN_DC = low impedance voltage source = 1.5 V | ||

| VBAT = VSTOR = 100 µF | ||

| VSTOR = 330 Ω resistive load (IL = inductor current) |

| VIN_DC = low impedance voltage source = 1.5 V | ||

| VBAT = VSTOR = 100 µF | ||