JAJSGI8D April 2016 – October 2019 DS90UB914A-Q1

PRODUCTION DATA.

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 概要(続き)

- 6 Device Comparison Table

- 7 Pin Configuration and Functions

-

8 Specifications

- 8.1 Absolute Maximum Ratings

- 8.2 ESD Ratings

- 8.3 Recommended Operating Conditions

- 8.4 Thermal Information

- 8.5 Electrical Characteristics

- 8.6 AC Timing Specifications (SCL, SDA) - I2C-Compatible

- 8.7 Bidirectional Control Bus DC Timing Specifications (SCL, SDA) - I2C-Compatible

- 8.8 Deserializer Switching Characteristics

- 8.9 Typical Characteristics

- 9 Parameter Measurement Information

-

10Detailed Description

- 10.1 Overview

- 10.2 Functional Block Diagram

- 10.3

Feature Description

- 10.3.1 Serial Frame Format

- 10.3.2 Line Rate Calculations for the DS90UB913A/914A

- 10.3.3 Deserializer Multiplexer Input

- 10.3.4 Error Detection

- 10.3.5 Synchronizing Multiple Cameras

- 10.3.6 General-Purpose I/O (GPIO) Descriptions

- 10.3.7 LVCMOS VDDIO Option

- 10.3.8 EMI Reduction

- 10.3.9 Pixel Clock Edge Select (TRFB / RRFB)

- 10.3.10 Power Down

- 10.4

Device Functional Modes

- 10.4.1 DS90UB913A/914A Operation With External Oscillator as Reference Clock

- 10.4.2 DS90UB913A/914A Operation With Pixel Clock From Imager as Reference Clock

- 10.4.3 MODE Pin on Deserializer

- 10.4.4 Clock-Data Recovery Status Flag (LOCK), Output Enable (OEN) and Output State Select (OSS_SEL)

- 10.4.5 Built-In Self Test

- 10.4.6 BIST Configuration and Status

- 10.4.7 Sample BIST Sequence

- 10.5 Programming

- 10.6 Register Maps

- 11Application and Implementation

- 12Power Supply Recommendations

- 13Layout

- 14デバイスおよびドキュメントのサポート

- 15メカニカル、パッケージ、および注文情報

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

- RHS|48

サーマルパッド・メカニカル・データ

- RHS|48

発注情報

13.2 Layout Example

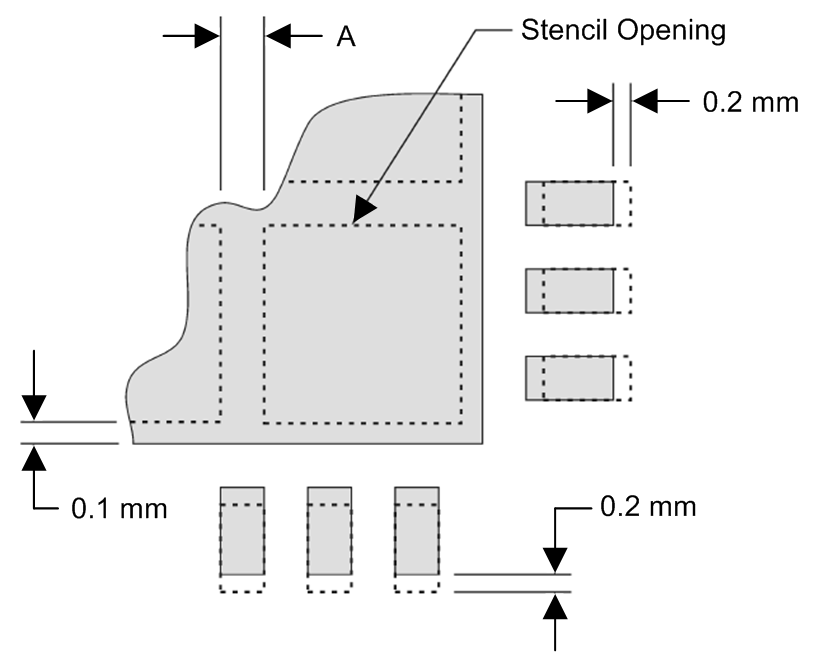

Stencil parameters such as aperture area ratio and the fabrication process have a significant impact on paste deposition. Inspection of the stencil prior to placement of the WQFN package is highly recommended to improve board assembly yields. If the via and aperture openings are not carefully monitored, the solder may flow unevenly through the DAP. Stencil parameters for aperture opening and via locations are shown below:

Figure 41. No Pullback WQFN, Single Row Reference Diagram

Figure 41. No Pullback WQFN, Single Row Reference Diagram Table 13. No Pullback WQFN Stencil Aperture Summary for DS90UB914A-Q1

| DEVICE | PIN COUNT | MKT DWG | PCB I/O PAD SIZE (mm) | PCB PITCH (mm) | PCB DAP SIZE(mm) | STENCIL I/O APERTURE (mm) | STENCIL DAP APERTURE (mm) | NUMBER OF DAP APERTURE OPENINGS | GAP BETWEEN DAP APERTURE (Dim A mm) |

|---|---|---|---|---|---|---|---|---|---|

| DS90UB914A-Q1 | 48 | RHS | 0.25 x 0.6 | 0.5 | 5.1 x 5.1 | 0.25 x 0.7 | 1.1 x 1.1 | 16 | 0.2 |

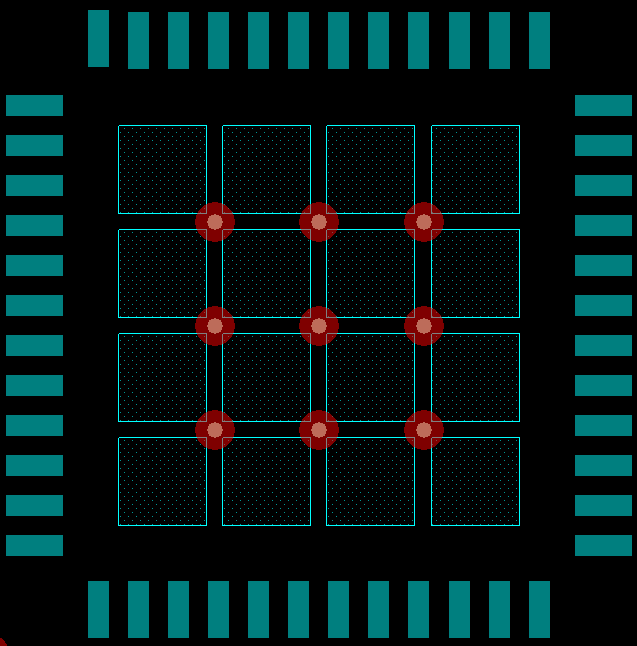

Figure 42. 48-Pin WQFN Stencil Example of Via and Opening Placement

Figure 42. 48-Pin WQFN Stencil Example of Via and Opening Placement The following PCB layout examples are derived from the layout design of the DS90UB914A-Q1 Evaluation Module (see DS90UB913A-CXEVM and DS90UB914A-CXEVM User’s Guide (SNLU135)). These graphics and additional layout description are used to demonstrate both proper routing and proper solder techniques when designing in this Deserializer.