JAJSHP2D December 2015 – August 2021 OPA191 , OPA2191 , OPA4191

PRODUCTION DATA

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 ピン構成および機能

- 6 仕様

- 7 パラメータ測定情報

- 8 詳細説明

- 9 アプリケーションと実装

- 10電源に関する推奨事項

- 11レイアウト

- 12デバイスおよびドキュメントのサポート

- 13メカニカル、パッケージ、および注文情報

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

サーマルパッド・メカニカル・データ

発注情報

6.9 代表的特性

TA = 25℃、VS = ±18V、VCM = VS/2、RL = 10kΩ を VS/2 に接続、CL = 100pF (特に記述のない限り)

表 6-1 グラフ一覧

| 説明 | 図 |

|---|---|

| オフセット電圧の製品分布 | 図 6-1、図 6-2、図 6-3、図 6-4、図 6-5、図 6-6 |

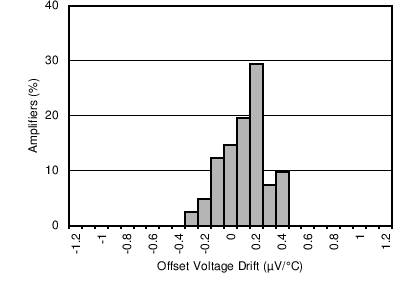

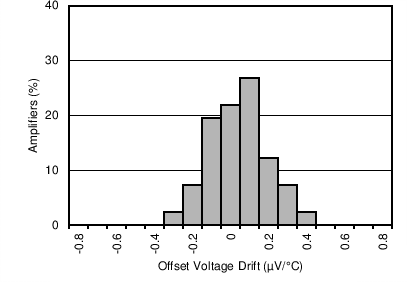

| オフセット電圧ドリフトの分布 | 図 6-7、図 6-8 |

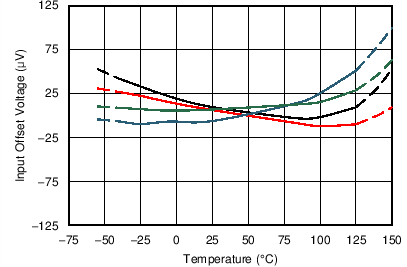

| オフセット電圧と温度との関係 | 図 6-9、図 6-10 |

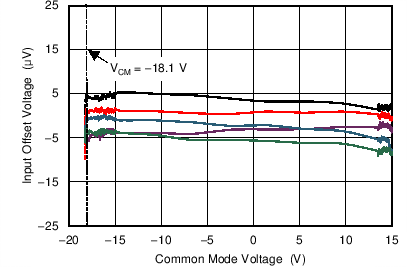

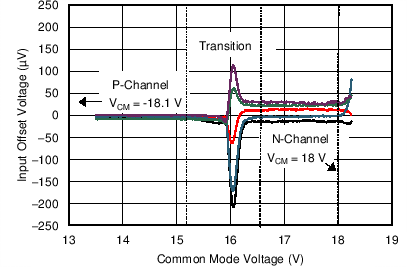

| オフセット電圧と同相電圧との関係 | 図 6-11、図 6-12 |

| オフセット電圧と電源電圧との関係 | 図 6-13 |

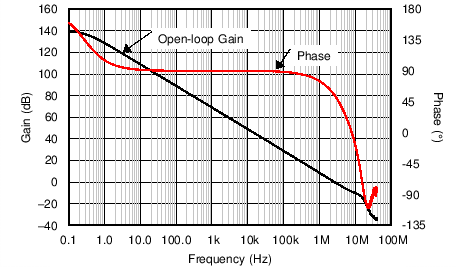

| 開ループのゲインおよび位相と周波数との関係 | 図 6-14 |

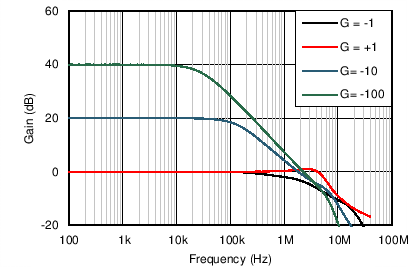

| 閉ループのゲインおよび位相と周波数との関係 | 図 6-15 |

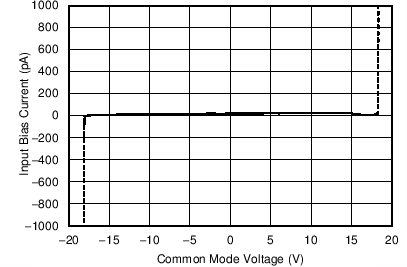

| 入力バイアス電流と同相電圧との関係 | 図 6-16 |

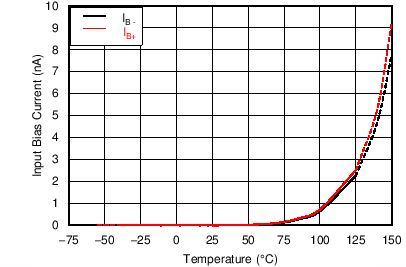

| 入力バイアス電流と温度との関係 | 図 6-17 |

| 出力電圧スイングと出力電流との関係 (最大供給能力) | 図 6-18、図 6-19 |

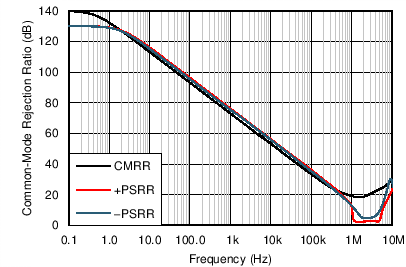

| CMRR および PSRR と周波数との関係 | 図 6-20 |

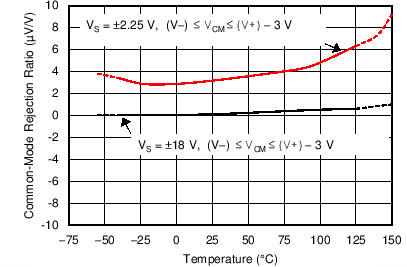

| CMRR と温度との関係 | 図 6-21 |

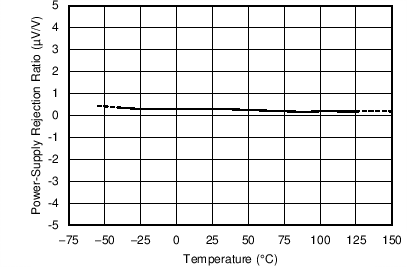

| PSRR と温度との関係 | 図 6-22 |

| 0.1Hz~10Hz のノイズ | 図 6-23 |

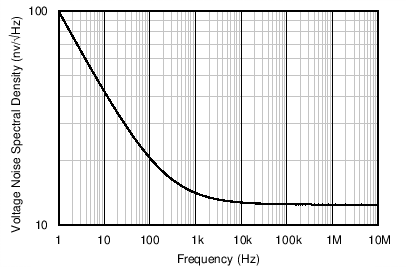

| 入力電圧ノイズのスペクトル密度と周波数との関係 | 図 6-24 |

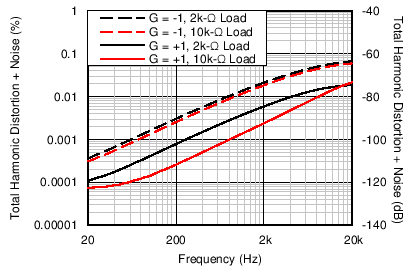

| THD+N 比と周波数との関係 | 図 6-25 |

| THD+N と出力振幅との関係 | 図 6-26 |

| 静止電流と電源電圧との関係 | 図 6-27 |

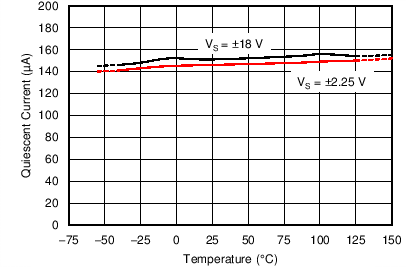

| 静止電流 対 温度 | 図 6-28 |

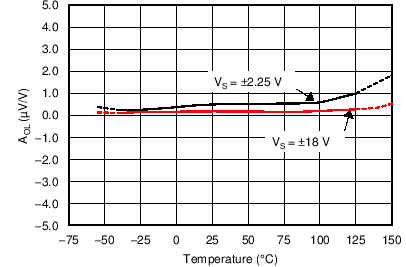

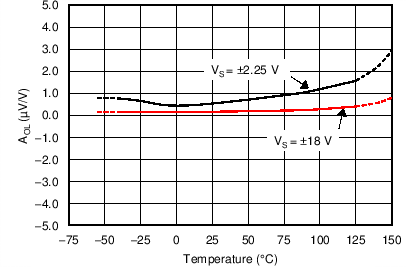

| 開ループのゲインと温度との関係 | 図 6-29、図 6-30 |

| 開ループの出力インピーダンスと周波数との関係 | 図 6-31 |

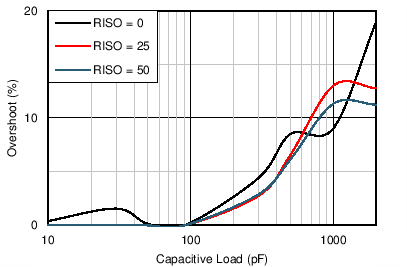

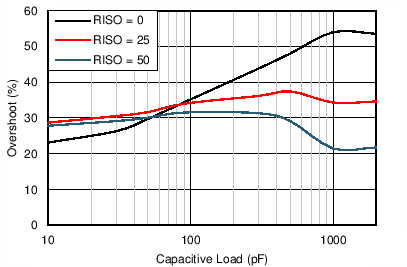

| 小信号オーバーシュートと容量性負荷との関係 (出力ステップ 100mV) | 図 6-32、図 6-33 |

| 位相反転なし | 図 6-34 |

| 過負荷からの回復 | 図 6-35 |

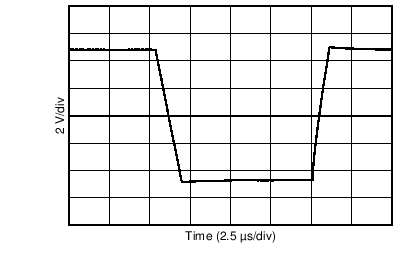

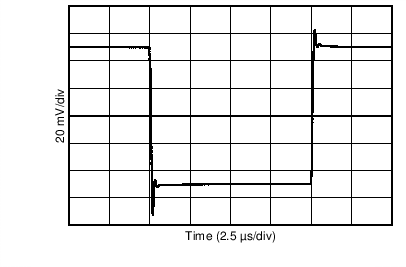

| 小信号ステップ応答 (100mV) | 図 6-36、図 6-37 |

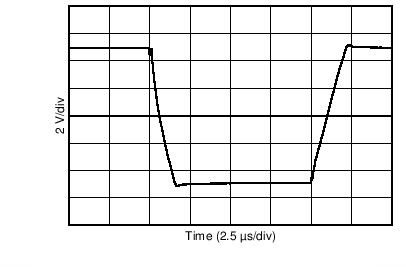

| 大信号ステップ応答 | 図 6-38、図 6-39 |

| セトリング・タイム | 図 6-40、図 6-41、図 6-42、図 6-43 |

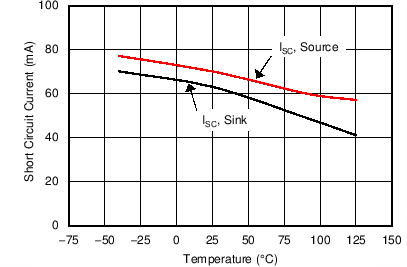

| 短絡電流と温度との関係 | 図 6-44 |

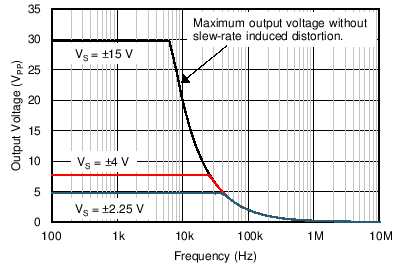

| 最大出力電圧と周波数との関係 | 図 6-45 |

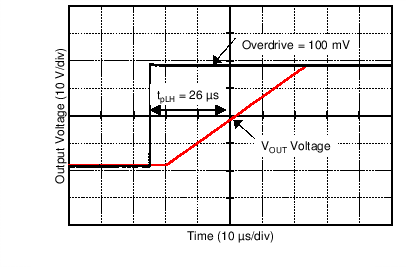

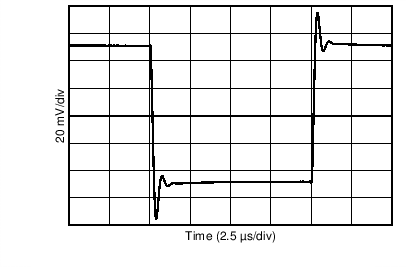

| 伝搬遅延の立ち上がりエッジ | 図 6-46 |

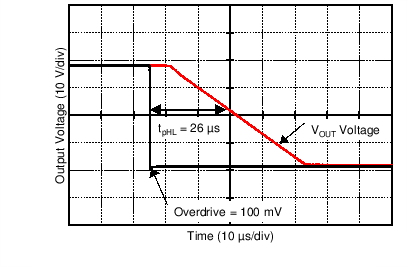

| 伝搬遅延の立ち下がりエッジ | 図 6-47 |

| TA = 25℃ |

| TA = 85℃ |

| TA = -25℃ |

| TA = -40℃~+125℃、SOIC パッケージ |

| 統計的分布 |

| 30 個の代表的なユニット |

| シンク |

出力電流との関係

| RL = 10kΩ |

周波数との関係

| G = -1、100mV の出力ステップ |

容量性負荷との関係

| VS = ±18V、G = -10V/V |

| G = -1、RL = 1kΩ、CL = 10pF |

| G = -1、RL = 1kΩ、CL = 10pF |

| ゲイン = 1、2V ステップ、立ち下がり、t = 0μs でステップを印加 |

| ゲイン = 1、5V ステップ、立ち下がり、t = 0μs でステップを印加 |

| TA = 125℃ |

| TA = 0℃ |

| TA = -40℃ |

| TA = 0℃~85℃、SOIC パッケージ |

| 4 個の代表的なユニット |

周波数との関係

同相電圧との関係

| ソース |

出力電流との関係

| RL = 2kΩ |

| G = 1、100mV の出力ステップ |

(出力ステップ 100mV)

| G = 1、CL = 10pF |

| G = 1、CL = 10pF |

| ゲイン = 1、2V ステップ、立ち上がり、t = 0μs でステップを印加 |

| ゲイン = 1、5V ステップ、立ち上がり、t = 0μs でステップを印加 |