JAJSC99B December 2012 – December 2015 TLC6C5912-Q1

PRODUCTION DATA.

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 ピン構成および機能

- 6 仕様

- 7 パラメータ測定情報

- 8 詳細説明

- 9 アプリケーションと実装

- 10電源に関する推奨事項

- 11レイアウト

- 12デバイスおよびドキュメントのサポート

- 13メカニカル、パッケージ、および注文情報

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

サーマルパッド・メカニカル・データ

- PW|20

発注情報

6 仕様

6.1 絶対最大定格

自由通気で動作温度範囲内の場合(特に記述のない限り)(1)| 最小 | 最大 | 単位 | |||

|---|---|---|---|---|---|

| VCC | ロジック電源電圧 | 8 | V | ||

| VI | ロジック入力電圧 | –0.3 | 8 | V | |

| VDS | 電力DMOSのドレイン-ソース間電圧 | 42 | V | ||

| 連続合計損失 | 熱特性についてを参照 | ||||

| 動作時周囲温度(上面) | 125 | °C | |||

| TJ | 動作時のジャンクション温度 | –40 | 150 | °C | |

| Tstg | 保管温度 | –55 | 165 | °C | |

(1) 絶対最大定格を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これはストレスの定格のみについて示してあり、このデータシートの推奨動作条件に示された値を超える状態で本製品が正常に動作することを暗黙的に示すものではありません。絶対最大定格の状態に長時間置くと、本製品の信頼性に影響を与えることがあります。

6.2 ESD定格

| 数値 | 単位 | |||||

|---|---|---|---|---|---|---|

| V(ESD) | Electrostatic discharge | Human body model (HBM), per AEC Q100-002(1) | ±2000 | V | ||

| Charged device model (CDM), per AEC Q100-011 | ±750 | |||||

(1) AEC Q100-002は、 ANSI/ESDA/JEDEC JS-001仕様に従ってHBMストレス試験を実施することを示します。

6.3 推奨動作条件

| 最小 | 最大 | 単位 | ||

|---|---|---|---|---|

| VCC | 電源電圧 | 3 | 5.5 | V |

| VIH | HIGHレベルの入力電圧 | 2.4 | V | |

| VIL | LOWレベルの入力電圧 | 0.7 | V | |

| tsu | セットアップ時間、SRCK↑前のSER IN HIGH | 15 | ns | |

| th | ホールド時間、SRCK↑後のSER IN HIGH | 15 | ns | |

| tw | パルス幅 | 40 | ns | |

| TC | 動作時のケース温度 | –40 | 125 | °C |

6.4 熱特性について

| THERMAL METRIC(1) | TLC6C5912-Q1 | UNIT | ||

|---|---|---|---|---|

| 20 PINS | ||||

| PW(TSSOP) | DW(SOIC) | |||

| RθJA | Junction-to-ambient thermal resistance | 114.8 | 81.2 | °C/W |

| RθJC(top) | Junction-to-case (top) thermal resistance | 44.1 | 45.4 | °C/W |

| RθJB | Junction-to-board thermal resistance | 61.3 | 49.1 | °C/W |

| ψJT | Junction-to-top characterization parameter | 4.7 | 17.5 | °C/W |

| ψJB | Junction-to-board characterization parameter | 60.8 | 48.6 | °C/W |

(1) 従来および新しい熱測定値の詳細については、『Semiconductor and IC Package Thermal Metrics (半導体およびICパッケージの熱測定値)』のアプリケーション・レポートを参照してください。

6.5 電気的特性

VCC= 5V、TC= 25℃ (特に記述のない限り)| パラメータ | 測定条件 | 最小 | 標準 | 最大 | UNIT | ||

|---|---|---|---|---|---|---|---|

| DRAIN0 to DRAIN11, drain-to-source voltage |

40 | V | |||||

| VOH | High-level output voltage, SER OUT |

IOH = –20 μA | VCC = 5 V | 4.9 | 4.99 | V | |

| IOH = –4 mA | 4.5 | 4.69 | |||||

| VOL | Low-level output voltage, SER OUT |

IOH = 20 μA | VCC = 5 V | 0.001 | 0.01 | V | |

| IOH = 4 mA | 0.25 | 0.4 | |||||

| IIH | High-level input current | VCC = 5 V, VI = VCC | 0.2 | μA | |||

| IIL | Low-level input current | VCC = 5 V, VI = 0 | –0.2 | μA | |||

| ICC | Logic supply current | VCC = 5 V, No clock signal |

All outputs off | 0.1 | 1 | μA | |

| All outputs on | 130 | 170 | |||||

| ICC(FRQ) | Logic supply current at frequency | fSRCK = 5 MHz, CL = 30 pF, all outputs on | 300 | µA | |||

| IDSX | Off-state drain current | VDS = 30 V, VCC = 5 V | 0.1 | μA | |||

| VDS = 30 V, TC = 125°C, VCC = 5 V | 0.15 | 0.3 | |||||

| rDS(on) | Static drain-source on-state resistance | ID = 20 mA, VCC = 5 V, TA = 25°C, single channel ON | 6 | 7.4 | 8.6 | Ω | |

| ID = 50 mA, VCC = 5 V, TA = 25°C, all channels ON | 6.7 | 8.9 | 9.6 | ||||

| ID = 20 mA, VCC = 3.3 V, TA = 25°C, single channel ON | 7.9 | 9.3 | 11.2 | ||||

| ID = 20 mA, VCC = 3.3 V, TA = 25°C, all channels ON | 8.7 | 10.6 | 12.3 | ||||

| ID = 20 mA, VCC = 5 V, TA = 125°C, single channel ON | 9.1 | 11.2 | 12.9 | ||||

| ID = 20 mA, VCC = 5 V, TA = 125°C, all channels ON | 10.3 | 13 | 14.5 | ||||

| ID = 20 mA, VCC = 3.3 V, TA = 125°C, single channel ON | 11.6 | 13.7 | 16.4 | ||||

| ID = 20 mA, VCC = 3.3 V, TA = 125°C, all channels ON | 12.8 | 15.6 | 18.2 | ||||

| TSHUTDOWN | Thermal shutdown trip point | 150 | 175 | 200 | °C | ||

| tHYS | Hysteresis | 15 | °C | ||||

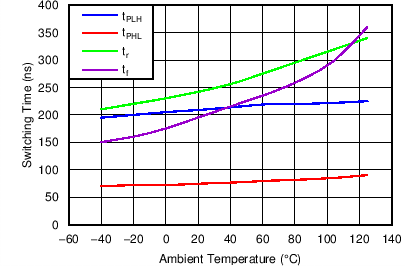

6.6 スイッチング特性

VCC = 5V、TJ = 25℃| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | 単位 | |

|---|---|---|---|---|---|---|

| tPLH | 伝搬遅延時間、Gからの出力がLOWレベルからHIGHレベルへ | CL = 30pF、ID = 48mA | 210 | ns | ||

| tPHL | 伝搬遅延時間、Gからの出力がHIGHレベルからLOWレベルへ | 75 | ns | |||

| tr | 立ち上がり時間、ドレイン出力 | 250 | ns | |||

| tf | 立ち下がり時間、ドレイン出力 | 200 | ns | |||

| tpd | 伝搬遅延時間、SRCK↓からSEROUTまで | CL = 30pF、ID = 48mA | 35 | ns | ||

| Tor | SEROUT立ち上がり時間(10%から90%へ) | CL = 30pF | 20 | ns | ||

| Tof | SEROUT立ち下がり時間(90%から10%へ) | CL = 30pF | 20 | ns | ||

| f(SRCK) | シリアルクロック周波数 | CL = 30pF、ID = 20mA | 10 | MHz | ||

| TSRCK_WH | SRCKパルス幅、HIGH | 30 | ns | |||

| TSRCK_WL | SRCKパルス幅、LOW | 30 | ns | |||

Figure 1. SER INからSER OUTへの波形

Figure 1. SER INからSER OUTへの波形

SER INからSER OUTへの波形を、Figure 1に示します。出力信号は、シフト・レジスタ・クロック(SRCK)の立ち下がりエッジで現れます。これは、SER OUTに位相インバータが存在するためです(機能ブロック図を参照)。その結果、データがSER INからSER OUTへ転送されるにはSRCKの11.5周期分の時間が必要です。

Figure 2. スイッチング時間と電圧波形

Figure 2. スイッチング時間と電圧波形

スイッチング時間と電圧波形を、Figure 2に示します。これらすべてのパラメータのテストは、Figure 12に示すテスト回路を使用して行われました。

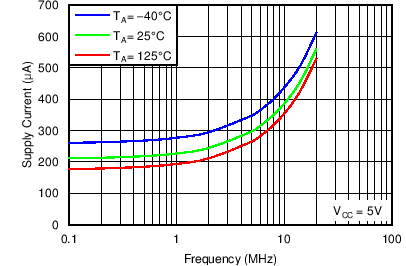

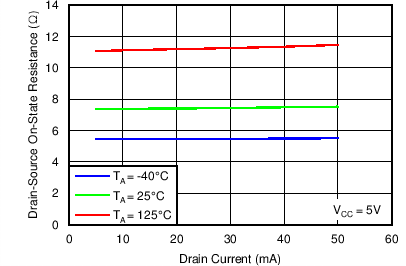

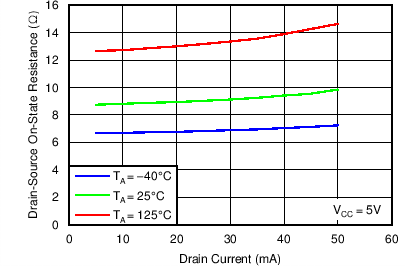

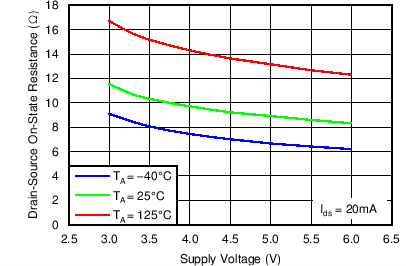

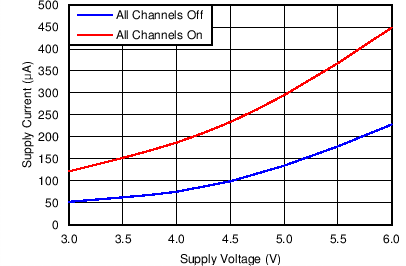

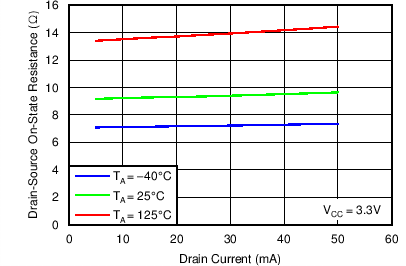

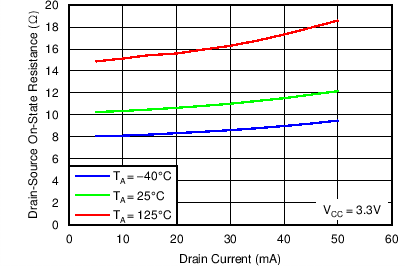

6.7 代表的特性

Figure 5およびFigure 6の条件: 単一チャネルがオン、Figure 7、Figure 8、Figure 9の条件: すべてのチャネルがオン。

ドレイン電流との関係

ドレイン電流との関係

ドレイン電流との関係

ドレイン電流との関係

ドレイン電流との関係