JAJSLY1G July 2013 – June 2021 TPS54561

PRODUCTION DATA

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3

Feature Description

- 7.3.1 Fixed Frequency PWM Control

- 7.3.2 Slope Compensation Output Current

- 7.3.3 Pulse Skip Eco-mode

- 7.3.4 Low Dropout Operation and Bootstrap Voltage (BOOT)

- 7.3.5 Error Amplifier

- 7.3.6 Adjusting the Output Voltage

- 7.3.7 Enable and Adjusting Undervoltage Lockout

- 7.3.8 Soft Start/Tracking Pin (SS/TR)

- 7.3.9 Sequencing

- 7.3.10 Constant Switching Frequency and Timing Resistor (RT/CLK) Pin)

- 7.3.11 Maximum Switching Frequency

- 7.3.12 Synchronization to RT/CLK Pin

- 7.3.13 Accurate Current Limit Operation

- 7.3.14 Power Good (PWRGD Pin)

- 7.3.15 Overvoltage Protection

- 7.3.16 Thermal Shutdown

- 7.3.17 Small Signal Model for Loop Response

- 7.3.18 Simple Small Signal Model for Peak Current Mode Control

- 7.3.19 Small Signal Model for Frequency Compensation

- 7.4 Device Functional Modes

-

8 Application and Implementation

- 8.1 Application Information

- 8.2

Typical Applications

- 8.2.1

Buck Converter for 7-V to 60-V Input to 5-V at 5-A Output

- 8.2.1.1 Design Requirements

- 8.2.1.2

Detailed Design Procedure

- 8.2.1.2.1 Custom Design with WEBENCH® Tools

- 8.2.1.2.2 Selecting the Switching Frequency

- 8.2.1.2.3 Output Inductor Selection (LO)

- 8.2.1.2.4 Output Capacitor

- 8.2.1.2.5 Catch Diode

- 8.2.1.2.6 Input Capacitor

- 8.2.1.2.7 Slow Start Capacitor

- 8.2.1.2.8 Bootstrap Capacitor Selection

- 8.2.1.2.9 Undervoltage Lockout Set Point

- 8.2.1.2.10 Output Voltage and Feedback Resistors Selection

- 8.2.1.2.11 Compensation

- 8.2.1.2.12 Power Dissipation Estimate

- 8.2.1.2.13 Safe Operating Area

- 8.2.1.2.14 Discontinuous Conduction Mode and Eco-mode Boundary

- 8.2.1.3 Application Curves

- 8.2.2 Inverting Buck-Boost Topology for Positive Input to Negative Output

- 8.2.3 Split-Rail Topology for Positive Input to Negative and Positive Output

- 8.2.1

Buck Converter for 7-V to 60-V Input to 5-V at 5-A Output

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

3 概要

TPS54561 は、ハイサイド MOSFET を内蔵した 60V、5A の降圧レギュレータです。ISO 7637 に準拠し、最大 65V の負荷ダンプ・パルスに耐えることができます。電流モード制御により外部補償が単純化され、柔軟な部品選択が可能になります。低リップルのパルス・スキップ・モードを使用すると、無負荷時の消費電流を 152μA まで低減できます。イネーブル・ピンを Low にすると、シャットダウン時消費電流が 2μA まで減少します。

低電圧誤動作防止は内部で 4.3V に設定されていますが、イネーブル・ピンに分割抵抗を外付けしてさらに高い電圧に設定することができます。出力電圧のスタートアップ・ランプは、ソフト・スタート・ピンにより制御されます。このピンはシーケンス処理やトラッキング用に構成することも可能です。オープン・ドレイン出力のパワー・グッド信号は、出力電圧が公称電圧の 93%~106% の範囲内であることを示します。

スイッチング周波数の調整可能範囲が広いため、効率と外付け部品サイズのどちらにも最適化できます。サイクル単位の電流制限、周波数フォールドバック、サーマル・シャットダウン機能によって、過負荷状態時に内部部品および外部部品を保護します。

TPS54561 は 10 ピン 4mm x 4mm の WSON パッケージで供給されます。

製品情報

| 部品番号 | パッケージ(1) | 本体サイズ (公称) |

|---|---|---|

| TPS54561 | WSON (10) | 4.00mm × 4.00mm |

(1) 利用可能なすべてのパッケージについては、このデータシートの末尾にある注文情報を参照してください。

概略回路図

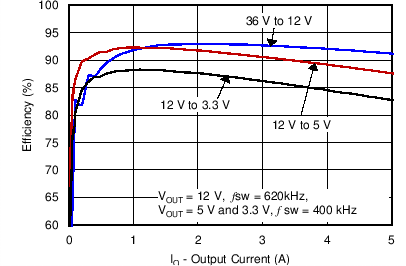

概略回路図 効率と負荷電流との関係

効率と負荷電流との関係