JAJSC12D October 2013 – April 2018 TPS7B67-Q1

PRODUCTION DATA.

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 概要(続き)

- 6 Device Comparison

- 7 Pin Configuration and Functions

- 8 Specifications

- 9 Detailed Description

- 10Application and Implementation

- 11Power Supply Recommendations

- 12Layout

- 13デバイスおよびドキュメントのサポート

- 14メカニカル、パッケージ、および注文情報

11.1.2 TPS7B67xx-Q1 Dropout During Startup

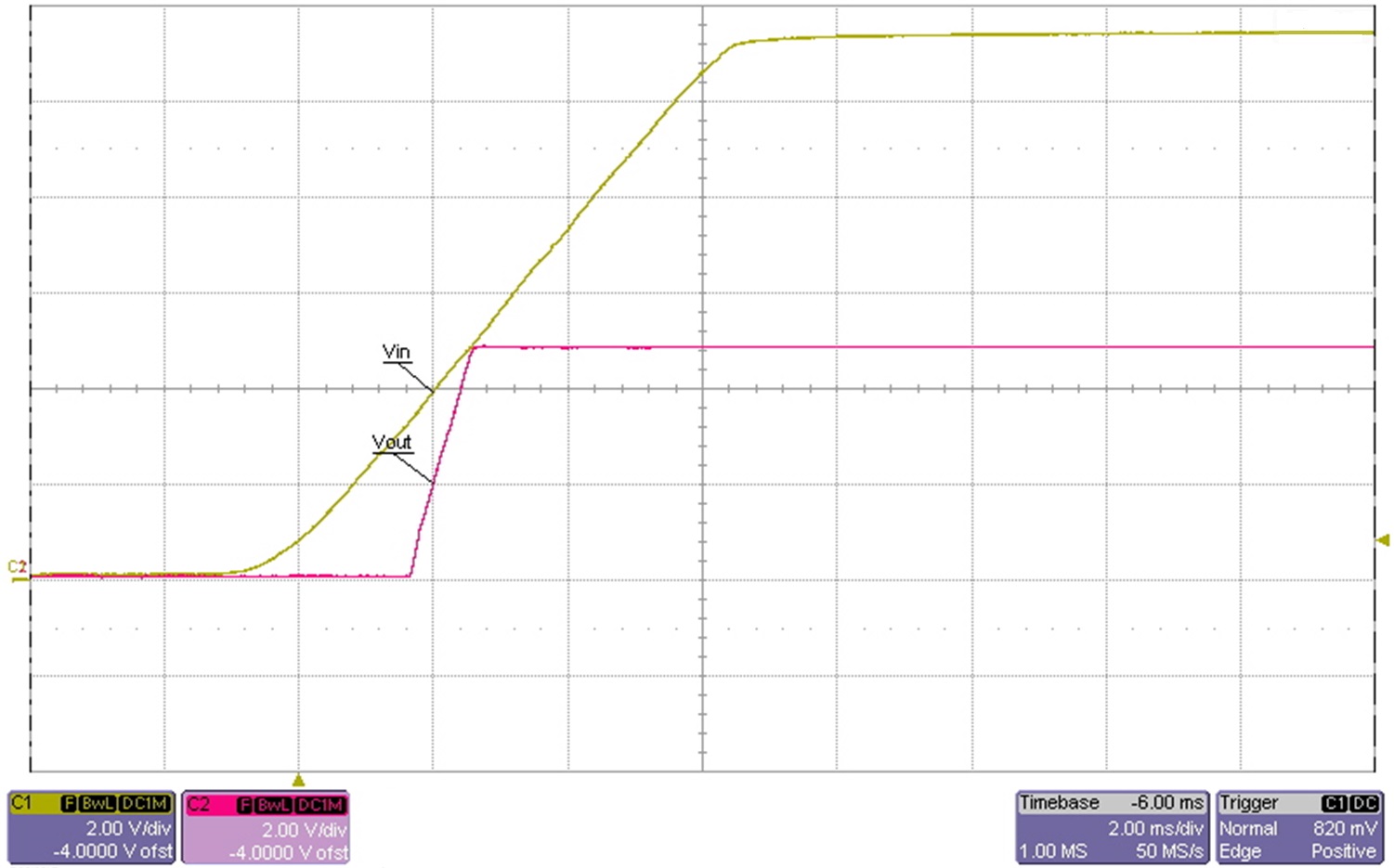

The TPS7B67xx-Q1 does not overshoot significantly if the LDO is enabled after the input voltage is already above VOUT(NOM) plus VDO. Furthermore, startup performance is not affected as long as the input voltage transitions from VUVLO+(IN) to VOUT(NOM) plus VDO in less than 1 millisecond. Approximately 1 millisecond is required for the TPS7B67xx-Q1 reference voltage to reach its steady state value, so input voltage startup transitions that are less than 1 millisecond do not force the device into dropout. One example that does not overshoot is a 5-V output voltage with full load (full load has the highest dropout), where the input voltage ramps steadily from 0 V to 5.45 V in less than 3 milliseconds. Overshoot does not occur in this case because the input reaches VOUT plus VDO before the reference has come up all the way to its final value, keeping the LDO out of dropout. Figure 26 depicts an example of a startup ramp rate that is just fast enough to keep a device with a 5-V output voltage from going into dropout.

Figure 26. Startup Ramp Speed to Avoid Dropout

Figure 26. Startup Ramp Speed to Avoid Dropout