JAJSC47I June 2011 – October 2019 LM5113

PRODUCTION DATA.

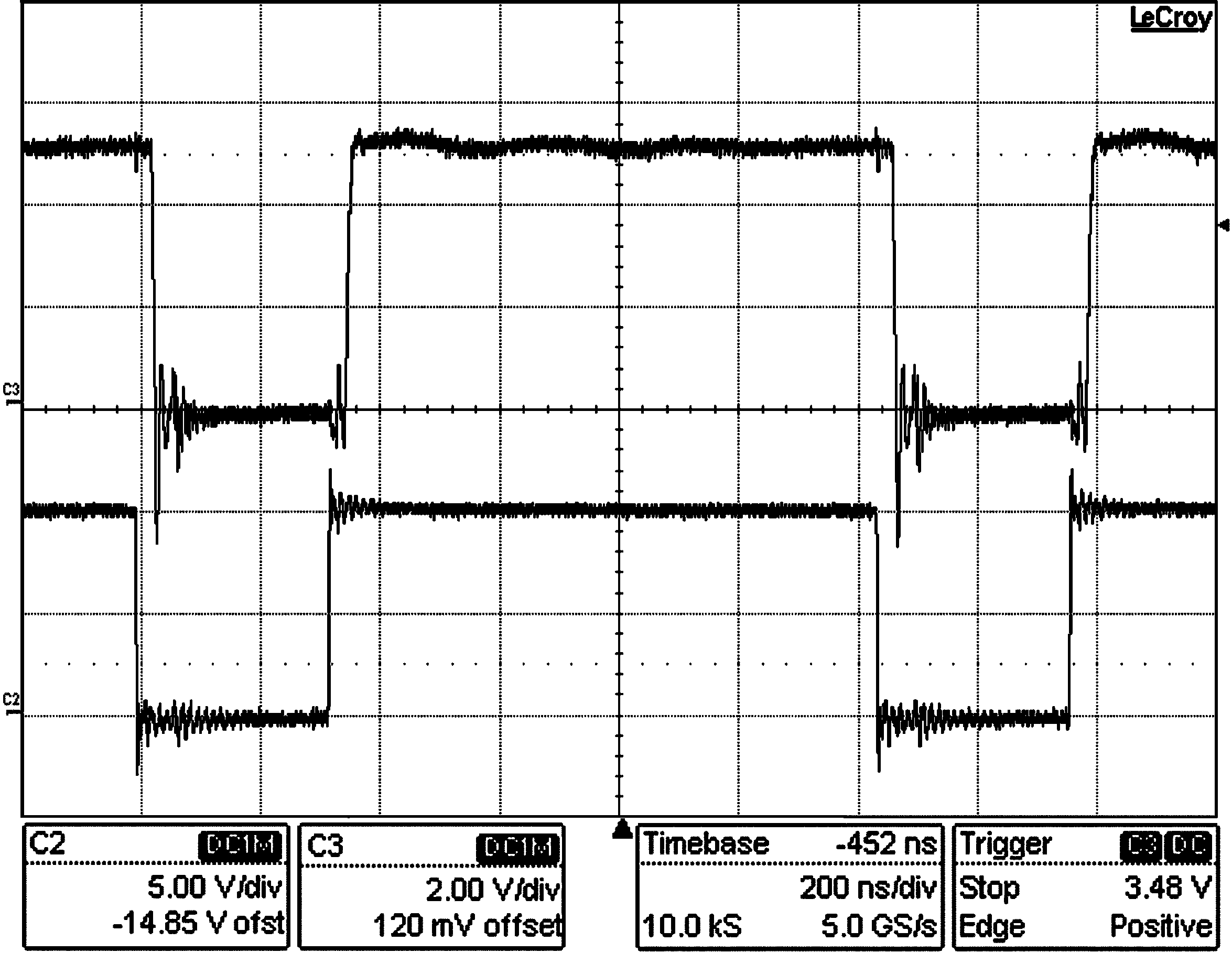

9.2.3 Application Curves

Conditions:

Input Voltage = 48 V DC, Load Current = 5 A

Traces:

Top Trace: Gate of Low-Side eGaN FET, Volt/div = 2 V

Bottom Trace: LI of LM5113, Volt/div = 5 V

Bandwidth Limit = 600 MHz

Horizontal Resolution = 0.2 µs/div

Figure 22. Low-Side Driver Input and Output Input Voltage = 48 V DC, Load Current = 5 A

Traces:

Top Trace: Gate of Low-Side eGaN FET, Volt/div = 2 V

Bottom Trace: LI of LM5113, Volt/div = 5 V

Bandwidth Limit = 600 MHz

Horizontal Resolution = 0.2 µs/div

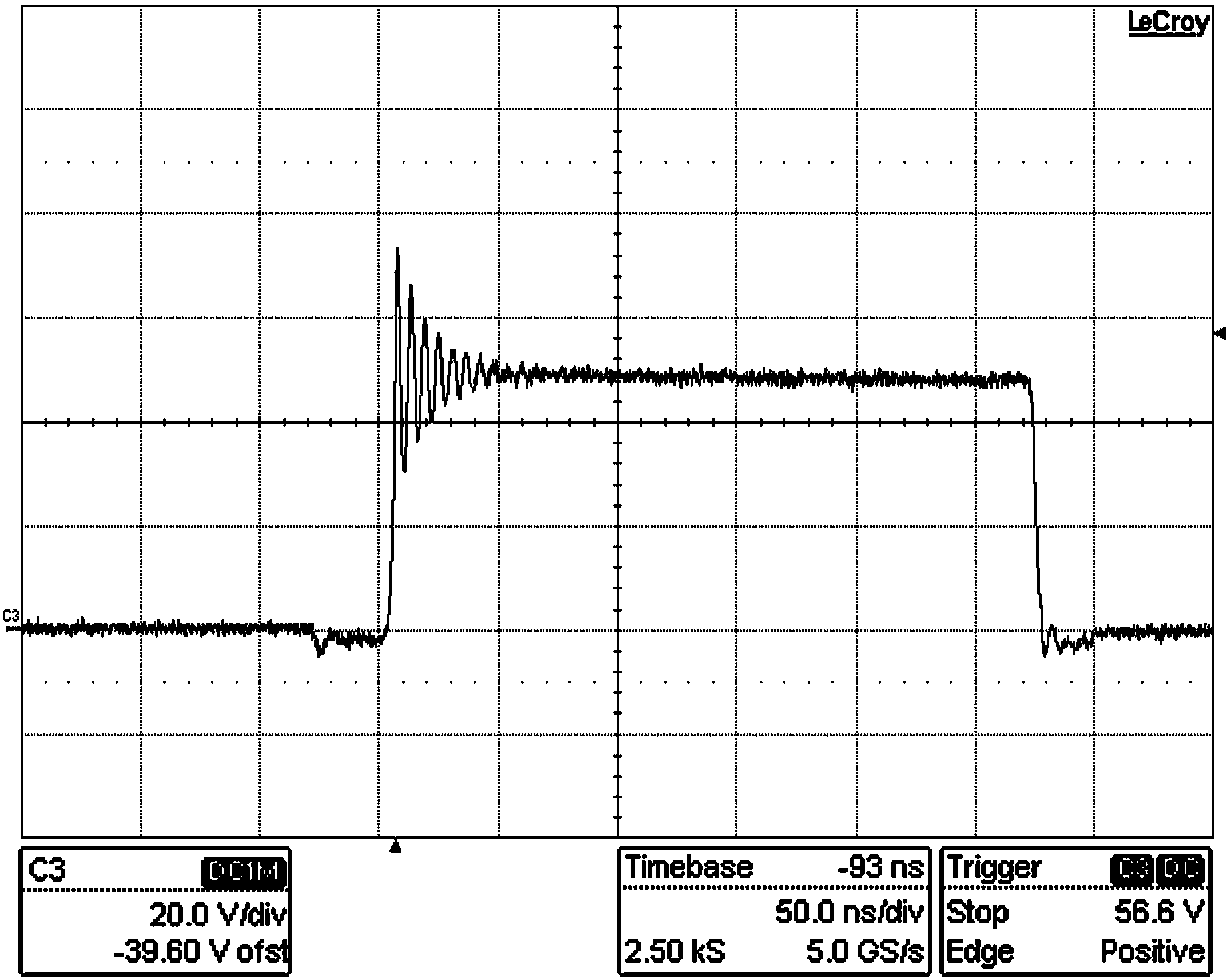

Conditions:

Input Voltage = 48 V DC,

Load Current = 10 A

Traces:

Trace: Switch-Node Voltage, Volts/div = 20 V

Bandwidth Limit = 600 MHz

Horizontal Resolution = 50 ns/div

Figure 23. Switch-Node Voltage Input Voltage = 48 V DC,

Load Current = 10 A

Traces:

Trace: Switch-Node Voltage, Volts/div = 20 V

Bandwidth Limit = 600 MHz

Horizontal Resolution = 50 ns/div